Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Страница 1 из 1 • Поделиться

Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

1

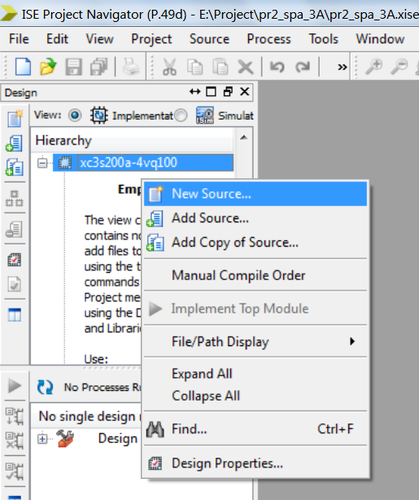

Решил, что пора изучать VHDL и освоить ПЛИС, например фирмы Xilinx.

В этой теме, будет отображаться весь процесс изучения, не знаю чем он закончится, так как предыдущая моя попытка, ничем положительным так и не закончилась. Поэтому буду тут выкладывать и теорию, своего рода конспект нескольких источников. Так как уже убедился, что иногда в одной книге, понятно и доходчиво раскрывается какой нибудь аспект, но совершенно непонятно, другой. А некоторые вещи понятны становятся только прочитав какую нибудь статью из журнала.

Поэтому, можно считать, что эта тема своего рода, мой рабочий конспект, где я постараюсь собрать побольше информации, законспектировать её, в понятной для новичка форме, то есть меня и может ещё кому нибудь пригодится, и попытаться перейти к практике, если теория станет более или менее понятной.

Итак в путь, больше первый пост засирать не буду, он может ещё пригодиться...

_________________________________________________________________________

Обзор современных ПЛИС и САПР. 2006г.

Особенности архитектуры нового поколения ПЛИС с архитектурой

FPGA фирмы Xilinx, Artix-7, Kintex-7, Virtex-7. 2010г.

__________________________________________________

Практический курс сквозного проектирования цифровых

устройств на основе ПЛИС фирмы Xilinx

Разработка VHDL-описаний цифровых устройств, проектируемых на основе ПЛИС фирмы Xilinx, с использованием шаблонов САПР ISE Design Suite. Часть 1-11, 17-27.

Первое знакомство с ПЛИС Xilinx c сайта radiokot.ru

Разработка устройств питания для ПЛИС фирмы Xilinx на основе интегральных стабилизаторов напряжения, выпускаемых компанией National Semiconductor. Часть 1 - 3

Новый инструментальный комплект от компании Avnet на основе ПЛИС FPGA семейства Spartan-3A фирмы Xilinx

Новый инструментальный комплект Spartan-3A Starter Kit для практического освоения методов проектирования и отладки цифровых устройств с аппаратной и программной реализацией операций, реализуемых на основе ПЛИС семейств FPGA фирмы Xilinx

Новые возможности САПР Xilinx версии 12.3

Создание проекта в среде Xilinx PlanAhead 12.4 входящего в состав Xilinx ISE Design Suite 12.4

Инструменты автоматизации процессов моделирования и конфигурирования ПЛИС в САПР ISE

__________________________________________________

Система команд микропроцессорных ядер PicoBlaze

проектируемых на ПЛИС Spartan-II Spartan-IIE Virtex Virtex-E

Пример сквоздного проектирования 8-разрядной микропроцессорной системы на базе ядра семейства PicoBlaze, реализуемой на основе ПЛИС фирмы Xilinx. Часть 1-3

Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы XILINX.

В. Ю. Зотов. 2006г.

MicroBlaze - семейство 32-разрядных микропроцессорных ядер,

реализуемых на основе ПЛИС фирмы Xilinx

Система команд микропроцессорного ядра MicroBlaze

Создание проекта микропроцессорной системы на основе ядра MicroBlaze реализуемой в ПЛИС семейств FPGA фиры Xilinx

Построение систем на кристалле с подчинённым процессорным ядром MicroBlaze на ПЛИС фирмы Xilinx

В этой теме, будет отображаться весь процесс изучения, не знаю чем он закончится, так как предыдущая моя попытка, ничем положительным так и не закончилась. Поэтому буду тут выкладывать и теорию, своего рода конспект нескольких источников. Так как уже убедился, что иногда в одной книге, понятно и доходчиво раскрывается какой нибудь аспект, но совершенно непонятно, другой. А некоторые вещи понятны становятся только прочитав какую нибудь статью из журнала.

Поэтому, можно считать, что эта тема своего рода, мой рабочий конспект, где я постараюсь собрать побольше информации, законспектировать её, в понятной для новичка форме, то есть меня и может ещё кому нибудь пригодится, и попытаться перейти к практике, если теория станет более или менее понятной.

Итак в путь, больше первый пост засирать не буду, он может ещё пригодиться...

_________________________________________________________________________

Обзор современных ПЛИС и САПР. 2006г.

Особенности архитектуры нового поколения ПЛИС с архитектурой

FPGA фирмы Xilinx, Artix-7, Kintex-7, Virtex-7. 2010г.

__________________________________________________

Практический курс сквозного проектирования цифровых

устройств на основе ПЛИС фирмы Xilinx

Разработка VHDL-описаний цифровых устройств, проектируемых на основе ПЛИС фирмы Xilinx, с использованием шаблонов САПР ISE Design Suite. Часть 1-11, 17-27.

Первое знакомство с ПЛИС Xilinx c сайта radiokot.ru

Разработка устройств питания для ПЛИС фирмы Xilinx на основе интегральных стабилизаторов напряжения, выпускаемых компанией National Semiconductor. Часть 1 - 3

Новый инструментальный комплект от компании Avnet на основе ПЛИС FPGA семейства Spartan-3A фирмы Xilinx

Новый инструментальный комплект Spartan-3A Starter Kit для практического освоения методов проектирования и отладки цифровых устройств с аппаратной и программной реализацией операций, реализуемых на основе ПЛИС семейств FPGA фирмы Xilinx

Новые возможности САПР Xilinx версии 12.3

Создание проекта в среде Xilinx PlanAhead 12.4 входящего в состав Xilinx ISE Design Suite 12.4

Инструменты автоматизации процессов моделирования и конфигурирования ПЛИС в САПР ISE

__________________________________________________

Система команд микропроцессорных ядер PicoBlaze

проектируемых на ПЛИС Spartan-II Spartan-IIE Virtex Virtex-E

Пример сквоздного проектирования 8-разрядной микропроцессорной системы на базе ядра семейства PicoBlaze, реализуемой на основе ПЛИС фирмы Xilinx. Часть 1-3

Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы XILINX.

В. Ю. Зотов. 2006г.

MicroBlaze - семейство 32-разрядных микропроцессорных ядер,

реализуемых на основе ПЛИС фирмы Xilinx

Система команд микропроцессорного ядра MicroBlaze

Создание проекта микропроцессорной системы на основе ядра MicroBlaze реализуемой в ПЛИС семейств FPGA фиры Xilinx

Построение систем на кристалле с подчинённым процессорным ядром MicroBlaze на ПЛИС фирмы Xilinx

Последний раз редактировалось: Viktor2312 (Чт Ноя 05 2015, 01:24), всего редактировалось 10 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Полезная информация.

Полезная информация.

2

Для начала выложу немного полезной информации, которая возможно в будущем пригодится нам для изучения:

_______________________________________________________

Справочная система по VHDL, в формате html Скачать

_______________________________________________________

Ключевые слова VHDL, в формате html Скачать

_______________________________________________________

Авдеев Н. А., Бибило П. Н. Пакет NUMERIC_STD языка VHDL.

Информационные технологии. - 2005. - №9

Скачать

_______________________________________________________

Моделирование цифровых и микропроцессорных систем.

Язык VHDL. Дьяков.

Скачать

_______________________________________________________

Авдеев Н. А. Бибило П. Н. Реализация VHDL-функций пакета

NUMERIC_STD логическими схемами. // Информационные

технологии. - 2006г. - №1. - стр. 9 - 18.

Скачать

_______________________________________________________

В. Стешенко. Языки описания аппаратуры: синтезируемое

подмножество VHDL.

Скачать

_______________________________________________________

_______________________________________________________

Справочная система по VHDL, в формате html Скачать

_______________________________________________________

Ключевые слова VHDL, в формате html Скачать

_______________________________________________________

Авдеев Н. А., Бибило П. Н. Пакет NUMERIC_STD языка VHDL.

Информационные технологии. - 2005. - №9

Скачать

_______________________________________________________

Моделирование цифровых и микропроцессорных систем.

Язык VHDL. Дьяков.

Скачать

_______________________________________________________

Авдеев Н. А. Бибило П. Н. Реализация VHDL-функций пакета

NUMERIC_STD логическими схемами. // Информационные

технологии. - 2006г. - №1. - стр. 9 - 18.

Скачать

_______________________________________________________

В. Стешенко. Языки описания аппаратуры: синтезируемое

подмножество VHDL.

Скачать

_______________________________________________________

Последний раз редактировалось: Viktor2312 (Пт Окт 03 2014, 19:22), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

3

А также, немного литературы, из которой мы также будем черпать полезную информацию:

Основы языка VHDL. Бибило П. Н. (2002г.) Скачать

Описывается применение языка VHDL на алгоритмическом и логическом уровнях проектирования цифровых систем. Язык VHDL является международным стандартом в системах автоматизации проектирования и предназначен для спецификации, моделирования и синтеза цифровых систем на основе заказных и программируемых пользователями сверхбольших интегральных схем.

Книга предназначена для первоначального ознакомления с языком VHDL и может быть полезна студентам, аспирантам и специалистам, занимающимся разработкой электронной аппаратуры с помощью средств САПР.

Проектирование цифровых систем на VHDL. Е. А. Суворова, Ю. Е. Шейнин (2003г.) Скачать

В книге рассматривается язык VHDL - стандартизованный язык высокого уровня для описания аппаратуры - и его применение для проектирования систем на СБИС.

Подробно, в полном объеме приводится язык VHDL, базовые конструкции моделей на этом языке, методы его применения, особенности VHDL для моделирования и для синтеза цифровых систем.

Рассматриваются основы проектирования систем на СБИС, уровни и этапы проектирования СБИС и Систем-на-кристалле, использование VHDL в процессе проектирования цифровых систем.

Изложение иллюстрируется примерами моделей устройств на языке VHDL. Рассматривается шина АВМА АНВ, широко применяемая в Системах-на-кристалле, оцениваются ее характеристики. Приводится описание практической работы в популярных САПР - OrCAD Express и Xilinx Foundation Express - при проектировании на языке VHDL цифровых СБИС и Систем-на-кристалле.

Языки VHDL и VERILOG в проектировании цифровой аппаратуры. Поляков (2003г.)

Скачать pdf

Скачать djvu

Книга посвящена проектированию цифровых систем с помощью высокоуровневых языков описания аппаратуры (Hardware Description Language - HDL) - Verilog и VHDL. Эти языки являются международным стандартом и используются как системами анализа (моделирование), так и системами синтеза цифровой аппаратуры. С единых позиций изложены основные концепции этих языков. Даны рекомендации по стилю кодирования, синтезабельности и верификации HDL-описаний проектируемых систем.

Приведены примеры синтезабельных описаний узлов и устройств и организации функциональных тестов.

В приложение вынесены справочные данные по языкам VHDL и Verilog.

Автор предполагает, что читатель знаком с основами программирования и основами проектирования цифровых устройств.

VHDL для проектирования вычислительных устройств. Сергиенко А. М. (2003г.)

Скачать pdf

Скачать djvu

Приведены основы программирования на языке VHDL и особенности проектирования вычислительных устройств с помощью VHDL, ориентированных на реализацию в программируемых логических интегральных схемах. Рассмотрены методы разработки специализированных конвейерных вычислительных устройств и предложена методика их проектирования, основанная на VHDL. Приведено описание на VHDL проекта RISC-микропроцессора и цикл экспериментальных работ на его основе.

Для студентов, аспирантов, преподавателей вузов и специалистов в области электроники, измерительной и вычислительной техники, связи.

Проектирование цифровых устройств на основе ПЛИС фирмы XILINX в САПР WebPACK ISE. Зотов В.Ю. (2003г.)

Скачать pdf

Скачать djvu

Книга предназначена для самостоятельного изучения методики проектирования специализированных цифровых устройств на базе программируемых логических интегральных схем (ПЛИС) фирмы XilinxR, выполняемого в рамках свободно распространяемого пакета WebPACKT ISET версии 5.1. Применение САПР WebPACK ISE позволяет реализовать полный цикл сквозного проектирования устройства на рабочем столе разработчика, включая программирование кристалла, без материальных затрат на программное обеспечение. Рассмотрен процесс создания исходного описания разрабатываемого устройства в схемотехнической и алгоритмической форме. Краткий справочник по унифицированным библиотекам схемотехнического редактора, включенный в виде приложения, позволяет разработчикам использовать наиболее привычный способ представления проекта. Обзор шаблонов VHDL облегчает изучение этого языка описания аппаратуры и ускоряет создание законченных VHDL-описаний проектов. Приведено описание системы HDL-моделирования ModelSimT корпорации Model TechnologyR (одного из подразделений компании MentorGraphicsR) и ее применения в процессе функциональной и временной верификации разрабатываемого устройства.

Материал, изложенный в книге, также может быть использован в процессе самостоятельного освоения системы проектирования FoundationT ISE фирмы Xilinx.

Для инженерно-технических работников, может быть полезна студентам и аспирантам, специализирующимся в области разработки цифровых систем.

Разработка цифровых устройств на основе ПЛИС Xilinx с применением языка VHDL.

И. Е. Тарасов (2005г.) Скачать - да да, это теперь не ссылка, скачать нельзя, скажите спасибо государству и Яндексу, файл они заблокировали, так что ищите в другом месте и так скорее всего будет со всем. Но...

Но информация должна быть доступна всем, а посему:

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Содержит начальные сведения о ПЛИС фирмы Xilinx, маршрутах проектирования цифровых устройств на базе ПЛИС, и языке описания аппаратуры VHDL. Рассмотрены технические характеристики современных ПЛИС Xilinx и возможности САПР, предназначенных для их программирования. Даются начальные сведения о языке описания аппаратуры VHDL, ориентированные на его использование в САПР фирмы Xilinx. Книга ориентирована на читателя, не имеющего опыт работы с ПЛИС.

Для инженерно-технических работников, студентов и аспирантов, занимающихся проектированием цифровых устройств.

VHDL: Эффективное использование при проектировании цифровых систем. Бибило П. Н. (2006г.) Скачать

Рассматриваются наиболее распространенные на практике пакеты STD_LOGIC_1164, NUMERIC_STD, EXEMPLAR_1164, TEXTIO, STD_LOGIC_TEXTIO, VITAL языка VHDL и их использование при проектировании цифровых систем на элементной базе сверхбольших интегральных схем, в том числе базовых матричных кристаллов. Приведены примеры и маршруты проектирования с использованием системы ModelSim моделирования и системы LeonardoSpectrum синтеза логических схем по алгоритмическим VHDL-описаниям цифровых систем. Предназначена для специалистов, занимающихся проектированием цифровых систем и знакомых с основными элементами языка VHDL, может быть полезна студентам и аспирантам, изучающим язык VHDL и его применение в системах автоматизированного проектирования.

Основы языка VHDL. 3-е издание. Бибило П. Н. (2007г.) Скачать

Описывается применение языка VHDL на алгоритмическом и логическом уровнях проектирования цифровых систем. Язык VHDL является международным стандартом в системах автоматизации проектирования и предназначен для спецификации, моделирования и синтеза цифровых систем на основе заказных и программируемых пользователями сверхбольших интегральных схем.

Книга предназначена для первоначального ознакомления с языком VHDL и может быть полезна студентам, аспирантам и специалистам, занимающимся разработкой электронной аппаратуры с помощью средств САПР.

Основы языка VHDL. Бибило П. Н. (2002г.) Скачать

Описывается применение языка VHDL на алгоритмическом и логическом уровнях проектирования цифровых систем. Язык VHDL является международным стандартом в системах автоматизации проектирования и предназначен для спецификации, моделирования и синтеза цифровых систем на основе заказных и программируемых пользователями сверхбольших интегральных схем.

Книга предназначена для первоначального ознакомления с языком VHDL и может быть полезна студентам, аспирантам и специалистам, занимающимся разработкой электронной аппаратуры с помощью средств САПР.

Проектирование цифровых систем на VHDL. Е. А. Суворова, Ю. Е. Шейнин (2003г.) Скачать

В книге рассматривается язык VHDL - стандартизованный язык высокого уровня для описания аппаратуры - и его применение для проектирования систем на СБИС.

Подробно, в полном объеме приводится язык VHDL, базовые конструкции моделей на этом языке, методы его применения, особенности VHDL для моделирования и для синтеза цифровых систем.

Рассматриваются основы проектирования систем на СБИС, уровни и этапы проектирования СБИС и Систем-на-кристалле, использование VHDL в процессе проектирования цифровых систем.

Изложение иллюстрируется примерами моделей устройств на языке VHDL. Рассматривается шина АВМА АНВ, широко применяемая в Системах-на-кристалле, оцениваются ее характеристики. Приводится описание практической работы в популярных САПР - OrCAD Express и Xilinx Foundation Express - при проектировании на языке VHDL цифровых СБИС и Систем-на-кристалле.

Языки VHDL и VERILOG в проектировании цифровой аппаратуры. Поляков (2003г.)

Скачать pdf

Скачать djvu

Книга посвящена проектированию цифровых систем с помощью высокоуровневых языков описания аппаратуры (Hardware Description Language - HDL) - Verilog и VHDL. Эти языки являются международным стандартом и используются как системами анализа (моделирование), так и системами синтеза цифровой аппаратуры. С единых позиций изложены основные концепции этих языков. Даны рекомендации по стилю кодирования, синтезабельности и верификации HDL-описаний проектируемых систем.

Приведены примеры синтезабельных описаний узлов и устройств и организации функциональных тестов.

В приложение вынесены справочные данные по языкам VHDL и Verilog.

Автор предполагает, что читатель знаком с основами программирования и основами проектирования цифровых устройств.

VHDL для проектирования вычислительных устройств. Сергиенко А. М. (2003г.)

Скачать pdf

Скачать djvu

Приведены основы программирования на языке VHDL и особенности проектирования вычислительных устройств с помощью VHDL, ориентированных на реализацию в программируемых логических интегральных схемах. Рассмотрены методы разработки специализированных конвейерных вычислительных устройств и предложена методика их проектирования, основанная на VHDL. Приведено описание на VHDL проекта RISC-микропроцессора и цикл экспериментальных работ на его основе.

Для студентов, аспирантов, преподавателей вузов и специалистов в области электроники, измерительной и вычислительной техники, связи.

Проектирование цифровых устройств на основе ПЛИС фирмы XILINX в САПР WebPACK ISE. Зотов В.Ю. (2003г.)

Скачать pdf

Скачать djvu

Книга предназначена для самостоятельного изучения методики проектирования специализированных цифровых устройств на базе программируемых логических интегральных схем (ПЛИС) фирмы XilinxR, выполняемого в рамках свободно распространяемого пакета WebPACKT ISET версии 5.1. Применение САПР WebPACK ISE позволяет реализовать полный цикл сквозного проектирования устройства на рабочем столе разработчика, включая программирование кристалла, без материальных затрат на программное обеспечение. Рассмотрен процесс создания исходного описания разрабатываемого устройства в схемотехнической и алгоритмической форме. Краткий справочник по унифицированным библиотекам схемотехнического редактора, включенный в виде приложения, позволяет разработчикам использовать наиболее привычный способ представления проекта. Обзор шаблонов VHDL облегчает изучение этого языка описания аппаратуры и ускоряет создание законченных VHDL-описаний проектов. Приведено описание системы HDL-моделирования ModelSimT корпорации Model TechnologyR (одного из подразделений компании MentorGraphicsR) и ее применения в процессе функциональной и временной верификации разрабатываемого устройства.

Материал, изложенный в книге, также может быть использован в процессе самостоятельного освоения системы проектирования FoundationT ISE фирмы Xilinx.

Для инженерно-технических работников, может быть полезна студентам и аспирантам, специализирующимся в области разработки цифровых систем.

Разработка цифровых устройств на основе ПЛИС Xilinx с применением языка VHDL.

И. Е. Тарасов (2005г.) Скачать - да да, это теперь не ссылка, скачать нельзя, скажите спасибо государству и Яндексу, файл они заблокировали, так что ищите в другом месте и так скорее всего будет со всем. Но...

Но информация должна быть доступна всем, а посему:

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Скачать (10,8 Мб)

Содержит начальные сведения о ПЛИС фирмы Xilinx, маршрутах проектирования цифровых устройств на базе ПЛИС, и языке описания аппаратуры VHDL. Рассмотрены технические характеристики современных ПЛИС Xilinx и возможности САПР, предназначенных для их программирования. Даются начальные сведения о языке описания аппаратуры VHDL, ориентированные на его использование в САПР фирмы Xilinx. Книга ориентирована на читателя, не имеющего опыт работы с ПЛИС.

Для инженерно-технических работников, студентов и аспирантов, занимающихся проектированием цифровых устройств.

VHDL: Эффективное использование при проектировании цифровых систем. Бибило П. Н. (2006г.) Скачать

Рассматриваются наиболее распространенные на практике пакеты STD_LOGIC_1164, NUMERIC_STD, EXEMPLAR_1164, TEXTIO, STD_LOGIC_TEXTIO, VITAL языка VHDL и их использование при проектировании цифровых систем на элементной базе сверхбольших интегральных схем, в том числе базовых матричных кристаллов. Приведены примеры и маршруты проектирования с использованием системы ModelSim моделирования и системы LeonardoSpectrum синтеза логических схем по алгоритмическим VHDL-описаниям цифровых систем. Предназначена для специалистов, занимающихся проектированием цифровых систем и знакомых с основными элементами языка VHDL, может быть полезна студентам и аспирантам, изучающим язык VHDL и его применение в системах автоматизированного проектирования.

Основы языка VHDL. 3-е издание. Бибило П. Н. (2007г.) Скачать

Описывается применение языка VHDL на алгоритмическом и логическом уровнях проектирования цифровых систем. Язык VHDL является международным стандартом в системах автоматизации проектирования и предназначен для спецификации, моделирования и синтеза цифровых систем на основе заказных и программируемых пользователями сверхбольших интегральных схем.

Книга предназначена для первоначального ознакомления с языком VHDL и может быть полезна студентам, аспирантам и специалистам, занимающимся разработкой электронной аппаратуры с помощью средств САПР.

Последний раз редактировалось: Viktor2312 (Вт Июл 12 2016, 19:46), всего редактировалось 10 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

4

И ещё немного литературы:

VHDL'92. Новые свойства языка описания аппаратуры. Берже Ж.-М., Фонкуа А., Мажино С., Руйар Ж. (1995г.) Скачать

Книга представляет новый стандарт языка спецификации проектов аппаратуры на базе сверхбольших высокоскоростных интегральных схем — VHDL'92. Проанализировано большинство слабых мест и неоднозначностей VHDL'87. Показаны изменения, которые либо устранили, либо дали возможность обойти эти недостатки при сохранении максимальной преемственности. Классифицируются и объясняются новые свойства и возможности языка VHDL.

Для разработчиков цифровых систем, СБИС и средств автоматизации их проектирования, особенно для тех, кто работает над совместными проектами с зарубежными партнерами или собирается представить свои разработки на мировом рынке. Может быть полезна менеджерам в области проектирования изделий радиоэлектроники, а также аспирантам и студентам старших курсов соответствующих специальностей.

Проектирование систем на микросхемах программируемой логики. Грушвицкий Р., Мурсаев А., Угрюмов Е. (2002г.) Скачать

Пособие посвящено проектированию систем на интегральных схемах с программируемой структурой (ИСПС) и включает материалы учебных дисциплин, читаемых авторами. Рассмотрены методика создания проектов на ИСПС, включая тестирование и верификацию c ориентацией на применение современных систем автоматического проектирования (САПР); архитектура и характеристики ИСПС; концепции языкового описания аппаратуры. Приведен сравнительный анализ современных ИСПС. Изложены основные концепции языкового описания цифровых устройств на системном уровне (язык SystemC), блочном уровне (языки VHDL, VerilogHDL), а также особенности описания смешанных (цифровых и аналоговых) систем (VHDL-AMS). Пособие содержит примеры разработки проектов. Практически все разделы включают новую информацию.

Проектирование на ПЛИС. Курс молодого бойца. Клайв Максфилд (2007г.) Скачать

Эта книга является не только пособием по проектированию устройств на основе ПЛИС (FPGA), но и содержит поистине энциклопедические сведения. Кроме архитектурных особенностей последних поколений микросхем ПЛИС, здесь рассматриваются различные методы и средства проектирования. Проводится обзор и анализ схемотехнических подходов к проектированию (которые все еще находят применение), HDL-моделирования и логического синтеза, а так же современных технологий проектирования, основанных на использовании языка C/C++. Рассматриваются специализированные вопросы, такие как совместное проектирование программно-аппаратных систем и разработка систем цифровой обработки сигналов (ЦОС). Обсуждаются и технические новинки, например программируемые пользователем массивы узлов (FPNA).

Написанная в непринужденном, увлекательном стиле, книга будет хорошим пособием и для начинающих, и для опытных инженеров, разрабатывающих устройства на основе ПЛИС. Книга послужит весьма ценным источником информации и для специалистов, разрабатывающих устройства на основе заказных микросхем и переходящих на использование ПЛИС. А также, несомненно, привлечет внимание широкого круга читателей, в том числе технических аналитиков, студентов и продавцов.

Схемотехника и средства проектирования цифровых устройств. В. Амосов (2012г.)

Скачать Part1

Скачать Part2

Скачать Part3

Приводится описание схемотехники цифровых устройств. Основное внимание уделяется обучению разработке программно-аппаратных комплексов, содержащих процессор: написание поведенческих и структурных VHDL и Verilog HDL-моделей, их тестирование и функциональное тестирование выполнения программ. Описывается современный инструментарий разработчика. На примерах дается описание использования этого инструментария. Каждая глава содержит упражнения или лабораторные работы, позволяющие закрепить теоретический материал. Достоинством книги является сочетание теории и практики, что позволяет легко освоить этапы разработки программно-аппаратных комплексов, включая тестирование как аппаратной, так и программной составляющих.

Для студентов вузов и специалистов-схемотехников.

VHDL'92. Новые свойства языка описания аппаратуры. Берже Ж.-М., Фонкуа А., Мажино С., Руйар Ж. (1995г.) Скачать

Книга представляет новый стандарт языка спецификации проектов аппаратуры на базе сверхбольших высокоскоростных интегральных схем — VHDL'92. Проанализировано большинство слабых мест и неоднозначностей VHDL'87. Показаны изменения, которые либо устранили, либо дали возможность обойти эти недостатки при сохранении максимальной преемственности. Классифицируются и объясняются новые свойства и возможности языка VHDL.

Для разработчиков цифровых систем, СБИС и средств автоматизации их проектирования, особенно для тех, кто работает над совместными проектами с зарубежными партнерами или собирается представить свои разработки на мировом рынке. Может быть полезна менеджерам в области проектирования изделий радиоэлектроники, а также аспирантам и студентам старших курсов соответствующих специальностей.

Проектирование систем на микросхемах программируемой логики. Грушвицкий Р., Мурсаев А., Угрюмов Е. (2002г.) Скачать

Пособие посвящено проектированию систем на интегральных схемах с программируемой структурой (ИСПС) и включает материалы учебных дисциплин, читаемых авторами. Рассмотрены методика создания проектов на ИСПС, включая тестирование и верификацию c ориентацией на применение современных систем автоматического проектирования (САПР); архитектура и характеристики ИСПС; концепции языкового описания аппаратуры. Приведен сравнительный анализ современных ИСПС. Изложены основные концепции языкового описания цифровых устройств на системном уровне (язык SystemC), блочном уровне (языки VHDL, VerilogHDL), а также особенности описания смешанных (цифровых и аналоговых) систем (VHDL-AMS). Пособие содержит примеры разработки проектов. Практически все разделы включают новую информацию.

Проектирование на ПЛИС. Курс молодого бойца. Клайв Максфилд (2007г.) Скачать

Эта книга является не только пособием по проектированию устройств на основе ПЛИС (FPGA), но и содержит поистине энциклопедические сведения. Кроме архитектурных особенностей последних поколений микросхем ПЛИС, здесь рассматриваются различные методы и средства проектирования. Проводится обзор и анализ схемотехнических подходов к проектированию (которые все еще находят применение), HDL-моделирования и логического синтеза, а так же современных технологий проектирования, основанных на использовании языка C/C++. Рассматриваются специализированные вопросы, такие как совместное проектирование программно-аппаратных систем и разработка систем цифровой обработки сигналов (ЦОС). Обсуждаются и технические новинки, например программируемые пользователем массивы узлов (FPNA).

Написанная в непринужденном, увлекательном стиле, книга будет хорошим пособием и для начинающих, и для опытных инженеров, разрабатывающих устройства на основе ПЛИС. Книга послужит весьма ценным источником информации и для специалистов, разрабатывающих устройства на основе заказных микросхем и переходящих на использование ПЛИС. А также, несомненно, привлечет внимание широкого круга читателей, в том числе технических аналитиков, студентов и продавцов.

Схемотехника и средства проектирования цифровых устройств. В. Амосов (2012г.)

Скачать Part1

Скачать Part2

Скачать Part3

Приводится описание схемотехники цифровых устройств. Основное внимание уделяется обучению разработке программно-аппаратных комплексов, содержащих процессор: написание поведенческих и структурных VHDL и Verilog HDL-моделей, их тестирование и функциональное тестирование выполнения программ. Описывается современный инструментарий разработчика. На примерах дается описание использования этого инструментария. Каждая глава содержит упражнения или лабораторные работы, позволяющие закрепить теоретический материал. Достоинством книги является сочетание теории и практики, что позволяет легко освоить этапы разработки программно-аппаратных комплексов, включая тестирование как аппаратной, так и программной составляющих.

Для студентов вузов и специалистов-схемотехников.

Последний раз редактировалось: Viktor2312 (Пт Окт 03 2014, 19:29), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

5

Начинать наше изучение мы будем с освоения самого языка описания аппаратуры VHDL. Так как это, основа основ. И без его знания, нет смысла покупать всевозможные платы, так называемые Starter Kit, сами микросхемы ПЛИС или делать различные соединительные кабели для их программирования, конфигурирования.

И так как мы будем изучать серьёзно и углублённо, да и ещё к тому же с нуля, то в первую очередь нам необходимо освоить, хотя бы в общих чертах основные элементы языка, такие как лексические элементы, объекты их типы и виды, декларации, атрибуты, имена, операторы и многое другое. Для того, чтобы при необходимости рассмотреть простой пример, он не казался нам набором иероглифов.

Процесс будет долгий, нудный, но надеюсь полезный, периодически могут встречаться повторения какого-нибудь материала, но думаю страшного в этом ничего не будет, как говориться - "повторение мать учения".

И непосредственно со следующего поста, приступим...

И так как мы будем изучать серьёзно и углублённо, да и ещё к тому же с нуля, то в первую очередь нам необходимо освоить, хотя бы в общих чертах основные элементы языка, такие как лексические элементы, объекты их типы и виды, декларации, атрибуты, имена, операторы и многое другое. Для того, чтобы при необходимости рассмотреть простой пример, он не казался нам набором иероглифов.

Процесс будет долгий, нудный, но надеюсь полезный, периодически могут встречаться повторения какого-нибудь материала, но думаю страшного в этом ничего не будет, как говориться - "повторение мать учения".

И непосредственно со следующего поста, приступим...

Последний раз редактировалось: Viktor2312 (Пт Окт 03 2014, 19:38), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

6

Теория_001.

Лексические элементы и типы данных.

Начнём, с простого, с лексических элементов.

Текст на языке VHDL - это последовательность раздельных лексических элементов. Далее перечислим их и потом детально рассмотрим каждый из них:

* идентификаторы (имена);

* разделители;

* ключевые (зарезервированные) слова;

* литералы (константные значения);

* комментарии.

Как видно из предыдущего списка, всего у нас получается пять лексических элементов.

Меду собой смежные лексические элементы разделяются:

* разделителями;

* концами строк;

* знаками форматирования.

Теперь рассмотрим более подробна каждый из лексических элементов.

Идентификаторы.

Идентификаторы употребляются как пользовательские имена и ключевые слова. Идентификаторы используются как имена для объектов, процедур, функций, процессов, объектов конструкции и т.д в VHDL. Они могут иметь любую длину, при условии, что весь идентификатор написан в одной строке программы.

Идентификатор должен начинаться с буквы, это важно, он не должен ни в коем случае начинаться с цифры. Например идентификатор 5AB неправильный, так как начинается с цифры. Так же в идентификаторе кроме букв и цифр может употребляться символ подчёркивания _ , но не допускается идущих подряд два символа подчёркивания, а также идентификатор не должен начинаться или заканчиваться символом подчёркивания.

И важно: В VHDL коде нет различия между прописными и строчными буквами. Это значит, что идентификаторы SET_TOOL1 и set_tool1 идентичны и являются одним и тем же идентификатором.

Так же в именах идентификаторов нельзя использовать ключевые (зарезервированные) слова, например, next, to, case, disconnect и другие, список которых будет представлен позже. В зависимости от стандарта, этот список пополнялся новыми ключевыми словами, поэтому необходимо иметь полный список ключевых слов в соответствии с последним стандартом.

Часто встречающаяся ошибка в идентификаторах, при подготовке текстов программ, перепутываются внешне одинаковые символы латиницы и кириллицы и близкие по изображению символы цифр и букв, поэтому за этим необходимо строго следить.

Вот примеры правильных идентификаторов:

Sim_out

DityS

Count6_SUM

Как видно в этих примерах прописные буквы применены по большей части для удобочитаемости данных идентификаторов, но их можно было бы записать и так, это будут эти же идентификаторы:

sIM_OUT или SIM_OUT или sim_out

ditys или DITYS или dITYs

Count6_sum или COUNT6_SUM

Так как, не забываем, что в VHDL коде нет различия между прописными и строчными буквами.

Так же существуют расширенные имена. Они могут включать любые символы кода ASCII. Расширенные имена ограничиваются символом \ наклонная черта влево.

И позволяют расширить диапазон применяемых имён.

Пример:

\d+dot_xo\

В VHDL применяются и составные имена - это последовательность имён, разделённых точками. С их помощью осуществляется доступ к элементам структур и другим объектам, например к пакетам.

Пример:

VS.DD.E1

Важные замечания:

* Идентификатор должен начаться с символа (a .. z).

* Не позволяются никакие пробелы в идентификаторах.

* Идентификаторы не чувствительны к регистру, то есть верхние и нижние - символы регистра считаются идентичными.

* дентификаторы состоят из латинских символов (a .. z), символов подчеркивания (_) и цифр (0 .. 9). Не позволяется использовать какие-либо специальные символы, включая не латинские (специфические для языка) символы.

Разделители.

Разделители бывают обычные и составные. Обычные разделители, это один из специальных символов:

& ( ) * + ? - . / : ; < = > |

Составной разделитель, это композиция двух смежных специальных символов:

=> ** := /= >= <= <>

Пример. VHDL-предложение:

A <= B and C;

Данный пример имеет шесть лексических элементов A, <=, B, and, C, ;

Два из шести лексических элементов являются разделителями:

<= (составной разделитель - оператор назначения сигнала)

;

В качестве разделителей в данном примере используются пробелы, однако нет необходимости иметь разделитель между оператором ; и лексическим элементом С.

Последний раз редактировалось: Viktor2312 (Пт Окт 03 2014, 19:48), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

7

Теория_002.

Ключевые (зарезервированные) слова.

Как и многие другие языки, VHDL имеет ключевые (зарезервированные) специальные слова.

Список зарезервированных (ключевых) слов.

Литералы.

Классификация литералов (константных числовых значений) приведена на рисунке:

Как видно из рисунка, абстрактные (Abstract) литералы состоят из десятичного (Decimal) и базового (Based), поэтому сначала рассмотрим десятичные литералы.

Десятичный литерал может быть целым, вещественным или вещественным с экспонентой.

Например:

Целые десятичные литералы: 35, 0, 2Е7, 4е5, 487_001.

Вещественные десятичные литералы: 34.0, 0.0, 0.398, 3.141_592_6.

Вещественные десятичные литералы с экспонентой: 2.78Е-12, 2.0Е+4, 4.078Е+25.

Знак экспоненты Е может быть строчным или прописным. Подчёркивание в десятичном литерале не является значащим. Экспонента для целого литерала не должна иметь знак минус.

Базовый литерал указывает на систему счисления: от двоичной до шестнадцатеричной:

Двоичная: 2#1111_1100# - число 252 в двоичной системе счисления

Шестнадцатеричная: 16#fc# или 016#0FC#

Десятичная: 10#252#

Семеричная: 7#510#

Число 16#6#E1 означает 6*16**1 - это число 96 в десятичной системе счисления 96=6х161. Символ * - знак умножения, ** - возведение в степень. Число 2Е-3 не является целым, 3е4 - это число 3х104.

Последний раз редактировалось: Viktor2312 (Пн Окт 06 2014, 11:33), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

8

Теория_003.

Основные понятия.

Основные понятия.

Теперь немного отвлечёмся от литералов, вернёмся к ним позже и почитаем основные понятия.

Данные основные понятия взяты из одной из статей на просторе интернета, но думаю пригодятся, для общего развития.

Интерфейс — описывает наше с вами устройство, как черный ящик с входами и выходами, т. е. главная его задача показать какие входы и выходы есть у нашего устройства для связи с внешним миром.

Архитектура — описывает поведение нашего устройства или раскрывает его внутреннюю структуру, т. е. в архитектуре описывается алгоритм функционирования нашего устройства.

Стоит обратить внимание, что архитектура может быть описана в общем случае двумя вариантами:

* поведенческим стилем(описывается алгоритм работы устройства);

* структурным стилем(описывается структура устройства).

Поведенческий стиль удобно использовать при описании элементов на низком уровне иерархии, а структурным на верхних уровнях иерархии, т. е. написать много маленьких устройств поведенческим стилем, а потом описать состоящее из них устройство структурным стилем, в виде связей между ними.

Операторы языка — операторы в языке бывают последовательные, а бывают параллельные. Параллельные операторы вводятся для того, чтобы отобразить параллельность протекающих в железе процессов. Но любой параллельный оператор можно заменить специальным параллельным оператором процесса с последовательными операторами внутри его, он как раз для этого и предназначен. При помощи параллельных операторов мы описываем как бы элементы схемы которые могут работать одновременно, при моделировании каждому параллельному оператору ставится в соответствие свой процесс. Далее я буду считать каждый параллельный оператор процессом.

Сигналы — связывают между собой процессы. Они являются внешними по отношению к процессу, т. е. процесс может считывать сигнал и выдавать значение в сигнал. Поэтому сигналы могут объявляться только в области деклараций архитектуры. Так же сигналы могут хранить значения, которые необходимо передавать от процесса к процессу.

Переменные — переменные используются внутри параллельного оператора процесса и требуются для описании алгоритма работы процесса. Их надо использовать в тех случаях, когда не требуется переносить информацию от процесса к процессу.

Атрибуты — это значения(характеристики), связанные с какими-либо объектами языка. Например типами, сигналами, переменными и т. д.

Типы — множества значений с какими то общими характеристиками. Характеризуются типы набором значений, которые могут принимать объекты (сигнал, переменные) данного типа, а так же набором операций которое могут выполнятся с объектами данного типа.

Библиотеки и пакеты — пакеты представляют собой структуры в которых хранятся описания различных функций, процедур, компонентов, типов, констант и т. д, все пакеты собираются в библиотеки, которые в последствии подключаются к проектам.

Последний раз редактировалось: Viktor2312 (Вс Ноя 01 2015, 03:06), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

9

Теория_004.

Базовые конструкции моделей на языке VHDL.

Сигналы.

Базовые конструкции моделей на языке VHDL.

Сигналы.

Сигналы являются отдельным классом объектов в VHDL, отличным от классов переменных и констант, достаточно традиционных для языков высокого уровня. Понятие сигнала не имеет аналогов в языках программирования типа FORTRAN, C, PASCAL и др.

Цифровые системы работают во времени, преобразуя и передавая сигналы. Естественно, что понятие сигнала является базовым в языке описания аппаратуры - языке VHDL. Сигналы являются абстракцией, представлением в модели на VHDL состояния проводников в структуре цифрового устройства.

О понятии время.

Рассуждая о языках и системах моделирования, мы имеем дело с несколькими понятиями, которые соотносятся с термином "время":

* физическое время моделируемого устройства. Оно непрерывно, в нём протекают различные физические процессы, изменяются электрические сигналы в цифровых устройствах, наблюдаемые на логическом уровне как изменения логических состояний;

* модельное время. Это время в модели устройства, оно является обобщённым представлением, на уровне модели устройства, физического времени, в котором работает моделируемое устройство. Модельное время дискретно;

* время моделирования. Это время выполнения программы на VHDL. В семантике программы на VHDL впрямую не наблюдается, однако, проявляется через упорядочение операторов программы по времени выполнения. Не имея для программиста на VHDL числовых значений, время работы системы моделирования позволяет определить отношение порядка над событиями - выполнением операторов программы в VHDL. Для каждой пары исполненных операторов программы определены отношения "выполнен раньше"/"выполнен позже".

Важно различать эти три разных вида времени, с которыми имеет дело проектировщик, работающий на языке VHDL.

Сигналы в цифровых устройствах. Каждое изменение состояния элемента схемы, его входов, является воздействием, которое может привести к изменению некоторого сигнала. Например, подача '1' на вход вентиля может привести к изменению сигнала на его выходе, но не мгновенно, а через интервал времени, определяемый задержкой вентиля (tв, скажем, 5нс). Так что, подавая '1' на вход вентиля в момент t2, мы как бы "запланировали" изменение сигнала на его выходе на время t3=t2+tв.

А что будет на выходе вентиля в момент t1=t2+tв-2нс? Это определяется тем, что было на входах вентиля (т. е. - что было запланировано, но ещё не успело выполниться, находится в процессе выполнения). Таким образом, в момент t2 в схеме идёт множество процессов которые "запланировали" значения сигналов на каждый момент времени, от момента t2 на некоторый промежуток времени вперёд. В текущем состоянии физического устройства как бы заложена временная диаграмма рассматриваемого сигнала на некоторый период времени вперёд.

В реальном цифровом устройстве, которое моделируется программой на VHDL, воздействий на сигнал, приводящих к его изменению, может быть несколько. Если мы посмотрим с этой точки зрения на сигнал и на устройство, то увидим, что в текущий момент физического времени в схеме одновременно идёт множество процессов, в разных её элементах и на связях между ними. Процессы в устройстве, которые приведут к изменению сигнала, уже идут, но в изменённом состоянии сигнала они проявятся через некоторые промежутки времени (возможно, разные процессы - через разные промежутки).

Сигналы в моделях устройств на VHDL. Сигналы, как и переменные, имеют некоторые значения, которые им присваиваются. Однако если переменную характеризует только значение, то сигнал характеризуется и моментом модельного времени, в который этот сигнал имеет данное значение. Можно сказать, что состояние сигнала - это пара: момент модельного времени/значение, которое сигнал имеет в данный момент.

Именно ассоциация сигнала с моментами модельного времени является его основным отличием от переменных. Сигнал существует в модельном времени, в каждый момент которого он может иметь своё значение, а переменная всегда имеет одно текущее значение. Таким образом, сигнал - это не тип переменной, это совсем другой, принципиально отличный класс программных объектов. И разница здесь значительно существенней, чем между переменной и константой.

По ходу модельного времени сигнал может менять своё значение. Последовательность значений сигнала в привязке к моментам модельного времени в течение некоторого промежутка времени формирует временную диаграмму сигнала (waveform).

В модели устройства на языке VHDL воздействия, изменяющие состояние сигнала, принимают форму присваивания значения сигналу. Проявляется воздействие в изменении значения сигнала, как правило, не в тот момент модельного времени, когда происходит это воздействие, а в другой, отстоящий от текущего на некоторый промежуток времени (задержку) по оси модельного времени.

Как и в физическом устройстве, в его модели на языке VHDL параллельно идёт множество процессов, определяющих значения сигналов в каждый момент модельного времени. Однако из прагматических соображений, чтобы сократить время прогона модели, система моделирует работу компонентов схемы не во всех моментах модельного времени, а только в тех, на которые запланированы действительные изменения каких-либо сигналов. Между такими моментами модельного времени сигналы не меняют своих значений, что мы и можем наблюдать при визуализации результатов моделирования на временных диаграммах.

События изменения сигнала. Изменение сигнала, реализуемое в какой-то момент модельного времени, называют событием (event). Принцип продвижения модельного времени системой моделирования формулируется так:

от момента события - до следующего момента модельного времени, в который происходит хотя бы одно событие, пропуская промежуточные моменты, в которые не происходит никаких событий. В системах моделирования это называют событийным моделированием.

Транзакция. Когда мы осмысливаем понятие переменных в языках программирования, обычно представляем себе определённые аспекты их реализации после трансляции, мыслим о них как о выделенных под переменные участках памяти. Также и при обсуждении сигналов и механизмов языка VHDL полезно представлять, хотя бы в общем виде, как сигналы реализуются в системах моделирования, выполняющих программы на VHDL.

В реализации сигналов, изменяемых в модельном времени, основным становится планирование в этом времени изменений сигналов. При выполнении операторов присваивания значения сигналу, системой моделирования формируется специальная структура данных, пара: значение сигнала/момент модельного времени, когда сигнал примет это значение. Такая пара в описаниях языка VHDL называется транзакцией (transaction).

Транзакция - это внутренняя инструкция системы моделирования по изменению указанного сигнала в заданный момент модельного времени.

Система моделирования работающая по принципам событийного моделирования, ведёт список транзакций, упорядоченных по меткам модельного времени.

Транзакция, как и список транзакций, является механизмом реализации VHDL, внутренним делом системы моделирования. Однако эти понятия часто привлекают при описании и разъяснении различных механизмов языка VHDL.

Источник сигнала (драйвер). Ещё одним понятием, связанным с сигналом и часто используемым в описании VHDL, является понятие драйвера (driver) - источника сигнала.

В реальных цифровых устройствах выход элемента схемы формирует сигнал на проводнике, подсоединённом к этому выходу, он является источником сигнала в этой точке схемы. Каждый выход каждого элемента схемы - источник для одного сигнала. Множество элементов схемы функционируют параллельно в физическом времени, причём элемент, имеющий несколько выходов, формирует сигналы на них также параллельно во времени. Когда несколько выходов элементов схемы подсоединяются проводниками в одну точку схемы, то получается, что для этой точки схемы имеется несколько источников сигнала. Результирующий сигнал в этой точке схемы формируется как результат выполнения (на физическом уровне) некоторых преобразований над сигналами, сформированными всеми источниками. Вид выполняемого преобразования зависит от элементной базы, используемой в устройстве.

Работа с сигналами в программе на VHDL представлены специальными операторами присваивания значений сигналам. Один источник сигнала и в реальном устройстве, и программе на VHDL, формирует один сигнал.

Однако в языке VHDL источник сигнала может не только определять значение сигнала в какой-то один момент модельного времени, но и задавать целую последовательность значений сигнала в разные моменты модельного времени, формировать некоторую планируемую временную диаграмму сигнала (projected output waveform).

В реализации языка VHDL запланированная источником временная диаграмма представляется упорядоченным (по моментам модельного времени) списком транзакций, фиксирующих моменты изменения сигнала на временной диаграмме. Часто в описании VHDL именно этот список транзакций, связанный с одним источником сигнала, называют термином драйвер (driver).

Поскольку каждый источник сигнала в реальной схеме - выход некоторого элемента, формирует свой сигнал параллельно во времени с другими источниками сигналов, то и в модели устройства на VHDL источники сигналов работают параллельно в модельном времени.

Синтаксически, в структуре программы на VHDL, параллельно работающий источник сигнала может быть оформлен по-разному. Это может быть отдельный параллельный оператор присваивания значения сигналу среди операторов тела процесса (параллельная конструкция программы на VHDL). Но в любом варианте, осмысливая соответствующие программные конструкции и фрагменты программ на VHDL, представляющие источники сигналов, мы должны стараться соотносить их с реальной работой схем и формируемых ими сигналов.

Конец Теория_004.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

10

Теория_005.

Структура описания объекта моделирования.

Структура описания объекта моделирования.

Описание объектов моделирования состоит из:

* декларативной части;

* описания архитектуры.

В декларативной части описываются связи объекта с внешним миром - входы и выходы объекта. Это, прежде всего, спецификация интерфейса описываемого объекта.

Понятие entity определяется как "интерфейс объекта проекта". В entity описывается интерфейс между объектом проекта и окружением, в котором употребляется объект. "Внутренность" объекта в entity не описывается и может быть уподоблена "чёрному ящику".

В описании архитектуры определяется функция специфицируемого объекта, осуществляемого им формирования выходных сигналов на основании входных сигналов и внутреннего состояния объекта.

Термин "архитектура" безотносительно к языку VHDL может быть определён как распределение функций, реализуемых системой, по отдельным её уровням и точное определение границ между этими уровнями.

К термину "архитектура" близок термин "структура", понимаемый как совокупность элементов системы и связей между ними.

Архитектура - это структура системы на функциональном уровне её описания.

Архитектурное тело (architecture) определяет тело объекта, т. е. раскрывает внутренность "чёрного ящика". В архитектурном теле описываются функции (поведение) либо структура объекта проекта.

В entity (в разделе деклараций) наряду с декларацией портов могут быть декларированы параметры. Для декларации таких параметров употребляется ключевое слово generic (настраиваемый). С помощью generic могут передаваться такие параметры, как ширина (разрядность) шины, число входных либо выходных полюсов, задержки элементов и т. д.

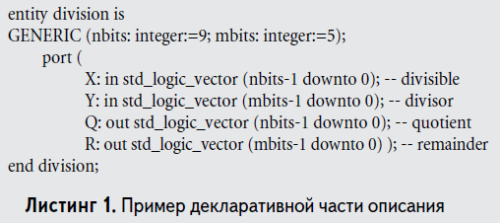

Декларативная часть.

Полный формат декларативной части описания объекта моделирования имеет следующий синтаксис:

- Код:

entity entity_name is

[generic (generic_interface_list);]

[port (port_interface_list);]

[begin {concurrent_assertion_statement |

passive_concurrent_procedure_call_statement |

passive_process_statement}]

{entity_declarative_item}

end [entity] [entity_name];

После ключевого слова entity указывается некоторый идентификатор entity_name - имя объекта моделирования. Поскольку оно используется для идентификации объекта в рамках проекта, имя объекта моделирования должно быть уникальным.

Секция generic предназначено для описания констант, определяющих изменяемые параметры объекта моделирования. Например, таким образом могут определяться времена задержек, размер внутренних буферов и др. Секция generic не является обязательной.

В терминах языка VHDL входы и выходы проектируемой схемы называют портами. Порты - это специальные программные объекты, являющиеся сигналами, а не переменными. Подобно переменным в традиционных языках программирования, в программе на VHDL порты должны быть определены (декларированы) с указанием типа соответствующих им сигналов. Для определения входных и выходных портов используется секция port в декларативной части спецификации объекта моделирования.

После ключевого слова port в круглых скобках располагается список описаний сигналов - port_interface_list. Он имеет следующий синтаксис:

{identifier, {...} : [mode] subtype_indication [:= expression]}, {...}

Описание каждого сигнала состоит из имени, вида сигнала [mode] и типа сигнала. Вид сигнала может иметь одно из следующих значений:

* in - входной сигнал;

* out - выходной сигнал;

*inout - сигнал являющийся и входным, и выходным.

Все типы которые указываются в описании портов, должны быть уже известны. Как видно из общей формы синтаксиса декларации entity. Эти описания могут располагаться в том же файле, выше по тексту, или (как часто делается), вынесены в отдельный пакет или библиотеку.

Например:

- Код:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.STD_LOGIC_arith.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity ...

В рамках описания, в секции port сигналам могут присваиваться значения по умолчанию. Если для сигнала определено значение по умолчанию, то оно используется внутри объекта моделирования в том случае, если сигналу не будет присвоено другое значение извне. Идентификаторы нескольких сигналов, имеющих одинаковое дальнейшее описание (вид, тип, значение по умолчанию, если оно есть) могут следовать в одном описании, через запятую.

Например:

- Код:

entity wers is

port(a : in std_logic;

b : in std_logic;

c: out std_logic);

end entity wers;

Тот же код:

entity wers is

port(a,b : in std_logic;

c: out std_logic);

end entity wers;

Секция port так же не является обязательной составляющей декларативной части описания объекта. Объект моделирования может не иметь входов и выходов. Такие объекты, как правило, расположены на верхнем уровне иерархии.

После ключевого слова begin следуют секции параллельно выполняющихся действий (не является обязательной частью описания), которые могут использоваться для проверки правильности функционирования объекта и для документирования процесса функционирования.

Последней располагается секция внутренних деклараций, {entity_declarative_item} описываемого объекта. В этой секции может содержаться декларация констант, переменных, сигналов и типов, являющихся внутренними для данного объекта моделирования, - т. е. доступных только внутри этого объекта.

Завершается описание объекта ключевым словом end, за которым следует слово entity (по стандарту VHDL'93 - обязательно); потом указывается имя описанного объекта (рекомендуется).

Пример, простейшего описания декларативной части объекта моделирования:

- Код:

entity aser is

port(a,b,c : in bit;

set : out bit);

end entity aser;

В листинге описан объект моделирования с именем aser. Он имеет три входных сигнала - a, b, c имеющих тип bit, и один выходной сигнал set того же типа.

И ещё один простой листинг:

- Код:

entity aser1 is

port(a : in integer;

b : in integer:=1; -- Значение по умолчанию.

c : in integer;

set : out bit);

end entity aser1;

В этом листинге описан объект моделирования с именем aser1. Он имеет три входных сигнала - a, b, c, имеющих тип integer, и один выходной сигнал set типа bit. Одному из трёх его входных сигналов, сигналу b, присваивается значение по умолчанию, равное 1.

Конец Теория_005.

Последний раз редактировалось: Viktor2312 (Вс Апр 26 2015, 10:40), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Немного полезной информации, для общего развития.

Немного полезной информации, для общего развития.

11

Краткая характеристика языка VHDL.

Хотя язык VHDL внешне выглядит так же, как и другие традиционные языки программирования (поскольку имеет литералы, разделители, операторы и т. д.), он обладает некоторыми важными отличительными характеристиками.

* Проекты цифровых устройств, созданные с помощью языка VHDL, имеют, как правило, иерархическую структуру.

* Каждый автономный проектируемый модуль (субблок проектируемого цифрового устройства) имеет:

- строго определённый интерфейс взаимодействия с другими модулями;

- точную спецификацию внутреннего устройства проектируемого модуля, описывающую концепцию и функционирование модуля.

* Спецификации модулей VHDL-проектов могут использовать или математические алгоритмы, описывающие их работу, или описание аппаратурной структуры проектируемого модуля. В соответствии с уровнями абстракций проектов описание модуля может иметь поведенческую или структурную форму.

* Моделирование алгоритма работы проекта основывается на событийном принципе управления.

* VHDL-проект позволяет выполнять моделирование протекания параллельных процессов в электрических схемах, временной анализ сигналов и их параметров.

* VHDL поддерживается инструментальными средствами синтеза и системами автоматического проектирования (САПР), которые могут создавать прямо из описания VHDL-проекта его аппаратную реализацию (связанные между собой структуры логических элементов, содержащихся в СБИС).

* Используя VHDL, можно проектировать, моделировать и синтезировать практически любое цифровое устройство, начиная от простой комбинационной схемы до законченной микропроцессорной системы на СБИС.

Перечисленные выше характеристики языка VHDL как специализированного языка описания цифровых устройств реализуются с помощью следующих языковых средств:

* Библиотеки и пакеты.

* Проекты: интерфейс и архитектура проекта.

* Подпрограммы: функции и процедуры.

* Скалярные типы данных: переменные, числовые, физические.

* Программные элементы данных: константы, переменные, сигналы, порты, идентификаторы.

* Математические операции: логические, отношений, арифметические.

* Программные операции: установка значений сигналов, присвоение значений переменным, реализация связи портов и сигналов.

* Математические выражения: логические, алгебраические, логико-алгебраические.

* Операторы комбинаторной логики: простой установки значения сигнала (ПУЗС), условной установки значения сигнала (УУЗС), селективной установки значения сигнала (СУЗС), оператор process, оператор реализации компонента port map.

* Операторы регистровой логики: оператор process, ПУЗС, оператор условной передачи управления, оператор цикла, оператор выбора.

В отличие от процедурных языков программирования, языковые средства которых обеспечивают выполнение вычислений над абстрактными данными и управление ими, VHDL-проект описывает цифровое устройство, учитывая его многогранность, поведение, структуру, функциональные и физические свойства, а также взаимодействие со специальной аппаратурой, физически реализующей проект цифрового устройства в микросхеме ПЛИС.

Остановимся особо на некоторых важных отличиях языка VHDL. VHDL по существу является языком параллельного программирования, т. е. в его конструкции существуют операторы, соответствующие логическим вентилям. Эти операторы обрабатываются (т. е. вычисляются) по параллельному принципу. Суть данного принципа состоит в том, что, как только сигнал, содержащийся в описании проектируемого цифрового устройства, изменяет своё значение (говорят, что "происходит событие на сигнале"), все операторы, принимающие участие в его обслуживании, мгновенно запускаются на выполнение и одновременно выдают конечный результат. Поэтому такие операторы называются операторами параллельной обработки (ОПО) (concurence operator). Программа, написанная на VHDL, моделирует физическое поведение системы (как правило, цифровой), сигналы в которой распространяются мгновенно. Такая программа позволяет формировать временную спецификацию (время задержки распространения сигнала на логическом элементе), а также описывать систему как соединение различного рода компонентов или функциональных блоков.

Этапы проектирования с использованием VHDL.

В подавляющем большинстве случаев аппаратная реализация проекта цифрового устройства с использованием языка VHDL протекает в соответствии со следующими этапами:

Разработка иерархической блок-схемы проекта. Выяснение базового конструктивно-технологического метода и стандартных блоков на уровне структурной схемы. Поскольку большие логические проекты являются, как правило, иерархическими, использование VHDL позволяет легко разбить проект на модули (субпроекты) и определить их интерфейсы.

Программирование. Запись VHDL-кода для модулей и их интерфейсов.

Компиляция. Анализ программного кода VHDL-проекта для выявления синтаксических ошибок, а также проверка его совместимости с другими модулями. В ходе компиляции также собирается внутренняя информация о структуре проекта, которая необходима для моделирования работы проектируемого цифрового устройства.

Моделирование. Определение и применение входных воздействий к откомпилированному коду проекта с наблюдением выходных реакций. Моделирование может выполняться как в форме функционального контроля, т. е. проверки логики работы проекта без учёта временных соотношений и задержек распространения сигналов на логических элементах, так и в качестве одного из этапов верификации завершённого проекта.

Синтез. Преобразование VHDL-описания в набор примитивов или логических элементов, которые могут быть реализованы с учётом конкретной технологии.

Компоновка, монтаж и разводка. Отображение проекта на карте синтезирующих элементов, содержащихся в микросхеме ПЛИС.

Временной анализ. Получение фактических задержек реализованной в микросхеме ПЛИС цифровой схемы проекта с учётом длины соединений, электрических нагрузок и других известных факторов.

Уровни представления и формы абстракции

цифровых систем.

цифровых систем.

Цифровая система на языке VHDL может быть представлена на различных уровнях и различными формами абстракции. Цифровая система может быть описана на уровне компонентов (диодов, транзисторов, логических элементов), на уровне архитектуры (структурной схемы, содержащей АЛУ, регистры, мультиплексоры и т. д.), на уровне автономной системы (ПЭВМ, ЭВМ, рабочей станции, сервера и т. д.), а также на уровне приложений (программных модулей, входящих в состав системы более высокого уровня).

Различные формы абстракции цифровой системы дают возможность сохранять описание и проект как комплексную управляемую систему.

Первичная и наивысшая форма абстракции - это поведенческая (behavioral) форма, которая позволяет описывать систему в терминах того, что она делает (или как она ведёт себя), а не в терминах её элементов либо компонентов и соединений между ними. Поведенческая форма представления определяет зависимость между входными и выходными сигналами. Поведенческая форма может быть Булевым (Boolean)выражением либо более абстрактным описанием, например, описанием межрегистровых пересылок (registr transfer) или описанием в алгоритмической форме.

В качестве примера представления поведенческой формы рассмотрим простое устройство SIREN, которое выдаёт сигнал предупреждения (Warning) всякий раз, когда автомобильный ключ вставлен в замок зажигания (Ignition_on), если дверь открыта (Door_open) или отстёгнут ремень безопасности (Seatbelt_off). На поведенческом уровне это словесное описание может быть выражено как:

Warning = Ignition_on and (Door_open or Seatbelt_off)

Структурная (structural) форма, с другой стороны, представляет систему как набор логических элементов и компонентов, которые связаны между собой таким образом, чтобы выполнить нужную функцию. Структурную форму представления можно сравнить со схемным решением связанных логических вентилей. Структурный уровень является обычно окончательным представлением физической реализации системы. Структурное представление рассмотренного выше примера:

Как говорилось выше, язык VHDL позволяет описать цифровую систему и в структурной, и в поведенческой форме. При этом поведенческая форма может быть реализована в одном из двух стилей: в виде потока данных (data flow style) и в алгоритмическом виде (algoritmic style).

Представление системы в виде потока данных позволяет описать систему с учётом направления потока перемещаемых через неё данных. Этот стиль характерен для описания поведения системы на уровне межрегистровых пересылок.

При представлении системы в алгоритмическом виде поведение системы описывается с помощью операторов (operator). При этом для описания поведения системы могут использоваться как операторы параллельной обработки (concurrent), которые выполняются параллельно, как только данные поступают на входы, так и последовательные (sequential) операторы, которые выполняются последовательно в порядке их записи. Язык VHDL допускает как параллельную, так и последовательную установку значений сигналов, которые определяют способ и порядок их выполнения.

Последний раз редактировалось: Viktor2312 (Сб Окт 31 2015, 02:47), всего редактировалось 20 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

12

Теория_006.

Описание архитектуры объекта моделирования.

Описание архитектуры объекта моделирования.

В языке VHDL под описанием архитектуры понимается описание функционирования специфицируемого объекта. Если декларативная часть описания объекта определяет его внешнее представление, задаёт интерфейсную спецификацию, вводит имя объекта и вводы/выводы ("порты", в терминах VHDL), то описание архитектуры задаёт его содержательное наполнение, спецификацию функциональной и временной работы описываемого объекта.

Отметим, что используемый в VHDL термин "архитектура" не вполне соответствует общепринятому в вычислительной технике смыслу (описание ЭВМ для программирующего на уровне машинных кодов или их символьного представления, на ASSEMBLER). Архитектурное описание на VHDL может, конечно, в конкретной программе получить и такое смысловое наполнение. Мы можем, например, в архитектурной части описания объекта моделирования - процессора, действительно дать такое описание, какое принято давать при описании архитектуры (в общепринятом смысле). Но в архитектурном описании на языке VHDL может быть, с одной стороны, дана и детальная функциональная или принципиальная схема процессора, а с другой стороны, наоборот, описание может идти на более абстрактном уровне, и программно доступные элементы архитектуры процессора не найдут отражения в архитектурном описании на языке VHDL.

Описывать архитектуру объекта на языке VHDL можно следующими способами:

1. Описать поведение объекта, преобразование информации и его внутреннего состояния, формирование выходных сигналов при поступлении входных, задать алгоритмическое описание поведения специфицируемого объекта. Внутренняя структура описываемого объекта при этом не специфицируется. Такое описание называется поведенческим описанием архитектуры объекта.

2. Описать структуру объекта, как состоящего из некоторых других объектов, указывая их перечень и связи между ними. Такое описание называется структурным описанием архитектуры объекта. Поведение объекта, преобразование информации и формирование выходных сигналов при поступлении входных, определяется здесь составом и связями объектов, формирующих заданную структуру. Сами объекты-компоненты описываются отдельно, с использованием структурного или поведенческого описания и т. д. В конечном итоге, на каком-то уровне вложенности таких описаний мы доходим либо до предопределённых компонентов, либо останавливаемся на алгоритмическом, поведенческом описании объекта-компонента.

3. Допускается и смешанное структурно-поведенческое описание, являющееся комбинацией первых двух видов описаний. Описание архитектуры объекта моделирования имеет следующий синтаксис:

- Код:

architecture identifier of entity_name is

{block_declarative_item}

begin

{concurrent_statements}

end [architecture] [identifier];

Спецификатор entity_name позволяет связать декларативную и архитектурную части описания объекта моделирования. После ключевого слова architecture указывается уникальный идентификатор identifier данной архитектуры.

После ключевого слова begin следуют параллельные операторы, задающие в алгоритмическом виде функционирование описываемой архитектуры объекта.

Завершается описание архитектуры объекта ключевым словом end, за которым следует слово architecture (по стандарту VHDL'93); потом указывается идентификатор описанной архитектуры объекта (рекомендуется).

Объект моделирования может иметь несколько различных видов архитектурного описания, однако одновременно в модели может использоваться только один из них. Выбор конкретного вида архитектурного описания осуществляется с использованием конфигурационной спецификации.

Конец Теория_006.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

13

Вставил постом выше Теория_006, чтобы была. Пост со схемами пусть так и останется, а тут мы продолжим сборку программатора. Буду добавлять периодически по чучуть фотки, описания, результаты и т. д.

Начал собирать. На фото видно корпус, который я буду применять. Решил не лепить внутри разъёма, а сделать нормально на макетной платке, МГТФ -ом соединю. Будет с одной стороны кабель с разъёмом LPT на конце, слева выходить, а справа шлейф 10 см, с разъёмом 10 контактным, ещё найти нужно его пока нет. Процесс потихоньку идёт...

BB_MV_001 (фото кликабельны, да смешное какое слово, ну вы поняли...)

И вот собственно что получилось в сборе:

BB_MV_002

Светодиодик питания горит, при подаче питания, ну а куда ему деться. Остальное ещё не проверял, в Quartus II подключал, пишет как вроде ОК, но нужно ещё разбираться, что да как. Работать думаю будет, так как схема простейшая, и там сложно, что-то ни так собрать. В общим один экземпляр программатора для ПЛИС есть ByteBlasterMV, пора думать о сборке следующего...

Немного приукрасил переднюю панель:

BB_MV_003

Начал собирать. На фото видно корпус, который я буду применять. Решил не лепить внутри разъёма, а сделать нормально на макетной платке, МГТФ -ом соединю. Будет с одной стороны кабель с разъёмом LPT на конце, слева выходить, а справа шлейф 10 см, с разъёмом 10 контактным, ещё найти нужно его пока нет. Процесс потихоньку идёт...

BB_MV_001 (фото кликабельны, да смешное какое слово, ну вы поняли...)

И вот собственно что получилось в сборе:

BB_MV_002

Светодиодик питания горит, при подаче питания, ну а куда ему деться. Остальное ещё не проверял, в Quartus II подключал, пишет как вроде ОК, но нужно ещё разбираться, что да как. Работать думаю будет, так как схема простейшая, и там сложно, что-то ни так собрать. В общим один экземпляр программатора для ПЛИС есть ByteBlasterMV, пора думать о сборке следующего...

Немного приукрасил переднюю панель:

BB_MV_003

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

Re: Изучаем VHDL и осваиваем ПЛИС фирмы Xilinx

14