Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Микросхемы ПЛИС фирмы Xilinx - FPGA 7-й серии.

Страница 1 из 1 • Поделиться

Микросхемы ПЛИС фирмы Xilinx - FPGA 7-й серии.

Микросхемы ПЛИС фирмы Xilinx - FPGA 7-й серии.

1

.

.

.

Микросхемы ПЛИС фирмы Xilinx - FPGA 7-й серии.

Конфигурируемые логические блоки CLB.

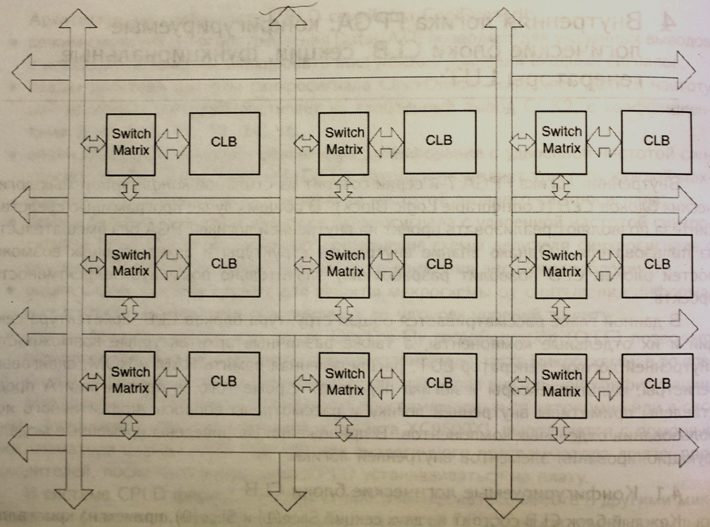

____Каждый блок CLB состоит из двух секций Slice(1) и Slice(0), причём на кристалле секция Slice(1) расположена в правом верхнем углу блока CLB, а секция Slice(0) - в левом нижнем углу (см. рис. 001). Для подключения CLB к общим ресурсам трассировки FPGA служит матрица переключателей (Switch Matrix).

Рисунок 001. Расположение секций в блоках CLB.

____Блоки CLB в FPGA 7-й серии организованы в виде столбцов. Для реализации арифметических переносов все секции в пределах одного столбца соединяются вертикально с помощью цепей переноса (см. рис. 002).

Рисунок 002. Цепи переноса в столбце блоков CLB.

____В общем случае блоки CLB в FPGA располагаются в виде регулярной матрицы (см. рис. 003). Между строками и столбцами блоков CLB находятся каналы межсоединений, которые являются ресурсами общей трассировки кристалла (interconnect routing resources). Межсоединения (interconnect) также используются для передачи сигналов между функциональными блоками FPGA, такими как: блоки ввода-вывода IOB, секции цифровой обработки сигналов DSP, блоки памяти RAM и др.

Рисунок 003. CLB и ресурсы межсоединений.

____Отметим, что секции одного блока CLB не имеют никаких соединений между собой. Возможна только передача сигналов по цепям переноса соседним секциям, расположенным выше данного блока CLB. При необходимости передачи сигналов между секциями в пределах одного блока CLB задействуются ресурсы матрицы переключателей, а при передаче сигналов между блоками CLB задействуются ресурсы межсоединений.

____Каждая секция блока CLB, в свою очередь, содержит четыре 6-входовых функциональных генератора LUT и 8 триггеров (по два на каждый LUT).

____Секции делятся на два типа: SLICEL и SLISEM. Секции типа SLISEM обладают дополнительными архитектурными возможностями, которые позволяют им конфигурироваться как блок распределённой памяти RAM на 256 битов или сдвиговый регистр SRL на 128 битов. Один блок CLB может содержать либо две секции SLICEL, либо одну секцию SLICEL и одну секцию SLICEM. Общие ресурсы одного блока CLB:

Количество

Ресурс 2

Число секций.....................................................................................................................................................8

Число LUT..........................................................................................................................................................16

Число триггеров.................................................................................................................................................2

Число цепей переноса..................................................................................................................................................256 битов

Объём распределённой памяти RAM..........................................................................................................................................................128 битов

Сдвиговый регистр.....................................................................................................................................................Таблица 1.

Таблица 2.

Таблица 3.

____Параметры ресурсов блоков CLB для семейств Artrix-7, Kintex-7 и Virtex-7 приведены в таблицах 1 - 3 соответственно.

Последний раз редактировалось: Viktor2312 (Пн Ноя 18 2019, 10:33), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Микросхемы ПЛИС фирмы Xilinx - FPGA 7-й серии.

Re: Микросхемы ПЛИС фирмы Xilinx - FPGA 7-й серии.

2

.

____Как было отмечено ранее, блоки CLB могут содержать секции двух типов: SLICEM (см. рис. 004) и SLICEL (см. рис. 005).

Рисунок 004. Архитектура секции SLICEM.

Рисунок 005. Архитектура секции SLICEL.

____Архитектура секции SLICEM включает четыре 6-входовых функциональных генератора LUT (A, B, C, D), цепь переноса, 4 вентиля XOR, 4 выходных запоминающих элемента, 4 дополнительных триггера, схемы BYPASS обхода генераторов LUT, мультиплексоры конфигурации для выбора сигналов, а также мультиплексоры F7AMUX, F7BMUX и F8MUX (на рис. 004 и рис. 005 не показаны).

____Основными входами данных являются шины A[6:1], B[6:1], C[6:1] и D[6:1], значения сигналов с которых поступают на входы соответствующих функциональных генераторов LUT. Для обхода функциональных генераторов по схеме BYPASS служат входы AX, BX, CX и DX. Кроме того, для реализации сдвиговых регистров служат дополнительные входы AI, BI, CI и DI.

____Каждая секция имеет 4 комбинационных выхода A, B, C и D, 4 регистровых выхода AQ, BQ, CQ и DQ с выходных запоминающих элементов, а также 4 выхода AMUX, BMUX, CMUX и DMUX с выходов одноимённых мультиплексоров.

____Управляющие сигналы секции SLICEM представлены сигналами: SR - установки или сброса; CLK - синхронизации; CE - разрешения синхронизации; WE - разрешения записи в распределённую память RAM.

____Кроме того, цепь переноса секции имеет входной сигнал CIN и выходной сигнал COUT. Таким образом, секция SLICEM в сумме имеет 37 входов и 13 выходов. В секции SLICEL отсутствуют дополнительные входы AI, BI, CI и DI, а также управляющий сигнал WE. Поэтому секция SLICEL имеет только 32 входа и 13 выходов.

____Отметим, что управляющие сигналы являются общими для всех запоминающих элементов секции. Поэтому триггеры FPGA 7-й серии не имеют сигналов индивидуального управления. Для управляющих сигналов SR, CE и WE активным является высокий уровень. Однако синхросигнал может программироваться с активным как положительным, так и отрицательным фронтом.

Секции блоков CLB.

____Как было отмечено ранее, блоки CLB могут содержать секции двух типов: SLICEM (см. рис. 004) и SLICEL (см. рис. 005).

Рисунок 004. Архитектура секции SLICEM.

Рисунок 005. Архитектура секции SLICEL.

____Архитектура секции SLICEM включает четыре 6-входовых функциональных генератора LUT (A, B, C, D), цепь переноса, 4 вентиля XOR, 4 выходных запоминающих элемента, 4 дополнительных триггера, схемы BYPASS обхода генераторов LUT, мультиплексоры конфигурации для выбора сигналов, а также мультиплексоры F7AMUX, F7BMUX и F8MUX (на рис. 004 и рис. 005 не показаны).

____Основными входами данных являются шины A[6:1], B[6:1], C[6:1] и D[6:1], значения сигналов с которых поступают на входы соответствующих функциональных генераторов LUT. Для обхода функциональных генераторов по схеме BYPASS служат входы AX, BX, CX и DX. Кроме того, для реализации сдвиговых регистров служат дополнительные входы AI, BI, CI и DI.

____Каждая секция имеет 4 комбинационных выхода A, B, C и D, 4 регистровых выхода AQ, BQ, CQ и DQ с выходных запоминающих элементов, а также 4 выхода AMUX, BMUX, CMUX и DMUX с выходов одноимённых мультиплексоров.

____Управляющие сигналы секции SLICEM представлены сигналами: SR - установки или сброса; CLK - синхронизации; CE - разрешения синхронизации; WE - разрешения записи в распределённую память RAM.

____Кроме того, цепь переноса секции имеет входной сигнал CIN и выходной сигнал COUT. Таким образом, секция SLICEM в сумме имеет 37 входов и 13 выходов. В секции SLICEL отсутствуют дополнительные входы AI, BI, CI и DI, а также управляющий сигнал WE. Поэтому секция SLICEL имеет только 32 входа и 13 выходов.

____Отметим, что управляющие сигналы являются общими для всех запоминающих элементов секции. Поэтому триггеры FPGA 7-й серии не имеют сигналов индивидуального управления. Для управляющих сигналов SR, CE и WE активным является высокий уровень. Однако синхросигнал может программироваться с активным как положительным, так и отрицательным фронтом.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» Статьи, заметки, очерки, разное...

» Изучаем основы VHDL, ISE, ПЛИС Xilinx. Старые семейства.

» Микросхемы ПЛИС семейства Spartan-3A

» Одна микросхема на все источники питания. Микросхемы Active-Semi серии PAC.

» Изучаем основы VHDL, ISE, ПЛИС Xilinx.

» Изучаем основы VHDL, ISE, ПЛИС Xilinx. Старые семейства.

» Микросхемы ПЛИС семейства Spartan-3A

» Одна микросхема на все источники питания. Микросхемы Active-Semi серии PAC.

» Изучаем основы VHDL, ISE, ПЛИС Xilinx.

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|