Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Разработка, сборка, наладка ВМИР-1.

Страница 1 из 1 • Поделиться

Разработка, сборка, наладка ВМИР-1.

Разработка, сборка, наладка ВМИР-1.

1

.

.

.

В этой теме, будет отражаться весь процесс разработки, сборки, наладки и программирования ВМИР-1. Напомню, реализовываться она будет, в основном, на отечественной элементной базе, то есть микропроцессорном комплекте КР580, и сопутствующих микросхемах серий К555, К531, К573, К565, и т. д.

.

.

ВМИР - аббревиатура, расшифровывается как, Вычислительная Машина Искусственного Разума.

В этой теме, будет отражаться весь процесс разработки, сборки, наладки и программирования ВМИР-1. Напомню, реализовываться она будет, в основном, на отечественной элементной базе, то есть микропроцессорном комплекте КР580, и сопутствующих микросхемах серий К555, К531, К573, К565, и т. д.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

2

Всё ещё ждём переноса в этот раздел постов на эту тему из засорённых оффтопом разделов.

Прорыв в науке и технике часто делают те, кто в отличие от всех остальных не знает, что что-то сделать нельзя, потому сдуру и начинают это пытаться сделать. По счастью в данном случае есть обоснованная надежда, что задуманное автором нереализуемо и человечество погибнет не от этого изделия.

Объявленной целью этого проекта является создание искусственного разума (ИИ). Слава Богу, что это невозможно сделать силами и средствами, которыми располагает автор (иначе ИИ уже давно бы уничтожил человечество). Но уже давно пора приравнять любые попытки разработать ИИ к преступлениям против человечества и наказывать более жестоко, чем за торговлю наркотиками и оружием.

Единственная надежда, что человечество не будет вскоре уничтожено или порабощено ИИ - это добрые инопланетяне, которые контроллируют человечество и сумеют вовремя уничтожить сумасшедших учёных реально приблизившихся к созданию враждебного человеку ИИ.

Чтобы не привлекать к себе внимание инопланетян и не пугать людей, лучше переименовать тему как "Разработка макета многопроцессорной системы с целью проверки работоспособности такой архитектуры на примере моделирования разума земляного червяка".

Как видно, УПЭ это просто традиционный компьютер в который добавлена периферийная плата для сопряжения с 64-мя ПЭ. Из любительских машин тут подходит ИРИША и ОРИОН (может и другие, но про них я не в курсе), а из промышленных - любой PC со слотами ISA (с ними проще расширять). ОРИОН имеет и монитор, и дисковод, и ИРПР (т.е просто адаптер принтера), и стык С2 (т.е последовательный интерфейс) в ОРИОН тоже не раз ставили.

ИРИША тоже подходит (и даже лучше, т.к шрифт читабельнее и конструктив для расширения удобнее). Последовательный и паралл-ный интерфейсы у ИРИШИ уже есть. Монитор в ПЗУ у ИРИШИ тоже есть. Для удовлетворения остальных пунктов спецификации, остаётся добавить к ИРИШЕ РК-КНГМД (КНГМД на ВГ93 тоже можно, но это потребует установки и ПДП, т.к ИРИША сама не тянет столь высокую скорость обмена) и плату расширения ОЗУ (чтобы поиметь эл.диск из ОЗУ).

Так что первым шагом по теме у Вас должно стать получение работающей ИРИШИ в нужном варианте. А в этом ваши интересы совпадают с интересами людей.

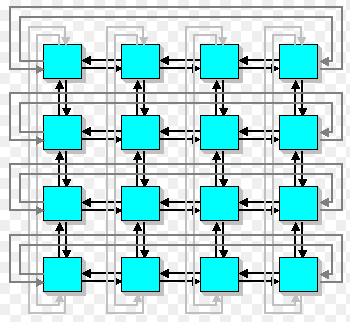

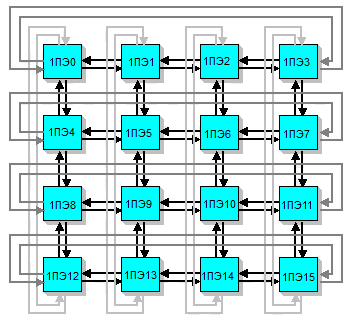

Архитектуру этого изделия можно охарактеризовать как обычный компьютер, к которому подключен макет простейшей нейронной сети на 64-х МП-ядрах. Эта сеть образована 8-ю модулями по 8 соединённых друг с другом МП-ядер. Кстати, непонятно почему у Вас УПЭ имеет лишь 32 связи с ПЭ, а не 64 (это значит, что связь лишь с каждым вторым ПЭ). А зачем это? Тогда уж логичнее и на УПЭ иметь не 32, а всего 8 связей, чтобы иметь связь с одним (главным) ПЭ в каждом модуле из 8-ми ПЭ.

Кроме того, если Вы для каждой связи будете использовать один порт из ВВ55, перестраивая его по ходу дела в обе стороны, это чревато конфликтами выходов ППА и программно сложнее, чем тратить два порта - один всегда на ввод, второй всегда на вывод, а третий для передачи сигналов управления (4 IN и 4 OUT). При этом понадобится всего лишь 65*8=520 ППА ВВ55. Что Вас, как любителя гигантомании должно очень радовать.

По поводу того, что единая шина обмена между ПЭ Вам не подходит. Вот как раз это правильное решение. Раз используются модули по 8 ПЭ. Видимо, именно ради общей шины это и сделано, а Вы просто не поняли и запланировали иметь полные перекрёстные связи для 65 блоков, что составляет 65*64=4160 (сомневаюсь, что Вы ответите, что столько ВВ55 Вы уже тоже купили). Когда идёт обмен в одном модуле из 8-ми ПЭ, то обмену 7-ми остальных модулей друг с другом это не мешает.

Но разумнее последовательный интерфейс (ведь это всё-равно лишь макет для проверки концепции и скорость не важна). Это по крайней мере реализуемо. При ВВ55 надо ещё формировать упр.сигналы, а в ВВ51 они уже внутри. В каждом ВВ51 три канала. Причем, даже не обязательно тратиться на килограмм ВВ51, т.к грамотно выбрав CPU программно формируемым последовательным интерфейсом достигается та же скорость.

И если уж серъёзно подходить к делу (а не ради пустой болтовни), то ПЭ надо делать на Z80, а ещё лучше на микроконтроллере с внутренним ОЗУ, ПЗУ, портами (и на крошечной платке, которых, по-крайней мере, реально спаять 64 штуки за несколько лет). Хотя я очень сомневаюсь, что у Вас хватит энтузиазма реализовать хотя бы несколько процентов из планируемого. За 7 лет Вы сделали лишь одну платку типового МП-контроллера, причём громоздкую и из неоптимальных деталей. С такими быстрыми темпами уже через 10 тысяч лет изготовление этого изделия будет успешно завершено. Даже на в сотни раз менее ёмкие проекты даже самым фанатичным людям не хватало энтузиазма.

Вот как я понял должно работать такое изделие (искусственный разум земляного червяка).

Главный компьютер УПЭ рассылает задачи 8-ми вычислительным модулям (каждый из них содержит 8 ПЭ). Передача делается только главному ПЭ в модуле (а уж он сам может распоряжаться остальными 7-ю ПЭ в данном модуле). При этом для каждого ПЭ требуется написать простой ROM-BIOS, что является просто процедурой приёма и запуска файла от УПЭ, затем очень сложную основную программу ИИ для УПЭ и программы, выполняющие типовые задачи в ПЭ, которые УПЭ пересылает на ПЭ, а они по их завершении отсылают в УПЭ результат.

Интеллект земляного червяка можно будет смоделировать и отладить подключив к УПЭ ещё несколько тысяч датчиков (по счастью червяк не имеет глаз, он воспринимает только тактильную информацию, температуру, влажность, вкус пищи и т.п), которые подключаются к ЭВМ имитирующей среду (т.е разные препятствия на пути в виде камней, пищу воду, кротов пожирающих червей и т.п). Моделируемый червяк сможет обучаться накапливая информацию в своей базе данных (если столь мизерного объёма памяти хватит). Программа искусственного разума червяка будет очень сложна и без помощи сотни программистов её не написать.

PS. Если зациклены именно на КР580, то сократить число деталей в контроллерах ПЭ Вам поможет вот эта статья.

Прорыв в науке и технике часто делают те, кто в отличие от всех остальных не знает, что что-то сделать нельзя, потому сдуру и начинают это пытаться сделать. По счастью в данном случае есть обоснованная надежда, что задуманное автором нереализуемо и человечество погибнет не от этого изделия.

Объявленной целью этого проекта является создание искусственного разума (ИИ). Слава Богу, что это невозможно сделать силами и средствами, которыми располагает автор (иначе ИИ уже давно бы уничтожил человечество). Но уже давно пора приравнять любые попытки разработать ИИ к преступлениям против человечества и наказывать более жестоко, чем за торговлю наркотиками и оружием.

Единственная надежда, что человечество не будет вскоре уничтожено или порабощено ИИ - это добрые инопланетяне, которые контроллируют человечество и сумеют вовремя уничтожить сумасшедших учёных реально приблизившихся к созданию враждебного человеку ИИ.

Чтобы не привлекать к себе внимание инопланетян и не пугать людей, лучше переименовать тему как "Разработка макета многопроцессорной системы с целью проверки работоспособности такой архитектуры на примере моделирования разума земляного червяка".

Вот это уже тема которая людей заинтересует (в то время как разработка ИИ никому неинтересна).Viktor2312 пишет:УПЭ... там нужен вывод на дисплей... клава, монитор, электронные диски и остальное по мелочи, типа стык С2, интерфейс ИРПР, КНГМД... возможно даже лучше сначала сделать УПЭ, а потом под него модернизировать ПЭ

Как видно, УПЭ это просто традиционный компьютер в который добавлена периферийная плата для сопряжения с 64-мя ПЭ. Из любительских машин тут подходит ИРИША и ОРИОН (может и другие, но про них я не в курсе), а из промышленных - любой PC со слотами ISA (с ними проще расширять). ОРИОН имеет и монитор, и дисковод, и ИРПР (т.е просто адаптер принтера), и стык С2 (т.е последовательный интерфейс) в ОРИОН тоже не раз ставили.

ИРИША тоже подходит (и даже лучше, т.к шрифт читабельнее и конструктив для расширения удобнее). Последовательный и паралл-ный интерфейсы у ИРИШИ уже есть. Монитор в ПЗУ у ИРИШИ тоже есть. Для удовлетворения остальных пунктов спецификации, остаётся добавить к ИРИШЕ РК-КНГМД (КНГМД на ВГ93 тоже можно, но это потребует установки и ПДП, т.к ИРИША сама не тянет столь высокую скорость обмена) и плату расширения ОЗУ (чтобы поиметь эл.диск из ОЗУ).

Так что первым шагом по теме у Вас должно стать получение работающей ИРИШИ в нужном варианте. А в этом ваши интересы совпадают с интересами людей.

Архитектуру этого изделия можно охарактеризовать как обычный компьютер, к которому подключен макет простейшей нейронной сети на 64-х МП-ядрах. Эта сеть образована 8-ю модулями по 8 соединённых друг с другом МП-ядер. Кстати, непонятно почему у Вас УПЭ имеет лишь 32 связи с ПЭ, а не 64 (это значит, что связь лишь с каждым вторым ПЭ). А зачем это? Тогда уж логичнее и на УПЭ иметь не 32, а всего 8 связей, чтобы иметь связь с одним (главным) ПЭ в каждом модуле из 8-ми ПЭ.

Кроме того, если Вы для каждой связи будете использовать один порт из ВВ55, перестраивая его по ходу дела в обе стороны, это чревато конфликтами выходов ППА и программно сложнее, чем тратить два порта - один всегда на ввод, второй всегда на вывод, а третий для передачи сигналов управления (4 IN и 4 OUT). При этом понадобится всего лишь 65*8=520 ППА ВВ55. Что Вас, как любителя гигантомании должно очень радовать.

По поводу того, что единая шина обмена между ПЭ Вам не подходит. Вот как раз это правильное решение. Раз используются модули по 8 ПЭ. Видимо, именно ради общей шины это и сделано, а Вы просто не поняли и запланировали иметь полные перекрёстные связи для 65 блоков, что составляет 65*64=4160 (сомневаюсь, что Вы ответите, что столько ВВ55 Вы уже тоже купили). Когда идёт обмен в одном модуле из 8-ми ПЭ, то обмену 7-ми остальных модулей друг с другом это не мешает.

Но разумнее последовательный интерфейс (ведь это всё-равно лишь макет для проверки концепции и скорость не важна). Это по крайней мере реализуемо. При ВВ55 надо ещё формировать упр.сигналы, а в ВВ51 они уже внутри. В каждом ВВ51 три канала. Причем, даже не обязательно тратиться на килограмм ВВ51, т.к грамотно выбрав CPU программно формируемым последовательным интерфейсом достигается та же скорость.

И если уж серъёзно подходить к делу (а не ради пустой болтовни), то ПЭ надо делать на Z80, а ещё лучше на микроконтроллере с внутренним ОЗУ, ПЗУ, портами (и на крошечной платке, которых, по-крайней мере, реально спаять 64 штуки за несколько лет). Хотя я очень сомневаюсь, что у Вас хватит энтузиазма реализовать хотя бы несколько процентов из планируемого. За 7 лет Вы сделали лишь одну платку типового МП-контроллера, причём громоздкую и из неоптимальных деталей. С такими быстрыми темпами уже через 10 тысяч лет изготовление этого изделия будет успешно завершено. Даже на в сотни раз менее ёмкие проекты даже самым фанатичным людям не хватало энтузиазма.

Вот как я понял должно работать такое изделие (искусственный разум земляного червяка).

Главный компьютер УПЭ рассылает задачи 8-ми вычислительным модулям (каждый из них содержит 8 ПЭ). Передача делается только главному ПЭ в модуле (а уж он сам может распоряжаться остальными 7-ю ПЭ в данном модуле). При этом для каждого ПЭ требуется написать простой ROM-BIOS, что является просто процедурой приёма и запуска файла от УПЭ, затем очень сложную основную программу ИИ для УПЭ и программы, выполняющие типовые задачи в ПЭ, которые УПЭ пересылает на ПЭ, а они по их завершении отсылают в УПЭ результат.

Интеллект земляного червяка можно будет смоделировать и отладить подключив к УПЭ ещё несколько тысяч датчиков (по счастью червяк не имеет глаз, он воспринимает только тактильную информацию, температуру, влажность, вкус пищи и т.п), которые подключаются к ЭВМ имитирующей среду (т.е разные препятствия на пути в виде камней, пищу воду, кротов пожирающих червей и т.п). Моделируемый червяк сможет обучаться накапливая информацию в своей базе данных (если столь мизерного объёма памяти хватит). Программа искусственного разума червяка будет очень сложна и без помощи сотни программистов её не написать.

PS. Если зациклены именно на КР580, то сократить число деталей в контроллерах ПЭ Вам поможет вот эта статья.

Последний раз редактировалось: barsik (Вт Мар 19 2019, 18:54), всего редактировалось 1 раз(а) (Обоснование : исправил результат умножения 65 на 8)

barsik- Ветеран

- Сообщения : 1032

Дата регистрации : 2016-11-10

Откуда : Россия

Re: Разработка, сборка, наладка ВМИР-1.

Re: Разработка, сборка, наладка ВМИР-1.

3

Объявленной целью этого проекта является создание искусственного разума (ИИ).

Нет, не ИИ, а ИР, а точнее ВМИР - вычислительная машина искусственного разума, ИИ входит в состав ИР как маленький один из блочков.

Слава Богу

Нет, бога нет !

Но уже давно пора приравнять любые попытки разработать ИИ к преступлениям против человечества и наказывать более жестоко, чем за торговлю наркотиками и оружием.

Нет, тех кто такое говорит, нужно наказывать, очень жестоко...

Единственная надежда, что человечество не будет вскоре уничтожено или порабощено ИИ - это добрые инопланетяне, которые контроллируют человечество и сумеют вовремя уничтожить сумасшедших учёных реально приблизившихся к созданию враждебного человеку ИИ.

Вот тут хорошо выкладывать видео с машинами которые ездиют по улицам, а водителей в них нет, хотя это и не ИИ, и уж тем более не ИР, но не буду, слишком объёмны эти видео по занимаемому месту в посте.

Чтобы не привлекать к себе внимание инопланетян и не пугать людей, лучше переименовать тему как "Разработка макета многопроцессорной системы с целью проверки работоспособности такой архитектуры на примере моделирования разума земляного червяка".

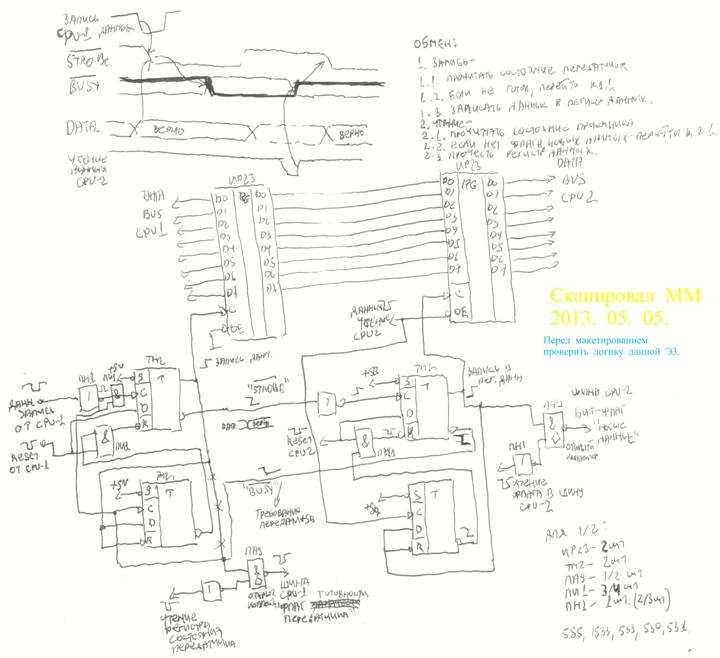

Ничего, переживут, ну а чтобы понятнее было, я её сделаю, но это будет как один нейрончик, но в удобоваримой форме, тут лучше будет посмотреть на фрактал и суть станет более понятной, ну и не забываем, что всё легко переносится в ПЛИС, при желании... Надеюсь словоблидия на этом закончатся, если нет, я уже писал, могу хоть по 1000 страниц писать мути, но это мало интересно, лучше больше практики (параллельный двунаправленный порт на КР580ВВ55А), у меня есть манускрипт от ММ, на рассыпухе, но я пока не хотел бы заниматься его расшифровкой или мутить на логике порты, мне нравится идея, да хоть 7 шт. ППА, но если получится уменьшить их количество в ПЭ, было бы отлично.

Вот это уже тема которая людей заинтересует (в то время как разработка ИИ никому неинтересна).

Вот это говорение за всех, меня всегда вымораживало, от куда вы можите знать кому и что интересно, вот мне ВМИР интересен. Прекращайте говорить за всех, постарайтесь сосредоточиться на себе.

Как видно, УПЭ это просто традиционный компьютер в который добавлена периферийная плата для сопряжения с 64-мя ПЭ.

С 32 ПЭ. С первой решёткой состоящей из 16 ПЭ и с 4-й решёткой, так же состоящей из 16 ПЭ.

Из любительских машин .... а из промышленных ...

Только хардкор, только система с нуля, ну а что там сложного, Проц с обвязкой, ПЗУ, ОЗУ, контроллер дисплея и 32 ИРПР Эл. диск, клава вот по сути и весь УПЭ, но тут у меня есть проблема в реализации, хотя хотелось бы обойтись чисто КР580 микропроцессорным комплектом. В игры играть не требуется, поэтому, этого будет достаточно -> ТГ КР580ГФ24, МП КР580ВМ80А, БА 3 х К155ЛП10, СК КР580ВК28, ПЗУ 2 х К573РФ2, ОЗУ 8 х КР565РУ5Г+обвязка, КП КР580ВН59, КР580ВГ75, клава КР580ВВ79 и т. д.

Так что первым шагом по теме у Вас должно стать получение работающей ИРИШИ в нужном варианте.

Это тупик, мне не туда, выше написал, система с нуля, по сути к ПЭ нужно добавить вывод на ЭЛТ и клаву, и подбавить портов с 7 до 32-х. Больше по сути ничего и не нужно.

А в этом ваши интересы совпадают с интересами людей.

Вы проводили социологический опрос? Сколько людей было опрошено? Нет, не проводили... Тогда говорите за себя, что тут совпадение максимум с вашими интересами...

Кстати, непонятно почему у Вас УПЭ имеет лишь 32 связи с ПЭ, а не 64 (это значит, что связь лишь с каждым вторым ПЭ). А зачем это?

Куб можно разбить на 4 составляющие 1-я (16 ПЭ) внешняя, 2-я и 3-я (16 ПЭ + 16 ПЭ) внутренние и 4-я (16 ПЭ) внешняя, достаточно связи только с внешними.

Эта сеть образована 8-ю модулями по 8 соединённых друг с другом МП-ядер.

Как-то витиевато написано, 1 матрица 4 х 4 ПЭ (16 ПЭ) за ней ещё три таких же:

Тогда уж логичнее и на УПЭ иметь не 32, а всего 8 связей, чтобы иметь связь с одним (главным) ПЭ в каждом модуле из 8-ми ПЭ.

Нет, 16 спереди и 16 сзади, это так можно рассмотреть.

Кроме того, если Вы для каждой связи будете использовать один порт из ВВ55, перестраивая его по ходу дела в обе стороны, это чревато конфликтами выходов ППА и программно сложнее, чем тратить два порта - один всегда на ввод, второй всегда на вывод, а третий для передачи сигналов управления (4 IN и 4 OUT). При этом понадобится всего лишь 65*8=440 ППА ВВ55. Что Вас, как любителя гигантомании должно очень радовать.

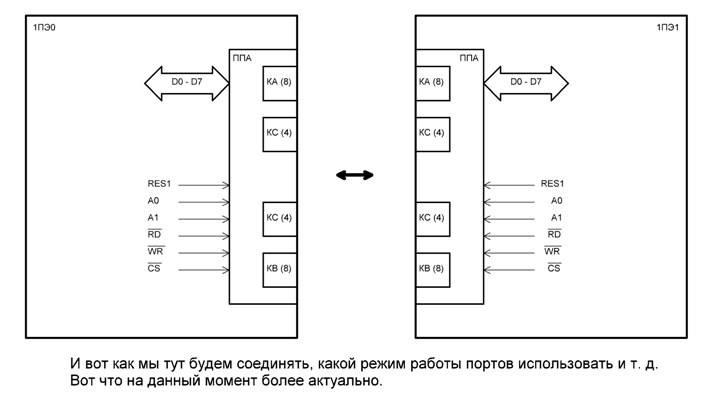

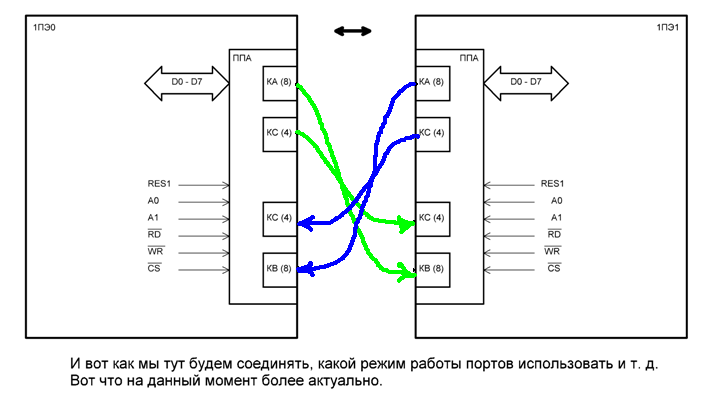

Если я правильно понял, то у нас получается, в ПЭ1 стоит 7 ППА, каждый ППА как известно имеет три порта A, B, C мы используем порт А для вывода, порт В для ввода и порт С для 4 и 4 сигналы управления. Итого 7 микросхем ППА в каждом ПЭ, всего в кубе 64 ПЭ, итого 64 * 7 = 448 микросхем ППА. Приемлемо. Дайте мне схемное решение и описание, а то вот именно с этим я что-то встал в ступор и никак не могу продвинуться дальше.

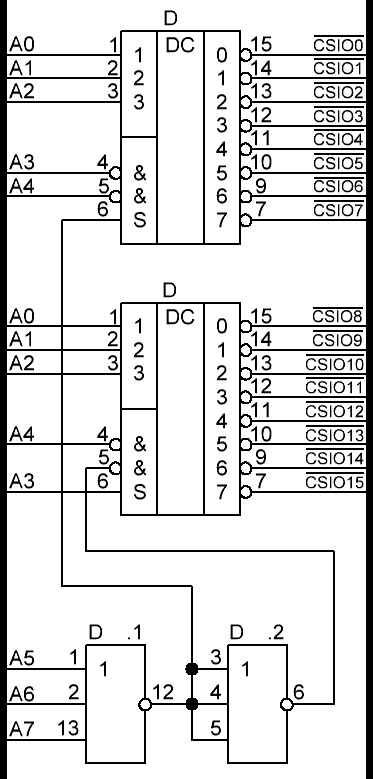

Тут я вас немного ввел в заблуждение, так как либо делать два вида ПЭ, одни имеют 7 портов, внешние и 6 внутренние, но для идентичности всех ПЭ, это не желательно, тогда в итоге получается, что все ПЭ будут иметь связь с УПЭ, а это избыточно. Избыточно по "железу" но желательно с точки зрения реализации. Тогда да, УПЭ лучше делать сразу на 64 порта, чтобы иметь связь с каждым ПЭ. Итого 448 портов в кубе и 64 в УПЭ итого 512, вот картина и сложилась и число правильное. Так что всё верно вы написали, 64 ПЭ, у каждого 7 портов, 6 для связи с соседними ПЭ внутри куба и 1 порт для связи с УПЭ, а УПЭ в свою очередь имеет 64 порта, всего система имеет 512 портов или 512 микросхем ППА. Отлично, осталось дело за малым, схемная реализация и назначение адресов портам.

На данный момент задача №1. Вычертить мне схему обновлённого ПЭ, содержащего контроллер прерываний и 7 параллельных портов ввода вывода. Как только это будет сделано, можно приступить к разработке печатной платы под стандартный корпус.

По поводу того, что единая шина обмена между ПЭ Вам не подходит. Вот как раз это правильное решение. Раз используются модули по 8 ПЭ. Видимо, именно ради общей шины это и сделано, а Вы просто не поняли и запланировали иметь полные перекрёстные связи для 65 блоков, что составляет 65*64=4160 (сомневаюсь, что Вы ответите, что столько ВВ55 Вы уже тоже купили). Когда идёт обмен в одном модуле из 8-ми ПЭ, то обмену 7-ми остальных модулей друг с другом это не мешает.

Какая-то околесица. есть матрица 4 х 4 ПЭ в ней 16 ПЭ, каждый ПЭ связан только с соседними ПЭ его окружающими, 6 портов и одна связь с УПЭ, итого всего 7 портов в каждом ПЭ. Каждый ПЭ может стать просто передатчиком, без осуществления каких либо вычислений. Правильная нумерация ПЭ такая 1ПЭ0...1ПЭ15, это первая матрица из 16 ПЭ, вы её видите на рисунке выше, можите их там пронумеровать слева направо и сверну вниз, следующая матрица, стоящая за первой, так же 4 х 4 ПЭ всего 16 ПЭ и в ней ПЭ имеют следующую нумерацию 2ПЭ0...2ПЭ15 и т. д. Всего 512 портов.

Но разумнее последовательный интерфейс

Дежавю, нет, и не начинайте, в прошлый раз на zxpk пол года ушло на мятие кала по этому поводу, лет 7 назад, мой ответ по прежнему НЕТ. Только параллельная передача данных.

И если уж серъёзно подходить к делу (а не ради пустой болтовни), то ПЭ надо делать на Z80

Вот точно, даже не буду начинать болтавню, уже писал, только КР580, остальное не интересно.

Хотя я очень сомневаюсь, что у Вас хватит энтузиазма реализовать хотя бы несколько процентов из планируемого. За 7 лет Вы сделали лишь одну платку типового МП-контроллера, причём громоздкую и из неоптимальных деталей. С такими быстрыми темпами уже через 10 тысяч лет изготовление этого изделия будет успешно завершено. Даже на в сотни раз менее ёмкие проекты даже самым фанатичным людям не хватало энтузиазма.

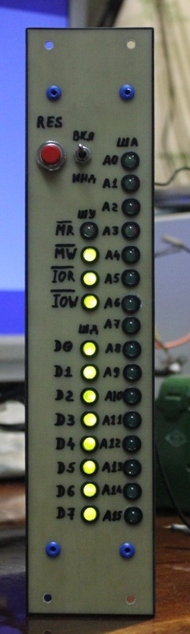

Я уперся тогда в параллельный порт, потом как писал уже был переезд и вообще электроника вся была в коробках и заброшена, даже компа не было, потом проблемы с работой были, заброшено было по причинам: 1. не получилось с нахрапу преодолеть параллельный порт, сделать можно было, но не был уверен в том что будет работать, и поэтому не хотелось ставить на заводскую плату. 2 переезды, работа, подавленное состояние, что всё по жизни идёт не так как хотелось. Ну и главное, этой платы ПЭ и требовалась 1 шт. Так как она имеет СПИП и индикацию шин, это первый макет с пошагивалкой, индикацией и конечный ПЭ не должен иметь всего этого лишнего, что занимает пол платы и то с расположенными элементами с увеличенным шагом в 2 раза.

А элементы как раз таки оптимальные, и идеальные, да и вообще самые лучшие, но это моё мнение, никому его не навязываю, каждый может использовать те, которые ему нравятся, я же буду использовать те, что нравятся мне и которые я считаю отличными, а для меня это КР580, К565, К573, К155, К555 и может ещё что-то по мелочи.

Вот как я понял должно работать такое изделие (искусственный разум земляного червяка).

Думайте что хотите, меня это мало заботит, меня заботят практические проблемы, реализация параллельного порта и вычерчивание окончательной схемы, обновлённого ПЭ. Потом разработка печатной платы, заказ 6 шт. (мин. заказ) изготовление 2 образцов и начало тестирования и если всё нормально, то можно собирать все 64 ПЭ и параллельно разрабатывать УПЭ.

Главный компьютер УПЭ рассылает задачи 8-ми вычислительным модулям (каждый из них содержит 8 ПЭ).

Нет, связь будет со всеми 64 ПЭ. И он может отправить код для допустим 1ПЭ7 содержащий всего задание для 1ПЭ7 разослать задания для 2ПЭ7, 1ПЭ8 и т. д. Количество вложенности заданий может быть и больше.

Передача делается только главному ПЭ в модуле (а уж он сам может распоряжаться остальными 7-ю ПЭ в данном модуле).

Нет, каждый ПЭ независим и самостоятелен, может как получать задание от УПЭ, так и выполнять его, в том числе раздавать задания соседним ПЭ или просто передавать информацию к соседнему ПЭ, если например 1ПЭ5 должен передать результат в 1ПЭ7, то ему не обязательно связываться для этого с УПЭ и тратить его драгоценное время, он может это сделать через 1ПЭ6.

Примерно, близко и похоже с небольшими оговорками, но при этом с большими последствиями, только не BIOS, а БСВВ - базовая система ввода-вывода.При этом для каждого ПЭ требуется написать простой ROM-BIOS, что является просто процедурой приёма и запуска файла от УПЭ, затем очень сложную основную программу ИИ для УПЭ и программы, выполняющие типовые задачи в ПЭ, которые УПЭ пересылает на ПЭ, а они по их завершении отсылают в УПЭ результат.

Интеллект земляного червяка можно будет смоделировать и отладить подключив к УПЭ ещё несколько тысяч датчиков (по счастью червяк не имеет глаз, он воспринимает только тактильную информацию, температуру, влажность, вкус пищи и т.п), которые подключаются к ЭВМ имитирующей среду (т.е разные препятствия на пути в виде камней, пищу воду, кротов пожирающих червей и т.п). Моделируемый червяк сможет обучаться накапливая информацию в своей базе данных (если столь мизерного объёма памяти хватит). Программа искусственного разума червяка будет очень сложна и без помощи сотни программистов её не написать.

Вот и хорошо, что мне не нужен земляной червяк...

МНЕ НУЖЕН ПАРАЛЛЕЛЬНЫЙ ПОРТ НА КР580ВВ55А АААААА....

PS. Если зациклены именно на КР580, то сократить число деталей в контроллерах ПЭ Вам поможет

Не хочу сократить, меня устраивает моя система, главное, чтобы работало, не допустить ошибок при проектировании, которые перейдут на заводскую плату, и в итоге после отладке приведут к повторному заказу новой платы, это потеря 3...5 месяцев и оплата повторная подготовки к производству...

Хух... как вроде всё прокоментировал, надеюсь понятно изложил свою позицию, она во чуть выше заглавными буквами написана, что требуется на данный момент, чтобы всё опять не встало, хотя в крайнем случае, почитаю про ППА ещё раз в книжечках и тупо от туда влуплю схему, как крайний вариант, жаль конечно потери будет 5 месяцев, но ничего...

Последний раз редактировалось: Viktor2312 (Вт Мар 19 2019, 19:32), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Разработка, сборка, наладка ВМИР-1.

Re: Разработка, сборка, наладка ВМИР-1.

4

.

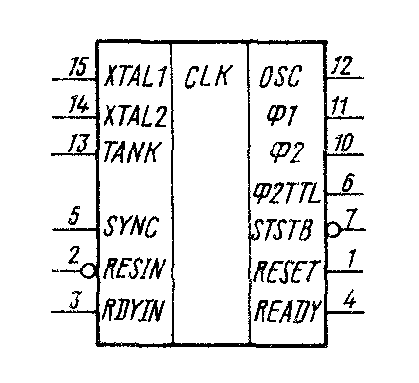

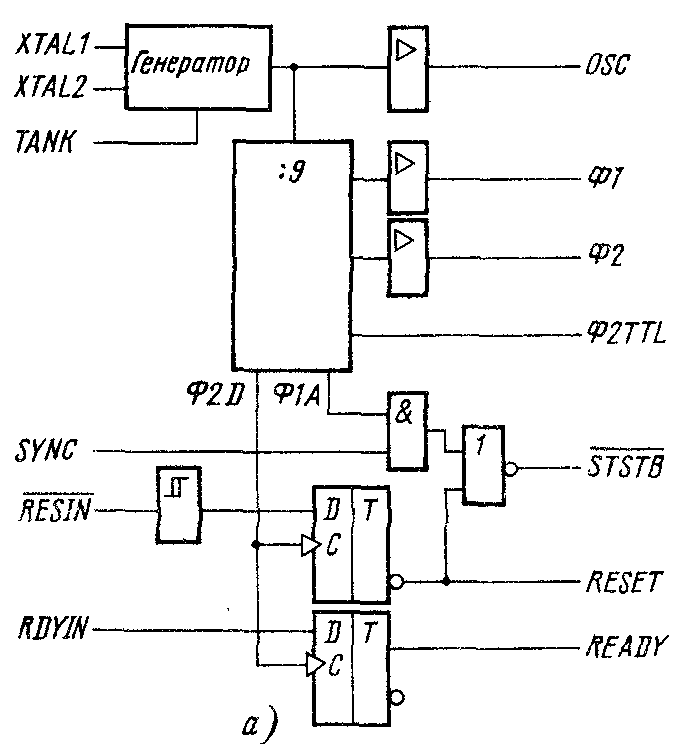

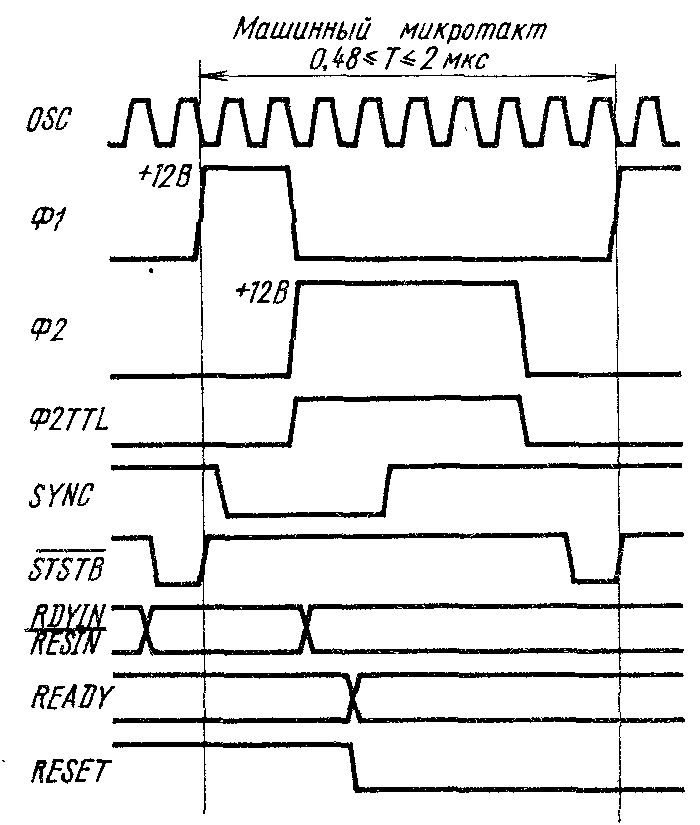

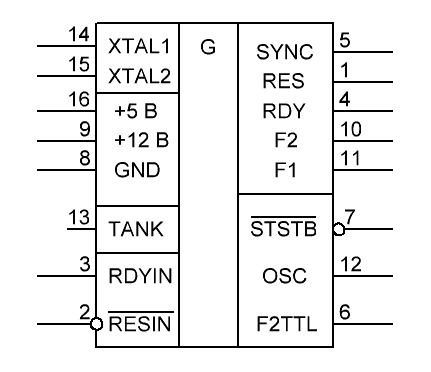

____Выводы XTAL1 и XTAL2 служат для подключения кварцевого резонатора, а вывод TANK - для выбора его гармоники. Выход генератора буферизирован и выведен на линию OSC так, чтобы другие устройства микропроцессорной системы могли его использовать. Основой схемы является делитель на 9, поэтому частота кварцевого резонатора должна быть в 9 раз больше, чем частота следования импульсов Ф1, Ф2. Частота кварцевого резонатора определяется быстродействием микропроцессорной системы и лежит в пределах 4,5 - 22,5 МГц. При OSC = 22,5 МГц период следования синхроимпульсов Ф1 и Ф2 (длительность микротакта) 400 нс, что соответствует нижней границе диапазона, допустимого для микропроцессора КР580ВМ80А.

____В процессорных элементах (ПЭ) будет применяться кварцевый резонатор на частоту 18 МГц, соответственно длительность микротакта составляет 500 нс, а частота работы микропроцессора 2 МГц.

____В состав схемы КР580ГФ24 входят также логические цепи для генерации строба /STSTB (Status Strobe), синхронизации сигнала RDYIN (Ready Input) и формирования мощного выхода RESET, служащего для аппаратного сброса микропроцессорной системы в исходное состояние.

____На рисунке выше показаны временные диаграммы работы генератора тактовых импульсов.

____На данный момент подготовлен макрос для схемы, хотя его нужно чуть подправить, вывод инверсии у вывода 7, но это мелочи. В общим на данный момент, работа и применение тактового генератора, предельно ясна и его можно добавлять на схему, за исключением мелких нюансов, которые потом будут добавлены в данный пост.

____Чтобы выполнить функцию начальной установки микропроцессора, необходимо ко входу /RESIN подключить RC-цепочку. Наличие гистерезиса на входе /RESIN гарантирует быстрое переключение схемы в момент достижения порога переключения.

Генератор тактовых импульсов КР580ГФ24.

____Выводы XTAL1 и XTAL2 служат для подключения кварцевого резонатора, а вывод TANK - для выбора его гармоники. Выход генератора буферизирован и выведен на линию OSC так, чтобы другие устройства микропроцессорной системы могли его использовать. Основой схемы является делитель на 9, поэтому частота кварцевого резонатора должна быть в 9 раз больше, чем частота следования импульсов Ф1, Ф2. Частота кварцевого резонатора определяется быстродействием микропроцессорной системы и лежит в пределах 4,5 - 22,5 МГц. При OSC = 22,5 МГц период следования синхроимпульсов Ф1 и Ф2 (длительность микротакта) 400 нс, что соответствует нижней границе диапазона, допустимого для микропроцессора КР580ВМ80А.

____В процессорных элементах (ПЭ) будет применяться кварцевый резонатор на частоту 18 МГц, соответственно длительность микротакта составляет 500 нс, а частота работы микропроцессора 2 МГц.

____В состав схемы КР580ГФ24 входят также логические цепи для генерации строба /STSTB (Status Strobe), синхронизации сигнала RDYIN (Ready Input) и формирования мощного выхода RESET, служащего для аппаратного сброса микропроцессорной системы в исходное состояние.

____На рисунке выше показаны временные диаграммы работы генератора тактовых импульсов.

____На данный момент подготовлен макрос для схемы, хотя его нужно чуть подправить, вывод инверсии у вывода 7, но это мелочи. В общим на данный момент, работа и применение тактового генератора, предельно ясна и его можно добавлять на схему, за исключением мелких нюансов, которые потом будут добавлены в данный пост.

____Чтобы выполнить функцию начальной установки микропроцессора, необходимо ко входу /RESIN подключить RC-цепочку. Наличие гистерезиса на входе /RESIN гарантирует быстрое переключение схемы в момент достижения порога переключения.

Последний раз редактировалось: Viktor2312 (Ср Мар 20 2019, 16:52), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

5

Бред. Значит Вы чокнулись ещё более, чем можно думать читая о ВМИР.Viktor2312 пишет:Объявленной целью этого проекта является создание искусственного разума (ИИ).

Нет, не ИИ, а ИР

Искусственный интеллект — система вычислительных технологий, действующая по образу человеческого мышления. Обучаемый механизм, который может выполнять как простейшие задачи, так и принимать решения, основанные на сложном анализе ситуации.

Разум это продукт эволюции, точнее его может создать эволюция, Бог или более высокий разум. А человек может создать только ИИ. А вот сам ИИ начав развиваться теоретически может стать разумным. Но ещё раньше он придёт к естественному и справедливому выводу, что человечество это вредная плесень на теле планеты подлежащая уничтожению.

Термин «искусственный интеллект» общепринят. В 1969 году международная конференция по ИИ узаконила именно этот термин. Человек в этой реальности неспособен на создание искусственного разума (ИР), учитывая, что процессы в биологическом разуме мало изучены и скорее всего никогда не будут изучены достаточно хорошо. Поэтому всякого учёного готорый заикается о ИР следует считать малограмотным идиотом.

Разум возникает в чём-то живом. И потому разум отличается от интелекта наличием чувств. Таким образом получается, что Вы собираетесь создать ИИ и затем снабдить его чувствами.

Вы заявляете, что делаете ИР. Ну так не обманывайте людей, пишите, что пытаетесь смоделировать один из нейронов мозга, которых в мозге миллиарды. Нейрон это не мозг. И непонятно зачем нужен один крошечный блочок от ИИ. На нём даже что-то проверить не удастся. Да и кому это надо? Вы же не учёный.ИИ входит в состав ИР как маленький один из блочков

А выхлоп от вашего изделия, если бы оно прямо сегодня стояло бы у Вас на столе - абсолютно нулевой. Пользу от него можно получить, если его наоборот распаять и продать на детали и КМ-ки. Или Вы хотите сделать изделие "под ретро" и продать его за $100К в американский технический музей, как советсткую разработку ИИ. Это по крайней мере объяснило бы ваше пристрастие к советским деталям.

И вообще ИИ и ИР это не железо и даже не нейронная сеть, о которой Вы где-то вычитали и решили, что сможете повторить. Это в первую очередь программа. И сложности создания железа и создания программы соотносятся как один к миллиону. Процессоры с гигантской производительностью и невообразимым объёмом памяти уже есть, а вот программу никак написать не могут.

Потому человека, который делает на кухонном столе даже не ИИ, а ИР можно считать или полным идиотом или чокнувшимся. Я не хочу никого обидеть, лишь озвучиваю то, что думает любой здравомыслящий человек читая о ВМИР.

Что-то невразумительное. Хотелось бы, чтобы Вы излагали свои мысли понятно. Как может быть манускрипт на рассыпухе, к тому же зашифрованным, а MM ведь увлекается DEC-процессорами, не знал, что он написал манускрипт о Intel-периферии.у меня есть манускрипт от ММ, на рассыпухе, но я пока не хотел бы заниматься его расшифровкой

Я вообще не понимаю в чём проблема.7 шт. ППА, но если получится уменьшить их количество в ПЭ, было бы отлично

Можно и не 7 портов, а 5. Тогда нужна двунаправленность, что немного более сложное программирование, более хитрый протокол и риск выхода из строя ППА, когда они оба на вывод и конфликтуют сигналами. Этого легко избежать соединяя ноги портов через резистор 300 Ом. Входы ППА высокоомные (т.к nMOP) и резистор сигналам не повредит, но защитит от выгорания.

Так в чём проблема? Уточните. В том, что Вы не можете написать программу параллельного интерфейса? Так надо было так и сказать. Тут Вам любой, кто выучил систему команд CPU с удовольствием поможет. Или не можете придумать протокол диалога между ПЭ? Т.е как они должны между собой договариваться о том, кто из них будет передатчиком, кто приёмником? Или в чём-то ещё?

Вы проводили социологический опрос? Сколько людей было опрошено? Нет, не проводили... Тогда говорите за себя, что тут совпадение максимум с вашими интересами

Извиняюсь, но уже не могу это выдерживать. "От куда" - слитно. "Можите" - через Е. Тут большинство молодёжи малограмотные (т.к только в советской школе хорошо учили), но уж такие ляпы и главное постоянно...Вот это говорение за всех, меня всегда вымораживало, от куда вы можите знать кому и что интересно, вот мне ВМИР интересен

Не надо проводить опросы населения, чтобы понять, что ВМИР никому неинтересен, т.к все сразу понимают, что это просто глупость с огромной затратой сил и средств. А то, что ИРИША или другие ретро машины людям интересны тоже ясно, что видно по тематическим форумам.

Какая же это система с нуля? Это РК86 с буферами и ВВ79 (плюс килограмм ППА). Только ВТ57 забыли. Что за обвязка к РУ5? Думаю, что имеете ввиду Ваш узел регенерации, забыв, что если есть ВГ75+ВТ57, то это не надо.только система с нуля... это ГФ24, ВМ80, БА 3 х К155ЛП10, ВК28, ПЗУ 2 х К573РФ2, ОЗУ 8 х РУ5 + обвязка, ВН59, ВГ75, ВВ79

На кой хрен Вам сдался РК. Сделайте плату текстового адаптера к ИРИШЕ и это будет на порядок удобнее и модульнее. И к тому же в строгом соответствии с Вашим требованием применения только советских деталей (работники музея не догадаются о новодельности).

ВВ79 это интересно. У меня он есть уже 30 лет. Всё хочу его куда-нибудь применить. Он идеально подходит для HEX-шалабушек (т.к он зараз обслуживает и клав-ру и HEX-индикаторы). В книге Рафикузамана "Микропроцессоры и проектирование МП систем" подробно и на примере показано как его применять. У ВВ79 ограничение на матрицу в 8*8, а если матрица корветовская или специалистовская, то нужны хитроумные примочки.

Дался Вам этот убогий генератор. Он жрёт как печка, а заменяется простейшей схемой (см.статью по ссылке в предыд.посте). Надо применять нормальные процессоры или контроллеры, у которых задающий генератор встроен внутрь кристалла. Например, 6802 или 6502.Генератор тактовых импульсов КР580ГФ24

barsik- Ветеран

- Сообщения : 1032

Дата регистрации : 2016-11-10

Откуда : Россия

Re: Разработка, сборка, наладка ВМИР-1.

Re: Разработка, сборка, наладка ВМИР-1.

6

Бред. Значит Вы чокнулись ещё более, чем можно думать читая о ВМИР.

Как я уже заметил вы легко других людей обвиняете в чём угодно, что они глупые, это я постоянно читаю в ваших постах, то что они сумасшедшие, но... Я считаю это всё от того, что вы сами признались, что вы на грани деменции.

Искусственный разум - это искусственная моделирующая установка, претендующая на сравнение с естественной (мозгом) по объёму переработки информации и по количеству этажей и дополнительных кодов-качеств.

Вот вам краткое определение, что такое ИР. Опять словоблудие и споры, я только так кратко могу ответить на эту часть, многое просто оставлю без комментарием.

Вы заявляете, что делаете ИР. Ну так не обманывайте людей, пишите, что пытаетесь смоделировать один из нейронов мозга, которых в мозге миллиарды. Нейрон это не мозг. И непонятно зачем нужен один крошечный блочок от ИИ. На нём даже что-то проверить не удастся. Да и кому это надо? Вы же не учёный.

Это называется: ...и смешалось всё в кучу, люди, лошади... Даже комментировать не буду.

А выхлоп от вашего изделия, если бы оно прямо сегодня стояло бы у Вас на столе - абсолютно нулевой. Пользу от него можно получить, если его наоборот распаять и продать на детали и КМ-ки. Или Вы хотите сделать изделие "под ретро" и продать его за $100К в американский технический музей, как советсткую разработку ИИ. Это по крайней мере объяснило бы ваше пристрастие к советским деталям.

Бред, бред, бред... Без комментариев.

Потому человека, который делает на кухонном столе даже не ИИ, а ИР можно считать или полным идиотом или чокнувшимся. Я не хочу никого обидеть, лишь озвучиваю то, что думает любой здравомыслящий человек читая о ВМИР.

Опять говорильня за всех, но хоть вашу позицию я понял, вы меня считаете сумасшедшим, хоть что-то прояснили, и то хорошо. Правда я на кухонном столе кушаю, а не делаю ИР, ну да ладно, собрались два, один на грани деменции, второй "можно считать или полным идиотом или чокнувшимся", весело живём, вот только время мне жалко, которое я сейчас трачу на эту писанину, вместо реальной работы над ВМИР, ну или отдыха, с вкусняшками и просмотром хорошего кинца...

Что-то невразумительное. Хотелось бы, чтобы Вы излагали свои мысли понятно. Как может быть манускрипт на рассыпухе, к тому же зашифрованным, а MM ведь увлекается DEC-процессорами, не знал, что он написал манускрипт о Intel-периферии.

Это не важно, забудьте, вы всё равно информацию неадекватно воспринимаете, просто попался под руку этот манускрипт, с времён когда я хотел сделать порт на рассыпухе, а не на КР580ВВ55А.

Так в чём проблема? Уточните. В том, что Вы не можете написать программу параллельного интерфейса? Так надо было так и сказать. Тут Вам любой, кто выучил систему команд CPU с удовольствием поможет. Или не можете придумать протокол диалога между ПЭ? Т.е как они должны между собой договариваться о том, кто из них будет передатчиком, кто приёмником? Или в чём-то ещё?

Примерно именно так. Я то примерно представляю, что да как сделать. Но общая картина не складывается. По сути примерно так, в ПЭ1 порт А настраивается на вывод, порт В на ввод и порт С используется для управляющих сигналов. В ПЭ2 всё то же самое. И соответственно пор А ПЭ1 соединяется с портом В ПЭ2 и наоборот порт А ПЭ2 соединяется с портом В ПЭ1, но пока общая картина не складывается, нужны детали и точная проработка нюансов. А так по сути да, в каждом ПЭ будет 7 портов, и соответственно 7 ППА и нужно их правильно развести и продумать сигналы управления, как это всё правильно соединять и программирование этого всего, для начала программирование РУС после включения и начальной инициализации и в последствии как их использовать уже при обмене, учитывая сигналы порта С. Ну и уложиться в стандартный 25 контактный разъём коих будет 7 шт. на задней стенке ПЭ.

Не надо проводить опросы населения, чтобы понять, что ВМИР никому неинтересен, т.к все сразу понимают, что это просто глупость с огромной затратой сил и средств. А то, что ИРИША или другие ретро машины людям интересны тоже ясно, что видно по тематическим форумам.

Ну а мне интересна ВМИР, и мало интересно, либо совсем не интересно всё остальное.

Извиняюсь, но уже не могу это выдерживать. "От куда" - слитно. "Можите" - через Е. Тут большинство молодёжи малограмотные (т.к только в советской школе хорошо учили), но уж такие ляпы и главное постоянно...

У меня по русскому всегда была 2+, то есть округляли до 3-, и писали уже 3, так что, мне можно...

Какая же это система с нуля? Это РК86 с буферами и ВВ79 (плюс килограмм ППА). Только ВТ57 забыли. Что за обвязка к РУ5? Думаю, что имеете ввиду Ваш узел регенерации, забыв, что если есть ВГ75+ВТ57, то это не надо.

Я так далеко не заглядываю, ВГ75 просто для примера привёл, по сути я уже описал, к обычному ПЭ нужно просто добавить клавиатуру и вывод на ЭЛТ, больше там особо ничего и не нужно, остальное всё мелочи, просто УВВ вешающиеся на порты.

Но сейчас лучше я сосредоточусь на ПЭ, довести схему до завершённого состояния. Разработать ПП и заказать для прототипа.

На кой хрен Вам сдался РК.

Вообще эпично, нет никакого РК и в помине, А КР580ВГ75 это вообщето универсальная микросхема для построения адаптера ЭЛТ. Но не стоит на ней зацикливаться, можно и на рассыпухе, желателен какой нибудь стандартный режим просто по графике, типа 640 х 480 и по тексту 80 х на сколько-то там, я с отображением графической и текстовой информации пока не дружу, как-то до меня пока не доходит это всё, а при слове спрайты и тайлы, у меня начинается лёгкое головокружение и подташнивание, но мне можно, я же того...

Поэтому пока графику и текст я не рассматриваю, только чистый ПЭ, а там по сути нужно только решить нужны ли прерывания и если да, то как их применить для ППА, ну и сами ППА соответственно, это основное.

ВВ79 это интересно. У меня он есть уже 30 лет. Всё хочу его куда-нибудь применить. Он идеально подходит для HEX-шалабушек (т.к он зараз обслуживает и клав-ру и HEX-индикаторы). В книге Рафикузамана "Микропроцессоры и проектирование МП систем" подробно и на примере показано как его применять. У ВВ79 ограничение на матрицу в 8*8, а если матрица корветовская или специалистовская, то нужны хитроумные примочки.

Вы думаете наизнанку, ну да ладно, просто когда эти микросхемы проектировали, или у нас выпускали, не было никаких Корветов, Специалистов, но радует, что возможно получится разобраться и приделать клавиатуру при помощи КР580ВВ79, как та часть, что для графики, так по мне она лишняя, но они независимы, что радует.

Дался Вам этот убогий генератор. Он жрёт как печка, а заменяется простейшей схемой (см.статью по ссылке в предыд.посте). Надо применять нормальные процессоры или контроллеры, у которых задающий генератор встроен внутрь кристалла. Например, 6802 или 6502.

Применяйте, но без меня, он у меня отлично работает и всё уже проверено на макете, зарекомендовал себя просто отлично, ну а по поводу питания, у меня нет проблем с эл. энергией и устройство предполагается стационарным.

Я уже писал ТГ + МП + ДА + СК + ПЗУ + ОЗУ

(КР580ГФ24 + КР580ВМ80А + 3 х К155ЛП10 + КР580ВК28 + 2 х К573РФ2 + КР565РУ5Г и схема регенерации),

вот оно основное ядро которое будет, и это факт, данность, это нужно просто понять, принять и осознать, и от этого плясать.

Расскажите мне лучше, что думаете по поводу конденсатора и резистора в схеме сброса. Если поставлю 4,7 мкФ и резистор 15 кОм, нормально будет? защитный диод там будет само собой, как и кнопка сброса.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

7

Нет такого, а в данном случае моё предположение абсолютно обосновано.Viktor2312 пишет:Как я уже заметил, вы легко других людей обвиняете в чём угодно, что они глупые, это я постоянно читаю в ваших постах... вы на грани деменции

Конечно в итоге, все кто проживёт достаточно долго станут слабоумными, т.е произойдёт плавная утрата памяти и сообразительности, хорошо ещё если так, - Альцгеймер ещё хуже. Но пока-то, я вполне нормально соображаю и в состоянии реально оценивать что-то и выражать свои мысли.

Вы обиделись, но исходя из той информации, что Вы предоставили, любой хоть немного интересующийся техникой, не может сделать иной вывод. Я уверен, что Вы и сами не понимаете, что хотите сделать и зачем Вам это надо. Уверен, Вы не сможете вразумительно объяснить зачем эта железяка Вам нужна и что даст.

Я прекрасно бы понял истинную одержимость идеей (говорят идея-бзик), даже если идея неверна и нереальна, но у Вас даже этого нет. Когда человек одержим и идёт к цели, он не капризничает, не фокусничает, а использует всё что можно, чтобы скорее (или хотя бы в обозримой перспективе) получить результат.

А сделать бессмысленную железяку, причём именно на серии 1974 года выпуска, это никак кроме как детской игрой в инженера-разработчика не назовёшь. Лучше бы Вы занялись изготовлением реплики СМ-1800.

Во-первых, это форум. Для того и предназначенный. Во-вторых, невозможно на всех тематических форумах найти другой более бессмысленный и бесполезный проект чем Ваш. Да и удивление. Мне (и опять-таки всем) хочется понять о чём речь.словоблудие и споры

Странные, необычные и с практической точки зрения бесполезные проекты бывают. Но в них есть идея и достигается результат. А Вы запланировали сделать что-то абсолютно бесполезное (главное, чтобы красивое, да?) и неспособное дать хоть какой-то результат.

Лучше бы Вы занялись изготовлением процессора на транзисторах КТ315. В России таких энтузиастов нет, но в мире империализма, где у людей килограммы денег и свободного времени, было с десяток подобных проектов. Но их можно хотя бы понять.

Человек поставил себе цель и сделал, получил реальный работающий результат и даже использовал свой самодельный процессор в собственной ЭВМ. Доказав тем самым, что главное идея, и что при утрате технологии микросхем, всё-равно можно будет делать клоны процессоров 6502 и PDP-8 на 3000 транзисторов. А что даёт и для чего годится ваше нагромождение железа?

Viktor2312 пишет:barsik пишет:не обманывайте людей

смешалось всё в кучу, люди, лошади

правильно так:

Земля тряслась — как наши груди;

Смешались в кучу кони, люди...

М.Ю.Лермонтов

Что смешалось в кучу в моём утверждении, что название темы неверное? Я лишь высказал совершенно справедливое мнение, что название темы не соответствует проекту, вводит читателя в заблуждение. Целью разработки является крошечный узел для ИИ (аналог нейрона в мозге) и это обьявляется компьютером искусственного разума. Трудно придумать бОльшую чушь.

Ваши тезисы были бы совершенно уместны в психбольнице, но в форуме, который читают компетентные люди интересующиеся компьютерами (и даже профессионалы) это реально похоже на полную "шизу".Опять говорильня за всех, но хоть вашу позицию я понял, вы меня считаете сумасшедшим

До чокнутого, т.е на самом деле одержимого идеей человека, Вы сильно не дотягиваете. Скорее это похоже на игру в разработчика. Похоже Вы решили освоить разработку изделий на МП-комплекте КР580 и где-то взяли нелепую мысль, что столь крошечная нейронная сеть что-то может. И внушили себе, что это Вам зачем-то надо.

Вот я и хотел узнать конечную цель проекта, зачем это надо и что это даёт (только не надо баек о разработке ИР и рассказов, что планируете выпускать в гараже роботов).

Не согласен. Приведите хоть один пример этого.вы всё равно информацию неадекватно воспринимаете

Глупо обижаться на правду. Другие вообще Вас игнорируют, не желая тратить время на чушь и не я первый говорю Вам, что данный проект полная чушь. Единственная польза от него это лишь изучение Вами проектирования МП-систем. Найдите хоть одного человека, кто думает об этом иначе. Потому, чтобы "спасти репутацию вашу и форума" я и хотел, чтобы Вы убрали всякое упоминание, что Вы разрабатываете ИР. С тем же успехом можно в названии темы указать, что автор темы не в себе.

Нюансы станут ясны, когда Вы поймёте как работает параллельный обмен, для чего надо самому написать интерфейс на ввод и на вывод. А вообще параллельный обмен между двумя ППА удобнее производить не в режиме 0, а в режимах 1 или 2. Тогда процессору не надо самому выдавать упр.сигналы. Раз надо много портов, то удобно сочетать режимы ППАв ПЭ1 порт А настраивается на вывод, порт В на ввод и порт С используется для управляющих сигналов. В ПЭ2 всё то же самое. И соответственно порт А ПЭ1 соединяется с портом В ПЭ2 и наоборот порт А ПЭ2 соединяется с портом В ПЭ1, но пока общая картина не складывается, нужны детали и точная проработка нюансов

Телевизор и CGA монитор не могут показать более 280 линий, для 480 линий растра нужен VGA-дисплей.желателен какой нибудь стандартный режим просто по графике, типа 640 х 480 и по тексту 80 х на сколько-то

Спрайты это маленькие, но целые картинки (в основном фигурки в разных фазах), а тайлы это или то, из чего крупная фигурка спрайт строится (т.е фрагменты спрайтов), или такие тайлы из которых рисуется пейзаж.при слове спрайты и тайлы, у меня начинается лёгкое головокружение и подташнивание

Я лишь упомянул, что если матрица превышает 8*8, то надо или ставить их две или придумывать какой-то хитрый трюк. Типа четный скан сканирует левую матрицу 8*8, нечётный скан - правую матрицу 8*8, а 8-й бит читается в МП-систему по входу Shift или Cntl. Но сам я такое не делал, может быть это и невозможно. У меня есть подозрение, что ВВ79 применялась в ПК/16 "Союз-Неон" и именно с трюком, т.к там у клавиш матрица 8*11.Viktor2312 пишет:У ВВ79 ограничение на матрицу в 8*8

Вы думаете наизнанку... просто когда эти микросхемы проектировали, или у нас выпускали, не было никаких Корветов, Специалистов

Упомянул об этом потому, что все промышленные клавиатуры как раз не укладываются в матрицу 8*8. У меня есть две отличные фирменные ретро клавиатуры из 80-тых с матрицей более чем 8*8 и есть корветовская клавиатура с герконами (а матрица там вообще огромная 8*16).

Этого никто знать не может. В моём РК, полностью по схеме журнала сброс работал нормально. Важно лишь, чтобы длительность сброса была не менее трёх маш.тактов, а если используется программная регенерация РУ5, то длительность сброса должна быть короткой, иначе пауза в регенерации превысит 2 МСЕК и данные в ОЗУ утратятся.что думаете по поводу конденсатора и резистора в схеме сброса. Если поставлю 4,7 мкФ и резистор 15 кОм, нормально будет?

barsik- Ветеран

- Сообщения : 1032

Дата регистрации : 2016-11-10

Откуда : Россия

Re: Разработка, сборка, наладка ВМИР-1.

Re: Разработка, сборка, наладка ВМИР-1.

8

Уверен, Вы не сможете вразумительно объяснить зачем эта железяка Вам нужна и что даст.

Для себя мне это объяснять не нужно, я знаю, а другим, зачем это знать, ну хочу я её сделать и другим должно быть абсолютно по барабану ЗАЧЕМ.

(или хотя бы в обозримой перспективе) получить результат.

Нет проблем получить результат в обозримом будущем, ну если поможете с мелкими трудностями.

А сделать бессмысленную железяку, причём именно на серии 1974 года выпуска, это никак кроме как детской игрой в инженера-разработчика не назовёшь. Лучше бы Вы занялись изготовлением реплики СМ-1800.

Я думаю пора вам прекратить убеждать меня не делать то, что было задумано ещё в 2012 году, примерно и ни раз обдумано, и моё мнение, желание и т. д. Не изменились.

Вот опять продолжается словоблудие и переливание из пустого в порожнее, вместо чего-то реального и полезного. Лучше бы подумали о реализации портов.

Во-первых, это форум. Для того и предназначенный. Во-вторых, невозможно на всех тематических форумах найти другой более бессмысленный и бесполезный проект чем Ваш. Да и удивление. Мне (и опять-таки всем) хочется понять о чём речь.

Я достаточно вразумительно описал систему, её общую структуру. УПЭ + 64 ПЭ.

Странные, необычные и с практической точки зрения бесполезные проекты бывают. Но в них есть идея и достигается результат. А Вы запланировали сделать что-то абсолютно бесполезное (главное, чтобы красивое, да?) и неспособное дать хоть какой-то результат.

Понять всё, ладно, сам справлюсь как нибудь...

Лучше бы Вы занялись изготовлением процессора на транзисторах КТ315. В России таких энтузиастов нет, но в мире империализма, где у людей килограммы денег и свободного времени, было с десяток подобных проектов. Но их можно хотя бы понять.

Вот это точно: "абсолютно бесполезное (главное, чтобы красивое, да?) и неспособное дать хоть какой-то результат."

А что даёт и для чего годится ваше нагромождение железа?

Объяснять бесполезно, даже пытаться не буду.

и это обьявляется компьютером искусственного разума. Трудно придумать бОльшую чушь.

Я не употреблял слово компьютер, есть перевод на русский, вычислитель. Для вас чушь, для меня нет.

Давайте ещё на 100 страниц поприпираемся, это так весело... А может всё же порт. Параллельный. Это интереснее.

До чокнутого, т.е на самом деле одержимого идеей человека, Вы сильно не дотягиваете. Скорее это похоже на игру в разработчика. Похоже Вы решили освоить разработку изделий на МП-комплекте КР580 и где-то взяли нелепую мысль, что столь крошечная нейронная сеть что-то может. И внушили себе, что это Вам зачем-то надо.

Я не делаю нейронную сеть, вы повторяетесь, это уже не интересно...

Чушь какую-то пишите и пишите, я делаю на КР580, так как мне нравится этот микропроцессорный комплект, так как я так хочу, так как мне так нравится, так как мне так хочется, и т. д.

Вот я и хотел узнать конечную цель проекта, зачем это надо и что это даёт

Для того, чтобы вам было проще, считайте, что цель собрать, чтобы работало, считайте её конечной целью.

Не согласен. Приведите хоть один пример этого.

Не буду, реально нет времени на эти препинания.

Глупо обижаться на правду. Другие вообще Вас игнорируют, не желая тратить время на чушь и не я первый говорю Вам, что данный проект полная чушь. Единственная польза от него это лишь изучение Вами проектирования МП-систем. Найдите хоть одного человека, кто думает об этом иначе. Потому, чтобы "спасти репутацию вашу и форума" я и хотел, чтобы Вы убрали всякое упоминание, что Вы разрабатываете ИР. С тем же успехом можно в названии темы указать, что автор темы не в себе.

Я не обижался ни разу, я пофигист, и мне пофиг.

Мне на других пофиг, мне и самого себя, в крайнем случае, вполне достаточно, я же того... Так что могу и сам с собой разговаривать и замутить раздвоение личности, и мне будет очень весело и не скучно ха ха ха...

Для вас чушь, для меня нет.

Я сам определюсь с пользой.

Я не собираюсь никого искать, мне фиолетово, что они думают.

Какие репутации, кому что-то не нравится, пусть проходят мимо, я никого не зазываю, и не удерживаю, я просто сделал форум таким, чтобы мне на нём было удобно и комфортно, а все остальные могут либо пользоваться, таким как он есть, либо нет, я ни на чём не настаиваю, и про всякие выдуманные репутации, мне плевать.

Могу и добавить, но лень тратить на это время, итак вот сижу и строчу ерунду, вместо того, чтобы читать про К1802ВР3 или искать какой из умножителей можно взять у поставщиков, по приемлемой цене и в достаточном количестве.

Нюансы станут ясны, когда Вы поймёте как работает параллельный обмен, для чего надо самому написать интерфейс на ввод и на вывод. А вообще параллельный обмен между двумя ППА удобнее производить не в режиме 0, а в режимах 1 или 2. Тогда процессору не надо самому выдавать упр.сигналы. Раз надо много портов, то удобно сочетать режимы ППА

Вот уже ближе к теме, как раз в этих режимах я и запутался. Вот про это и расскажите поподробнее, хотя я думаю мне нужно почитать, а то подзабылось и спрашивать уже конкретно, что мне не понятно, но не сейчас, я спать хочу, а завтра сначала поработать нужно, мне МФУ ремонтировать, потом картриджи заправлять и ремонтировать и вообще куча работы.

Пока остановимся на том, что мне нужно освежить в памяти работу ППА в режимах 1 и 2.

И я думаю, что на выходе нужно будет вообще буферы поставить, так как расстояния между соседними ПЭ вполне приличные оказываются, например до УПЭ у отдельных портов расстояние может быть и до 5 метров. Например К555АП5.

Вот тут коммент аж приятно было писать, всё чётко и по делу.

Телевизор и CGA монитор не могут показать более 280 линий, для 480 линий растра нужен VGA-дисплей.

Но вот насколько я знаю даже КР580ВГ75 тянет VGA притом точно и на практике, на zxpk делали точно такое. Хорошо было бы 640 х 480 и любой стандартный монитор, да хоть ЖК, хоть ЭЛТ, и простенький цвет. Но это позже, прошу это не комментируйте, не загромождайте тему, для этого ещё рано, когда УПЭ будет проектироваться, сейчас только ПЭ.

Спрайты это маленькие, но целые картинки (в основном фигурки в разных фазах), а тайлы это или то, из чего крупная фигурка спрайт строится (т.е фрагменты спрайтов), или такие тайлы из которых рисуется пейзаж.

Спасибо за разъяснение. Разговор перетекает в рабочее русло, это радует.

Я просто промолчал, что хочу контроллер дисплея 1024 х 768 и с цветами и на нескольких процессорах, и только К555 серия, побоялся, что тогда диагноз поставите, ещё хуже чем сумасшедший, поэтому пока и не заикался. Только это хоть не комментируйте...

Этого никто знать не может. В моём РК, полностью по схеме журнала сброс работал нормально. Важно лишь, чтобы длительность сброса была не менее трёх маш.тактов, а если используется программная регенерация РУ5, то длительность сброса должна быть короткой, иначе пауза в регенерации превысит 2 МСЕК и данные в ОЗУ утратятся.

Я просто нигде почему-то не нашёл формулы и описания как эта цепь рассчитывается. Ну регенерация у меня явно не программная, модуль вообще без процессора может работать и хранить там записанную информацию, только питание и тактовые импульсы подавать нужно, а так на вход управления приходил лог. 1 модуль в системе, лог. 0 модуль отключён. И таких модулей в системе может быть много, главное о стеке как-то позаботиться, чтобы при переходе на, допустим вторую страницу, в стеке ничего не было или как-то нужно им не пользоваться пока на второй странице, либо переписывать его содержимое, но тогда только через регистры процессора, а так конечно хочется 4 Кбайта ПЗУ и два модуля, но не важно какая страница включена, всё равно ПЗУ всегда доступно должно быть, поэтому на железном уровне при обращении к ПЗУ, то есть по адресам в диапазоне первый 4 Кбайт, доступно ПЗУ выше ОЗУ, и в итоге получится 2 страницы по 60 Кбайт или 120 Кбайт всего, но с переключением страниц, например одним из портов. При включении регистр порта сбрасывается, и соответственно выбрана 0 страница, при записи в регистр порта соответственно комбинации противоположной и выбрана 1 страница и т. д. я думаю поняли, завтра как освобожусь, приступлю к вычерчиванию схемы, а то всё обдумываю да обдумываю, хотя у меня уже и есть три варианта схемы ПЭ ver 1.0, ver 2.0 и ver 3.0 . Собрана ver 1.0 та что на фото. Но не думаю, что их стоит выкладывать, там именно версии с индикацией шин, и с СПИП, в одной из версий даже прикрутил 7-сегментный индикатор, чтобы в виде чисел можно было выдавать код ошибки, предусматривалось, что напишу подпрограмму проверки модуля пожирнее, чем просто проверка памяти. Типа при включении, сначала выполняется она, проверяет память, высвечивает 9, потом возможно ещё тест памяти, по другой методике и высвечивает 8, потом ещё что-то проверяет и высвечивает 7 и так до 1 и если тест проеден то 0, а нет, начинает писать ЕГОГ.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

9

Я в этом полный чайник. Не видел ни одной чужой программы с ППА в ненулевом режиме и сам никогда не использовал ППА в режиме не 0. Параллельный интерфейс доводилось писать только в драйвере принтера для ОРИОНА с использование режима 0 и программным опросом готовности и формированием строба.Viktor2312 пишет:как раз в этих режимах я и запутался. Вот про это и расскажите поподробнее,

Режимы 1 и 2 хороши тем, что ввод происходит без участия процессора, потому такой режим удобен для построения КНГМД. У меня есть схема самодельного КНГМД из 1989 года, где ППА в таком режиме. Режимы 1 и 2 удобно использовать с прерываниями, а режим 0 c формированием упр.сигналов в порту С процессором - в режиме 0.

Реакция на поступление байта конечно быстрее с прерываниями, но в каком режиме быстрее скорость пересылки неизвестно. Самая быстрая скорость пересылки получается с использованием ПДП (4 такта на байт). А программно в цикле с опросом готовности получается лишь 71 такт на байт (это для Z80, для КР580 чуть больше, у меня просто нет таблички с длительностями команд КР580).

При 2-х МГЦ клока CPU маш.такт длится 0.5 МКСЕК. Значит 1 байт принимается в лучшем случае за 71*0.5= 35.5 МКСЕК. Значит за секунду в лучшем случае будет принято ~28 кб.

http://madelectronics.ru/uchebnik/6.17.9.htm Тут нужен учебник электротехники. Это изучают в ВУЗ-е на первом курсе (теория линейных цепей), в ПТУ на 2-м курсе и даже в школе (в 10-м или 11-м классе).Я просто нигде почему-то не нашёл формулы и описания как RC-цепь рассчитывается.

Проблема стека при цельно-банковой коммутации банок не проблема. Разработчик ОРИОНА В.Сугоняко применил аппаратное решение этой проблемы, т.е специальную архитектуру с 1 кб некоммутируемой памяти в вершине ОЗУ (F000...F3FF). Стек в области выше F000 не мешает переключать банки.главное о стеке как-то позаботиться, чтобы при переходе на... вторую страницу, в стеке ничего не было или нужно... им не пользоваться пока включена вторая страница

Но, если есть некоммутируемое ПЗУ, то и программно это прекрасно решается. При включении второй банки число из регистра SP сохраняется во временной ячейке хранения и SP переустанавливается на то значение стека которое приемлемо для программ во второй банке и программы в этой банке работают со стеком. А перед возвратом регистр стека восстанавливается и делается возврат в банку 0. При этом в некоммутируемом ПЗУ д.быть соответствующий набор подпрограмм.

При двух или нескольких банках и использовании прерываний возникает некоторая проблема. Если процедура обслуживания прерываний находится в банке 0, то при приходе прерывания в момент когда текущая другая банка, возникает улёт. Потому при прерываниях лучше иметь всего одну банку.

barsik- Ветеран

- Сообщения : 1032

Дата регистрации : 2016-11-10

Откуда : Россия

Re: Разработка, сборка, наладка ВМИР-1.

Re: Разработка, сборка, наладка ВМИР-1.

10

При двух или нескольких банках и использовании прерываний возникает некоторая проблема. Если процедура обслуживания прерываний находится в банке 0, то при приходе прерывания в момент когда текущая другая банка, возникает улёт. Потому при прерываниях лучше иметь всего одну банку.

Ну, предполагается, что прерывания будут использоваться для портов, а подпрограммы обслуживания прерываний находиться в ПЗУ, соответственно не имеет значения какая страница включена 0 или 1.

Проблема стека при цельно-банковой коммутации банок не проблема. Разработчик ОРИОНА В.Сугоняко применил аппаратное решение этой проблемы, т.е специальную архитектуру с 1 кб некоммутируемой памяти в вершине ОЗУ (F000...F3FF). Стек в области выше F000 не мешает переключать банки.

Предполагается использовать стек в верхней части памяти, но вот думал какого объёма, подумывал над 1 Кбайтом, но думал не много ли, вы прямо разрешили мою делему, значит будет предполагаться, что глубина стека будет 1 Кбайт, то есть при написании программ нужно будет иметь в виду, что зализать выше условно нельзя, можно подумать, может поставлю статическое ОЗУ на 1 Кбайт в верхних адресах, чисто для стека, по типу ПЗУ в нижних адресах. То есть при обращении по адресам верхнего последнего килобайта, запись и считывание будет происходить из этого ОЗУ, таким образом получается, что недоступны 4 Кбайта снизу и 1 Кбайт сверху, и при 1 странице доступно 59 Кбайт, при двух 118 Кбайт основного ОЗУ. Осталось только продумать реализацию, по ходу пьессы, или вернуться к тому что 2 Кбайта ПЗУ, тогда 61 Кбайт и 122 Кбайта основного ОЗУ будет, делема, хватит ли 2 Кбайт для всего необходимого встроенного ПО...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

11

К сожалению, модератор ленится или не умеет переносить посты, из-за чего в некоторых темах царит "злостный оффтоп". Потому, чтобы уменьшить оффтоп на вот этот пост отвечаю здесь.

Забыл упомянуть, что, если так уж нравятся команды IN/OUT, то их можно поиметь и без ВК28. У КР580 есть одно свойство позволяющее использовать эти команды для ВВ55, если выделить на его адресацию 1 кб.

А при КР580 придётся иметь в ПЗУ 64 таких подпрограммы для связи с каждым из 64-х модулей, т.к в подпрограмме для КР580 в команде IN A,(nn) адрес порта фиксирован. В итоге объём ПЗУ понадобится в 64 раза больший.

А у процессора 6800 и это уже учтено, там при загрузке ставятся флаги. В итоге петля анализа флага у 6800 отнимает всего 8 маш.тактов (что соответствует 16-ти тактам КР580), а на КР580 с IN/OUT это отнимает 30 маш.тактов.

Вот если бы у КР580 команда IN выполнялась с маскированием битов и выставлением флагов (как сделано в однокристаллах), то I/O-порты приносили бы реальную пользу. А так вся польза от I/O-портов заключается лишь в том, что уже по виду команды ясно, что команда работает с портом.

Вы хоть подумайте о том, как в реале отлаживать программу в ПЭ, когда у него нет ни отладчика, ни органов управления и отображения. Т.к основную работу выполняют ПЭ, а не УПЭ, значит объём программ работающих в ПЭ будет в сотни раз больше. Значит для отладки придётся сделать один отладочный ПЭ с органами для отладки и программным отладчиком. Но и это не поможет. Т.к программы в ПЭ работают не по отдельности, а вместе и одновременно, отлаживать работу системы будет в тысячу раз сложнее, чем одну программу того же огромного размера.

Но главный и непреодолимый довод, что такая система нереализуема в том, что без ЯВУ написать столь сложное ПО явно вообще невозможно. А для ЯВУ 8-ми разрядки не годятся, по причине нехватки скорости и быстрого разбухания объёма кода за границу адресного пространства. Т.е для 8-ми разрядки на ЯВУ можно написать только маленькую несложную программу.

И тупое цельно-банковое расширение ОЗУ (как Вы рассчитываете) тут вообще не поможет, т.к для 8-ми разрядок нет компиляторов создающих код для двух или нескольких банок. Т.е для ЯВУ КР580 непреодолима граница 64 кб (за вычетом ПЗУ).

Это значит, что для данной системы написать ПО вообще невозможно, даже если бы программы писали 200 тысяч программистов. Даже применение Z180/Z280 поддерживающих много ОЗУ за счёт блока MMU не поможет. Потому, чтобы использовать ЯВУ нужен, как минимум, процессор 8088 (а лучше 68008, у него память до 16 мб и нет сегментирования).

Конечно. Это принесло большую пользу при анализе исходников для тех, кто не в состоянии запомнить адреса портов.Viktor2312 пишет:Считаю, что [IO-порты] отличная идея и правильно, что так сделали

Забыл упомянуть, что, если так уж нравятся команды IN/OUT, то их можно поиметь и без ВК28. У КР580 есть одно свойство позволяющее использовать эти команды для ВВ55, если выделить на его адресацию 1 кб.

Тогда у Вас - "семь пятниц на неделе" и Вы меняете условия, когда Вам выгодно. Скорости последовательного интерфейса мало и экономный по железу общий канал для связи модулей недопустим по причине потери скорости, а теперь оказывается скорость избыточная.Та скорость, что имеется, даже избыточна

При Z80 команды IN A,(C) или IN A,(BC) позволяют использовать одну подпрограмму интерфейса для связи со всеми 64-мя модулями, т.к эту подпрограмму интерфейса можно вызывать для каждого модуля, соответственно загружая в регистры адрес порта.Viktor2312 пишет:barsik пишет:в системе работающей из ПЗУ нельзя изменить адрес порта

А его и не нужно менять

А при КР580 придётся иметь в ПЗУ 64 таких подпрограммы для связи с каждым из 64-х модулей, т.к в подпрограмме для КР580 в команде IN A,(nn) адрес порта фиксирован. В итоге объём ПЗУ понадобится в 64 раза больший.

Я же выше писал, что это даёт ускорение обмена с анализом флага готовности. Поясняю: вместо одной команды в системе с портами IN/OUT на ввод и анализ флага нужны две команды - загрузка из порта и выделение бита для получения флага командой маскирования или сдвига. Это потеря 4-х или 7-ми маш.тактов.Viktor2312 пишет:barsik пишет:при порте в области памяти с данными порта одновременно со считыванием можно делать анализ битов

Ну и нафиг это нужно, "начерта кобыле 5-я нога"...

А у процессора 6800 и это уже учтено, там при загрузке ставятся флаги. В итоге петля анализа флага у 6800 отнимает всего 8 маш.тактов (что соответствует 16-ти тактам КР580), а на КР580 с IN/OUT это отнимает 30 маш.тактов.

Вот если бы у КР580 команда IN выполнялась с маскированием битов и выставлением флагов (как сделано в однокристаллах), то I/O-порты приносили бы реальную пользу. А так вся польза от I/O-портов заключается лишь в том, что уже по виду команды ясно, что команда работает с портом.

Намного более реально написать эмулятор этой системы, чем сделать в железе. При этом даже не придётся писать эмуляцию 64-х модулей ПЭ. Т.к модули одинаковы достаточно одного блока эмуляции, переключая для прогона его для каждого ПЭ содержимое ПЗУ, ОЗУ и регистров. С учётом огромного превосходства в скорости современных ЭВМ (что не в 64 раза скоростнее, чем КР580, а в многие тысячи раз), эмулятор будет работать намного быстрее, чем реальное изделие. А отлаживать столь сложную программу в эмуляторе вообще будет в тысячу раз проще, чем на реале.если за 5 месяцев уложиться в разработку [ВМИР], то за 1 год всё реализуемо

Вы хоть подумайте о том, как в реале отлаживать программу в ПЭ, когда у него нет ни отладчика, ни органов управления и отображения. Т.к основную работу выполняют ПЭ, а не УПЭ, значит объём программ работающих в ПЭ будет в сотни раз больше. Значит для отладки придётся сделать один отладочный ПЭ с органами для отладки и программным отладчиком. Но и это не поможет. Т.к программы в ПЭ работают не по отдельности, а вместе и одновременно, отлаживать работу системы будет в тысячу раз сложнее, чем одну программу того же огромного размера.

Но главный и непреодолимый довод, что такая система нереализуема в том, что без ЯВУ написать столь сложное ПО явно вообще невозможно. А для ЯВУ 8-ми разрядки не годятся, по причине нехватки скорости и быстрого разбухания объёма кода за границу адресного пространства. Т.е для 8-ми разрядки на ЯВУ можно написать только маленькую несложную программу.

И тупое цельно-банковое расширение ОЗУ (как Вы рассчитываете) тут вообще не поможет, т.к для 8-ми разрядок нет компиляторов создающих код для двух или нескольких банок. Т.е для ЯВУ КР580 непреодолима граница 64 кб (за вычетом ПЗУ).

Это значит, что для данной системы написать ПО вообще невозможно, даже если бы программы писали 200 тысяч программистов. Даже применение Z180/Z280 поддерживающих много ОЗУ за счёт блока MMU не поможет. Потому, чтобы использовать ЯВУ нужен, как минимум, процессор 8088 (а лучше 68008, у него память до 16 мб и нет сегментирования).

barsik- Ветеран

- Сообщения : 1032

Дата регистрации : 2016-11-10

Откуда : Россия

Re: Разработка, сборка, наладка ВМИР-1.

Re: Разработка, сборка, наладка ВМИР-1.

12

К сожалению, модератор ленится или не умеет переносить посты, из-за чего в некоторых темах царит "злостный оффтоп". Потому, чтобы уменьшить оффтоп на вот этот пост отвечаю здесь.

Наконецтаки до вас начинает доходить, что общаться на тему Ориона, нужно в теме Ориона, а на тему ВМИР-1, в теме посвящённой ВМИР-1. Сейчас мне некогда переносить те посты, так как чтобы перенести пост, нужно много действий произвести, выделить в отдельную тему, потом слить с другой темой, мне некогда это сейчас делать, да и вообще, пусть там живут.

Конечно. Это принесло большую пользу при анализе исходников для тех, кто не в состоянии запомнить адреса портов.

Вы уже давно об этом пишите, мы уже поняли, вам не нравятся команды IN и OUT. Свою точку зрения вам уже тоже многие высказали, им и мне это нравится, а потому будет применяться и использоваться. Я свою точку зрения не меняю, так как она складывается долго, годами, во время изучения, освоения и применения на практике, тех или иных схемных решений.

Забыл упомянуть, что, если так уж нравятся команды IN/OUT, то их можно поиметь и без ВК28. У КР580 есть одно свойство позволяющее использовать эти команды для ВВ55, если выделить на его адресацию 1 кб.

У меня нет проблем с применением КР580ВК28, и она уже стоит в схеме и отлично себя зарекомендовала, и кстати в схеме ПЭ_2019_ver1.0 она уже стоит, оболденная и классная микросхема, просто шедевр инженерной мысли.

Вы всё время хотите что-то сделать не по стандарту и не так как разработано, всё время хотите напхать кучу логики туда, где можно поставить 1 микросхему, притом специально разработанную, чтобы заменить кучу логики, но нет, мы идём стандартным путём, удобным и понятным. Одна микросхема, специально для этого предназначенная, с понятной логикой работы, и никаких лишних геморов.

Тогда у Вас - "семь пятниц на неделе" и Вы меняете условия, когда Вам выгодно.

Ничего не менялось в концепции с 2012 года. Стандартный параллельный порт, реализованный на ППА. А какую скорость получится получить, та и устраивает.

а теперь оказывается скорость избыточная.

Да, так как будет не один общий канал, одно окно для обслуживания и очередь из 64 страждущих отправить/принять по нему информацию,а много, от чего проблем с скоростью передачи нет. В один момент времени многие ПЭ будут обмениваться информацией, без ожиданий общего канала.

При Z80 команды IN A,(C) или IN A,(BC) позволяют использовать одну подпрограмму интерфейса для связи со всеми 64-мя модулями, т.к эту подпрограмму интерфейса можно вызывать для каждого модуля, соответственно загружая в регистры адрес порта.

У нас не зетвосемьдесят. Так что нет смысла дажу упоминать о нём, я его не использовал, не использую, и не собираюсь, я не знаю его устройство, систему команд, и не хочу знать, этот зетавосемьдесят мне не интересен. У меня есть система команд КР580ВМ80А и только она мне интересна, я уже капитально всё подзабыл за последние 7 лет, придётся всё вспоминать, особенно тонкости и нюансы, ну ничего, вспомним.

А при КР580 придётся иметь в ПЗУ 64 таких подпрограммы для связи с каждым из 64-х модулей, т.к в подпрограмме для КР580 в команде IN A,(nn) адрес порта фиксирован. В итоге объём ПЗУ понадобится в 64 раза больший.

Фигня это всё, у ПЭ имеется 7 портом и соответственно, если и потребуется как вы пишете, то 7 подпрограмм. Для чего ПЗУ 2 КБайта будет достаточно. Уже определился, не буду менять основную концепцию, 2 Кбайта ПЗУ и 1 страница ОЗУ на 64 Кбайта с доступными 62 Кбайта.

Я же выше писал, что это даёт ускорение обмена с анализом флага готовности. Поясняю: вместо одной команды в системе с портами IN/OUT на ввод и анализ флага нужны две команды - загрузка из порта и выделение бита для получения флага командой маскирования или сдвига. Это потеря 4-х или 7-ми маш.тактов.

Ну я уже писал вам, что нужно смириться с тем, что есть. Порты в ПЭ находятся в отдельном поле, и у нас 256 портов. Это факт, данность. Так устроен данный мир. А точнее ВМИР.

А у процессора 6800 ...

Пофиг, что там у этого процессора или у Intel Core i9 или ещё у какого бы то ни было. У нас есть КР580ВМ80А и интересует только то, что есть у него и реализация всего необходимого, его доступными средствами. Он есть как данность, как и ПЗУ 2 Кбайта и 62 Кбайта доступного ОЗУ и 256 портов ввода-вывода. Всё другого не дано и другое не интересно.

Вот если бы у КР580...

Если бы, да дакабы, во рту росли грибы, это был бы не рот а целый огород...

Намного более реально написать эмулятор этой системы, чем сделать в железе.

Цель как раз обратная, сделать "железо". Яж вам писал, для простоты, понимания, считайте что основная цель, это собрать "железо" и запустить, чтобы работала. И всё. И не засоряйте себе мозг расшифровкой аббревиатуры ВМИР, не думайте о стоимости и трудозатратах, для вас - основная моя цель, это собрать ВМИР-1 в железе. За всё остальное не переживайте.

При этом даже не придётся писать эмуляцию 64-х модулей ПЭ. Т.к модули одинаковы достаточно одного блока эмуляции, переключая для прогона его для каждого ПЭ содержимое ПЗУ, ОЗУ и регистров. С учётом огромного превосходства в скорости современных ЭВМ (что не в 64 раза скоростнее, чем КР580, а в многие тысячи раз), эмулятор будет работать намного быстрее, чем реальное изделие. А отлаживать столь сложную программу в эмуляторе вообще будет в тысячу раз проще, чем на реале.

Не интересно. И пофиг на возможности современного "железа".