Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Статьи, заметки, очерки, разное... Микроконтроллеры.

RUЭВМ :: Микроконтроллеры :: Разное

Страница 1 из 1 • Поделиться

Статьи, заметки, очерки, разное... Микроконтроллеры.

Статьи, заметки, очерки, разное... Микроконтроллеры.

1

.

.

.

Универсальный преобразователь напряжения в последовательность импульсов на микроконтроллере PIC12F683.

Ricardo Jiménez и Juan C. Ángeles

Electronic Design

Если для преобразования выходного сигнала аналогового датчика в последовательность импульсов использовать обычный стандартный микроконтроллер, его выход будет совместим с цифровыми портами ввода/вывода.

____Когда возникает необходимость преобразования значений напряжения аналогового датчика в серию импульсов, универсальным решением может стать простейший микроконтроллер. В схеме на Рисунке 1 использован 8-выводной микроконтроллер PIC12F683, формирующий последовательность импульсов, длина которой пропорциональна измеряемому входному напряжению. Подобная схема может оказаться полезной, например, для преобразования сигнала датчика в формат, совместимый со стандартным цифровым входом. Рабочему диапазону входных напряжений от 0 до 5.00 В соответствует диапазон длин последовательностей от 0 до 500 импульсов.

Рисунок 1. Количество импульсов на выходе GP2 микроконтроллера пропорционально

напряжению, измеренному на входе AN3. Счетчик запоминает число, соответствующее

длине последовательности, которое затем декодируется и отображается на

мультиплексируемом светодиодном дисплее с общим катодом.

____К примеру, входное постоянное напряжение (VIN) 1.25 В будет преобразовано в последовательность из 125 импульсов, количество которых (Pt) в общем случае вычисляется по формуле

Pt = VIN × 100,

где VIN – выраженные в вольтах целые, десятые и сотые доли входного напряжения. В данной схеме каждый импульс имеет длительность 1 мс при коэффициенте заполнения 50%. Время обновления (Rt) определяется выражением

Rt = VIN × 1 мс + задержка 50 мс.

____Наибольшее время обновления составит 0.499 с (плюс задержка 50 мс) при входном сигнале 4.99 В, в то время как наименьшее время 51 мс соответствует входному напряжению 0.01 В. 50-миллисекундная задержка добавлена ко всем отсчетам специально, чтобы исключить мерцание дисплея.

____Входное аналоговое напряжение с движка подстроечного резистора 47 кОм поступает на аналоговый вход микроконтроллера (AN3). Разрядность внутреннего аналого-цифрового преобразователя (АЦП) установлена равной 8.

____Для проверки программы микроконтроллера в схему включен трёхдекадный счетчик MC14553, подсчитывающий число импульсов в последовательности. Код длины последовательности защелкивается во внутреннем регистре счетчика и мультиплексно, по четыре разряда, выводится на дешифратор MC14543 (CD4543), управляющий мультиплексируемым четырехразрядным светодиодным дисплеем через три ключевых транзистора. Внешний вид схемы, собранной на макетной плате, показан на Рисунке 2.

Рисунок 2. Отсутствие критических требований к топологии или

высокочастотных цепей позволило собрать и испытать

схему на стандартной макетной плате.

____Для формирования на выводе GP2 последовательности импульсов с длиной, пропорциональной входному напряжению, программа микроконтроллера (см. ссылку на листинг в конце статьи) берет результат преобразования АЦП с весом единицы младшего разряда (LSB) 19.60 мВ и преобразует его в двоично-десятичную форму. Затем, используя инструкции DIG3, DIG2 и DIG1, соответственно, программа вычисляет десятичные эквиваленты единиц, десятых и сотых долей полученного числа. Значение DIG1 запоминается в переменной “units” для использования в цикле формирования числа единиц импульсов. Аналогично, значение DIG2 умножается на 10 и записывается в переменную “decimals” для генерации десятков импульсов. И в конце значение DIG3 запоминается в переменной «units», которая умножается на 100 для получения сотен импульсов.

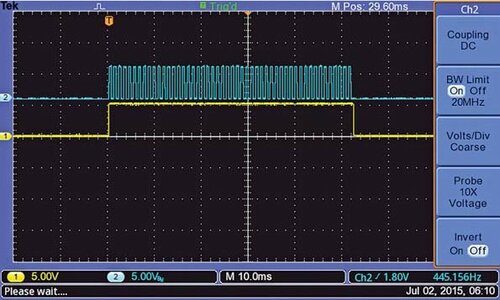

Рисунок 3. Временная диаграмма сформированной импульсной последовательности.

Уровень сигнала, отображаемого желтым цветом, остается высоким на

протяжении всего времени трансляции последовательности.

____Таким образом, например, измеренные 2.54 В будут состоять из 4, затем 50, и затем 200 импульсов, из которых будет получено всего 254 импульса, следующих с периодом 1 мс. Соответственно, для передачи этой последовательности импульсов потребуется примерно 254 мс. Если одна из цифр равно нулю, программа пропускает соответствующий цикл. На Рисунке 3 показаны осциллограммы последовательности импульсов и соответствующего сигнала, формируемого на выходе GP5.

Рисунок 4. Импульсы LE (запись) и MR (сброс), сформированные микроконтроллером

по окончании цепочки импульсов, используются для сохранения

результатов измерения и очистки счетчика, соответственно.

____По завершении передачи последовательности на выходе GP0 формируется отрицательный импульс длительностью 1 мс, переписывающий содержимое счетчиков во внутренние регистры MC14553. Вслед за ним на выходе GP1 появляется второй импульс такой же длины, но положительной полярности, сбрасывающий в ноль все регистры счетчика (Рисунок 4). Для регистров дешифратора MC14543 установлен прозрачный режим. Выход GP5 используется микроконтроллером для индикации процесса передачи импульсной последовательности.

____Три p-n-p транзистора 2N2907 (Q1 … Q3), непрерывно сканирующих светодиодный дисплей, управляются счетчиком MC14553. Транзистор включает десятичную точку, формируя 5-вольтовый импульс только в те моменты времени, когда сигнал на выходе /DS1 имеет низкий уровень. На Рисунке 5 показана последовательность из 11 импульсов, соответствующая входному напряжению 0.11 В, и импульс записи LE, генерируемый в конце передачи импульсной последовательности.

Рисунок 5. При входном напряжении 0.11 В микроконтроллер генерирует 11

импульсов, за которыми следует импульс записи LE,

сохраняющий результат измерения.

____Для приложений более высокой точности (например, 4.88 мВ на LSB), вы можете выбрать 10-разрядную конфигурацию АЦП. Тогда период выходного сигнала может быть сокращен до 0.5 мс, чтобы избежать увеличенных задержек при максимальных входных напряжениях. В этом случае при входном напряжении 1.000 В длина цепочки составит 1000 импульсов. При батарейном питании схемы рекомендуется использовать цифровой жидкокристаллический дисплей, для которого потребуются три дешифратора MC14543.

источник

Последний раз редактировалось: Viktor2312 (Вт Фев 25 2020, 09:46), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

2

.

.

Новое семейство микроконтроллеров PIC24 “GA7” с низким энергопотреблением от Microchip.

____Компания Microchip анонсирует новое семейство микроконтроллеров (МК) PIC24 “GA7”. Они отлично подойдут для экономичных приложений — например, для сенсорных сетей «Интернета вещей» (IoT), портативных медицинских приборов, промышленных систем управления.

____МК семейства PIC24 “GA7” позволят разработчику уменьшить энергопотребление, стоимость и габариты. В МК реализован ряд режимов пониженного энергопотребления, в том числе несколько режимов сна, сокращающих ток потребления до 190 нА, благодаря чему существенно возрастает срок службы батарей. При этом стоимость МК ниже, чем у более ранних продуктов. Новые МК доступны в модификациях с объемом флэш-памяти 64, 128 и 256 кбайт содержат ОЗУ до 16 кбайт и производятся в 28-, 44- и 48-выводных корпусах малых размеров вплоть до 4×4 мм.

____МК PIC24 “GA7” содержат независимую от ядра периферию (CIPs), в состав которой входят конфигурируемые логические ячейки (CLC), ШИМ захвата сравнения с несколькими выходами (MCCP) и независимый доступ к памяти (DMA). DMA позволяет решать задачи на аппаратном уровне, разгружая центральный процессор (ЦПУ) для решения других задач или позволяя ему перейти в режим сна. В состав периферии входит устойчивый к сбоям 12-разрядный АЦП производительностью 200 Квыб/с, до 7 таймеров и 2 интерфейса UART.

____Новые МК семейства PIC24 “GA7” поддерживаются макетной платой Explorer 16/32 и всей экосистемой (DM240001-2), а также новым плагином PIC24FJ256GA705 (MA240039), который подключается к плате Explorer 16/32 для разработки и оценки возможностей МК. Процесс можно ускорить за счет совместимых с GA7 платформ разработки ПО: конфигуратор MPLAB Code Configurator (MCC), MPLAB X IDE и XC16 Compiler.

источник

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

3

.

.

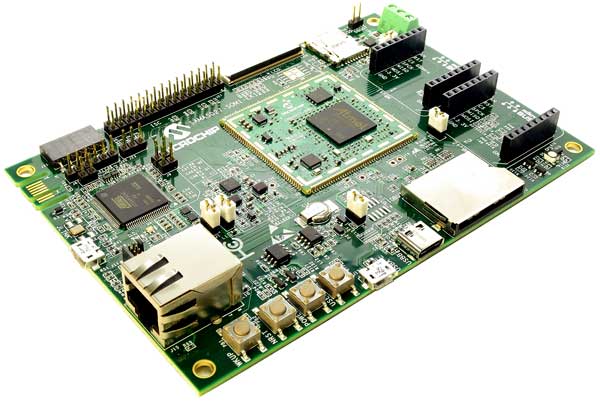

Новая макетная плата от Microchip для проектирования систем с 16- и 32-разрядными микроконтроллерами PIC

____Компания Microchip анонсировала новую макетную плату Explorer 16/32 для проектирования систем с 16- и 32-разрядными микроконтроллерами (МК). Ее стоимость ниже, чем стоимость популярной макетной платы Explorer 16, кроме того, в ее состав входят программатор/отладчик и ряд новых функций для проектирования современных встраиваемых систем. Плата являет собой адаптивный и удобный инструмент, позволяющий быстро приступить к работе, обеспечена обратная совместимость с классической платой Explorer 16.

____Благодаря легко сменяемым плагин-модулям (PIMs) макетная плата Explorer 16/32 служит платформой для оценки возможностей 16-разрядных PIC24, dsPIC33 и 32-разрядных PIC32 микроконтроллеров. Это обстоятельство облегчает прототипирование и помогает проверить концепцию проекта перед началом производства. На плате есть интерфейс mikroBUS, что позволяет добавить новые возможности за счет подключения платы Click от MikroElectronika. Также на плате предусмотрен USB, через который помимо передачи данных подсоединяется питание, что уменьшает потребность в дополнительных адаптерах для питания и других коммуникаций.

____Новая плата обратно совместима с популярной Explorer 16, поэтому можно использовать прежние программы, библиотеки, прототипы, плагины PIM и дочернюю плату PICtail, подключив ее через разъем, а также плату с расширениями PICtail Plus.

____В состав комплекта разработчика Explorer 16/32 (DM240001-3) входит макетная плата Explorer 16/32, модуль-плагин PIC24FJ1024GB610 и кабель USB. На плагине установлен 16-разрядный МК PIC24FJ1024GB610 с низким энергопотреблением и объемом флэш-памяти 1 Мбайт и расширенный набор памяти.

источник

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

4

.

.

Микроконтроллер Microchip PIC с 1-Мбайт флэш с коррекцией ошибки кода и ОЗУ 32 кбайт.

____Компания Microchip анонсирует расширение своего портфолио микроконтроллеров (МК) с низким энергопотреблением. Особенности нового семейства PIC24F «GB6» заключаются в 1-Мбайт флэш с коррекцией ошибки кода и ОЗУ 32 кбайт. Это первое семейство 16-разрядный МК Microchip со столь большим объемом памяти. Двухпанельная флэш (еще одна особенность) предусматривает использование на одном МК двух независимых ПО, что позволяет обновлять ПО одной части флэш, в то время как МК выполняет код из другой части. Эти возможности делают МК семейства PIC24F «GB6» отличным выбором для промышленных и вычислительных приложений, медицины и фитнеса, портативных приборов — повсюду, где нужен долгий срок службы батарей, перемещение и хранение данных без применения внешней памяти. Среди таких приложений: электрические измерения, нагрев, вентиляция и кондиционирование, дактилоскопирование, игры.

____В активном режиме МК семейства PIC24F «GB6» потребляют лишь 190 мкА/МГц, а в режиме сна — 3,2 мкА. Имея возможность изменять прошивку с помощью беспроводных технологий, разработчик обеспечивает экономичное, надежное и защищенное обновление своих приложений.

____В состав многофункциональной периферии входят: 24-канальный, 12-разрядный АЦП производительностью 200 Квыб/с; до 12 таймеров; 6 каналов UART и USB-устройство или USB-хост.

____В МК также интегрирована независимая от ядра периферия (CIPs), способная функционировать, не используя ресурсы ядра. В ее состав вошли: конфигурируемая логика (CLC) для работы в режиме реального времени и прямой доступ к памяти (DMA), что позволяет увеличить производительность и снизить энергопотребление.

____Микросхемы PIC24F производятся 64-, 100- и 121-выводных корпусах с флэш-памятью объемом от 128 кбайт до 1 Мбайт.

источник

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

5

.

.

PIC-микроконтроллер Microchip, объединяющий 16-бит ADC, 10 Msps ADC, DAC, USB и LCD.

____Компания Microchip Technology объявила о выпуске нового семейства микроконтроллеров — PIC24FJ128GC010. Семейство PIC24FJ128GC010 отличается расширенной богатой аналоговой периферией, которая включает в себя впервые интегрированный на чип высокоточный АЦП с разрешением 16 бит и АЦП с частотой выборки 10 Msps и разрешением 12 бит, а также ЦАП и два операционных усилителя. Микроконтроллеры выполнены по технологии eXtreme Low Power (XLP), которая максимально увеличивает время жизни батарейки, что важно для автономных медицинских и промышленных устройств.

____Сочетание богатой аналоговой периферии и низкого энергопотребления снижает себестоимость, уменьшает уровень шумов, увеличивает пропускную способность сигнала в портативных медицинских устройствах (например, глюкометре и тонометре) и счетчиках (электроэнергии, газовых расходомерах и др.). Помимо расширенной аналоговой периферии в микроконтроллеры семейства PIC24FJ128GC010 интегрирован ЖК-драйвер, который позволяет управлять ЖК-дисплеями до 472 сегментов. Встроенный USB-модуль может служить для загрузки данных в медицинских приложениях или вывода данных в промышленных устройствах. Измерение емкости можно реализовать благодаря интегрированной mTouch-периферии.

____Интеграция в монокристальном малопотребляющем микроконтроллере 16-разрядного АЦП, USB-модуля и ЖК-драйвера обеспечивает малый форм-фактор устройств с автономным питанием. Применение семейства PIC24FJ128GC010 предусматривает значительное сокращение себестоимости приложений, в сравнении с теми, что выполнены с дискретным набором периферии. При этом обеспечиваются пониженный уровень шума, повышенная пропускная способность, уменьшенные габариты изделия и сокращенный срок разработки.

____Семейство PIC24FJ128GC010 поддерживается отладочной платой для микроконтроллеров PIC24F Intelligent.Integrated.Analog (DM240015). Отладочная плата ориентирована на работу с семействами микроконтроллеров с расширенной аналоговой периферией.

____Семейство PIC24FJ128GC010 доступно уже сегодня для покупки и заказа образцов. PIC24FJ128GC010 (128 кбайт флэш-памяти) и PIC24FJ64GC010 (64 кбайт флэш-памяти) доступны в 100-выводном TQFP и 121-контактном BGA-корпусе, А PIC24FJ128GC006 (128 кбайт флэш-памяти) и PIC24FJ64GC006 (64 кбайт флэш-памяти) — в 64-контактных корпусах TQFP и QFN.

источник

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Imagination откроет доступ к коду RTL реального процессора MIPS в рамках программы MIPSfpga

Imagination откроет доступ к коду RTL реального процессора MIPS в рамках программы MIPSfpga

6

.

.

Imagination откроет доступ к коду RTL реального процессора MIPS в рамках программы MIPSfpga.

Компания Imagination Technologies анонсировала дополнение под названием MIPSfpga к программе Imagination University Programme (IUP), ориентированной на университеты. Благодаря MIPSfpga студенты получают бесплатный доступ к процессору MIPS текущего поколения как к части полного обучающего пакета.

____По словам Imagination, будущие специалисты в области электроники и вычислительной техники, изучающие архитектуру процессоров, впервые могут ознакомиться с кодом RTL реального процессора, что существенно меняет уровень обучения.

____Напомним, архитектура MIPS была разработана в Стэндфордском университете в начале 1980-х годов. В течение десятилетий она используется в учебном процессе, поскольку является элегантным воплощением концепции проектирования процессоров RISC.

____В рамках MIPSfpga компания Imagination предоставляет университетам упрощенный вариант популярного ядра MIPS microAptiv, сконфигурированный специально для академических целей. Ядро microAptiv уже используется в целях обучения и может похвастать широкой экосистемой поддержки, обусловленной наличием многочисленных коммерческих вариантов, включая микроконтроллер PIC32MZ производства Microchip Technology.

____Помимо процессора MIPS в набор материалов, доступных для загрузки, включено руководство по быстрому старту, рекомендации для преподавателей и примеры, которые позволят студентам понять работу процессора и его возможности. Взяв предоставленные материалы за основу, студенты могут спроектировать собственный CPU и реализовать его средствами FPGA. При этом конфигурация процессора выбрана с таким расчетом, чтобы его можно было реализовать на недорогой платформе FPGA. Производитель предлагает руководства по реализации на платформе Digilent Nexys4 (FPGA Xilinx Artix-7).

источник

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

Re: Статьи, заметки, очерки, разное... Микроконтроллеры.

7

.

.

Who Cares About Quantum Computing?

____Every now and then we see a flurry of news about quantum computing. But one recent piece rather focused the mind: a company claimed to have an encryption algorithm you will soon need, when quantum computers render today’s encryption algorithms useless.

____Now to the skeptic, such a claim raises questions. Right away there is curiosity. What is quantum computing (Figure 1)? Is it real? If so, how does it work? And what does it have to do with cryptography? Then there are more personal questions. Is quantum computing going to force me to change my design practices? Am I going to have to learn this stuff?

Figure 1. Even in artists’ renderings, quantum computing elements don’t look like anything from the digital hardware world.

____It turns out these are not easy questions to explore. The literature is mostly in one of two genres. The first form is aimed at general readers, and treats quantum mechanics rather like a satanic cult: dark, possibly dangerous, and you wouldn’t understand anyway. This makes it rather tricky to draw conclusions.

____The second genre is entirely different but equally helpful, written by experts to impress other experts. This form is easily identified by several touchstones: Turing machines, Richard Feynman’s name, Hilbert space, and Hadamard gates, all mentioned within about 75 words, followed by a blizzard of equations with unfamiliar and unexplained nomenclature. Of course you remember what |0> means!

Three Parallel Universes

____One reason this gets so complicated is that important contributions to quantum computing have come from three disciplines with very different vocabularies and interests. The idea began with theoretical physicists. Notably in 1980, physicist Paul Benioff of Argonne National Laboratory described how some quantum-mechanical effects could be used to implement a Turing machine. Two years later, iconic physicist Richard Feynman also raised the question of a computer using quantum behavior.

____The thread was picked up by an entirely different group: computer scientists and mathematicians. Taking the basic ideas of a quantum bit (a qbit) and of reversible unitary transforms (which they called quantum gates, or qgates) from physics, computer scientists explored what kinds of computing you might be able to do if ideal qbits and qgates actually existed. They found cases where such theoretical computers could be far faster than conventional digital computers.

____This result prompted experimental physicists—a third group entirely—to begin trying to build physical devices that could approximate ideal qbits and qgates. That has been a long, resource-eating pursuit that still has not proved that a useful quantum computer is physically possible. But it has offered tantalizing hints.

Some Explanations

____So what is this theoretical computer that we should be interested? For clarity, let’s first eliminate some things that it is not. A quantum computer is not a conventional computer simulating quantum-mechanical phenomena. Nor is it a conventional digital computer build from some post-Moore’s-Law transistors so tiny that they store or switch individual quanta of energy.

____Instead, quantum computers are machines based on unique behaviors predicted by quantum mechanics and utterly like the behavior of classical systems. One is the ability to constrain a particle or group of particles so that some aspect of it has only two discrete quantum base states—call them 0 and 1. (We will dispense with the funny-looking brackets here.) The aspect might be the spin on an electron, the polarization of a photon, or the charge on a quantum dot, for example.

____Second, quantum computing depends on superposition—the counterintuitive ability of a quantity to be in a combination of both 0 and 1 base states simultaneously, until you measure it. Once you measure it, the state reverts to either 0 or 1, and all the rest of the information disappears. Quantum mechanics properly expresses the superimposed state as a sum of the two base states, each multiplied by a complex coefficient and always with a total magnitude of 1. This can also be imagined as a unit vector starting at the origin and ending somewhere on a sphere called the Bloch Sphere (Figure 2). A key here is that the square of the complex coefficient on the 0 base states represents the probability that you will measure the qbit to be in the 0 base state, and likewise for the 1 base state. And when you make a measurement, you will always come up with either exactly a 0 state or exactly a 1 state.

Figure 2. The Bloch Sphere is one way to visualize quantum superposition in a qbit.

____This is important because it allows a qbit to be, conceptually, both a 0 and a 1 simultaneously. And hence a register made up of n qbits can simultaneously “contain” all the possible binary numbers n bits long. This allows a quantum computer to perform a single operation not on just one n-bit integer, but on all possible n-bit integers at once—very substantial parallelism as n gets large.

____Third, quantum computing depends on the ability of a qgate to change those coefficients—and hence your probability of measuring any particular number—in predictable ways. If you start out with all the coefficients in all the qbits equal, and then measure all the qbits in the register, you are equally likely to come up with any string of bits between all zeros and all ones, inclusive. But by running this initial state through a carefully designed sequence of qgates, the quantum computer can manipulate the coefficients so that the pattern you are most likely to measure at the output qbits represents the result of a computation—for instance, it might be highly probable that you will measure the bits of a number that is a perfect square.

A Computer on Paper

____But what does all this have to do with real computing? To answer that, we have to turn our attention from the theoretical physicists to the computer scientists and mathematicians. To do useful work, we would have to be able to place a register of qbits into a known superposition of states. We would need qgates, maybe wires, and some kind of output.

____All this is easy for computer scientists—they can just assume that these ideas exist in real life. They do have to make concessions to quantum mechanics, though. In order not to violate the laws of quantum physics, computer scientists must require that qgates be reversible—you can put a result into the output and get the correct input values at the input. And they must insist that the qgates be unitary transforms. Sparing the matrix algebra, this roughly means that when you put the state of a qbit through a qgate, the state you get out will certainly measure as either a 0 or a 1: the sum of the probabilities from the squares of those coefficients still has to add to exactly one.

____Notice that these qgates, even in theory, are very unlike normal Boolean logic gates. Most Boolean functions aren’t reversible, for instance. There is no way to infer the inputs to a NAND gate from its output unless the output happens to be 0. And of course logic gates only work with 1s and 0s, while the qgates work by rotating the vector inside the Bloch sphere. There really is no close analogy beyond the names.

____The computer scientists worked out that a very small set of qgates is sufficient for emulating a Turing machine—just the set of one-input qgates and a single two-input qgate. The most often used example of the two-input qgate is the controlled NOT (CNOT) gate. This reversible function either flips the vector state of a qbit or leaves it unchanged, depending on the state of a second qbit. It is rather like the quantum analogy to an XOR gate.

Useful Work

____We still haven’t really answered the question of how you would use one of these things. The answer is that if you string enough qgates together in the right pattern, you can prepare the input qbits to represent all possible numbers in your domain of inputs, and at the output of the qgate array you can, in theory, measure the bits that represent values of some useful function.

____An example might help. In 1994, mathematician Peter Shor, then at Bell Labs, developed an algorithm for factoring very large numbers using quantum subroutines. This factoring is a vital problem in applied math because there is no analytical solution: the only way is trial and error, and you can only make the algorithm faster by choosing more cleverly the numbers to try. So when you make the input number very large, the amount of trial and error becomes enormous. This is the basis of RSA-like cryptography algorithms, not at all incidentally. RSA and elliptic-curve cyphers are hard to crack specifically because it is so hard to factor huge numbers.

____Shor’s algorithm combined some traditional computing with two quantum functions that directly accelerate the trial-and-error part by, in effect, trying all possible numbers at the same time (Figure 3). One of these quantum functions performs modular exponentiation, and the other does a quantum version of a fast Fourier transform. For reasons only a mathematician could love, if we put in a set of n qbits prepared so that together they represent all the possible binary numbers up to length n, then in the qgates various superimposed states cancel each other—much like interference between two coherent light beams—and we are left with a distinct pattern of states in the output register.

Figure 3. Shor’s algorithm depends on a core of quantum subroutines to do modulo exponentiation and FFT operations. (drawing courtesy of Tyson Williams)

____This pattern isn’t a prime factor—it is only an intermediate step that allows us to calculate a possible prime factor. That calculation is done by measuring the qbits—remembering that we are only likely, not certain, to measure the most probably state of each qbit—and then to apply a lot of conventional computing in an ordinary CPU to produce the possible factor, and then to test to see if it is really a factor or a false result.

____All of this may sound hopelessly complex and infeasible. But the ability of the quantum exponentiation and FFT algorithms to work on all possible powers of 2 simultaneously to find the largest prime factor makes Shor’s algorithm faster than conventional computing for large numbers using even rather slow theoretical quantum subroutines.

____Shor’s algorithm makes a dramatic example because it is both bafflingly unlike conventional computing and potentially enormously important. But it is not alone. The US National Institute of Standards and Technology (NIST) maintains a large library of quantum computing algorithms in its Quantum Algorithm Zoo, at math.nist.gov/quantum/zoo/.

____Are these algorithms just math exercises? It is too early to tell for sure. But in practice, researchers have actually built laboratory quantum calculators with a few working qbits. These machines have successfully factored the number 15 (at IBM in 2001), unsurprisingly finding 3 and 5, and the current world’s record, 21 (done by a cross-institutional team in 2012). So for small numbers the idea works. Usefully large numbers will have to wait for machines with many more qbits. And that brings up the question of practicality.

The Path to Realization

____In order to construct workable quantum computing devices, we have to achieve a number of implementation milestones. We have to build working qbits—not just five, but thousands. We have to figure out the quantum gates, and the equivalent of wires—unless we can make the gates act directly on the state in the input quantum register. All of these are huge undertakings, and the schedule for their achievement is unpredictable.

____The challenges, unfortunately, come not so much from the novelty of the problems as from the laws of quantum mechanics and classical physics. Perhaps the foremost, and least familiar, is called decoherence. The job of a qbit is to hold a physical thing—an ion, a packet of photons, or an electron, perhaps–in place so that we can manipulate and eventually measure a quantized quantity like charge or spin. For that quantity to behave in a quantum way instead of a classical-physics way, we have to be able to restrict it to a superposition of the two pure base states we’ve been calling 0 and 1.

____But the nature of quantum systems is to couple to things around them, vastly increasing the number of possible base states. Physicists call that blurring away from the pure states decoherence. An analogy might be a coherent laser beam in a waveguide striking an impurity and blurring from a superposition of two modes into completely incoherent light. The job of the physical qbit design is to stave off decoherence for as long as possible.

____This means, in effect, that even a single qbit is a demanding laboratory apparatus, possibly involving lasers or RF transmitters, closely controlled electric and magnetic fields, exact dimensions, special materials, and maybe cryogenic cooling. Using it is essentially performing an elaborate experimental procedure. Even with all this work, today “as long as possible” is measured in tens of microseconds. So you have very little time to perform quantum computations before your qbits have lost their coherence. It is as if the information leaks out.

____Today these limitations preclude large quantum registers or computations that require more than a few microseconds. But research is underway to implement far more extensive arrays of qbits and qgates using microelectronic fabrication techniques.

____The work is itself somewhat incoherent, though, because there is no agreement on what physical phenomenon to use to hold the quantum state. There are qbit designs that quantize the polarization of photons, the charge on electrons trapped in quantum dots, the net spin of super-cooled trapped ions, the charge in a device called a transmon, and various other approaches.

____The kind of qbit you choose will naturally determine how you implement quantum gates. For instance you might use the interaction of RF pulses with internal spins in trapped molecules, or the interaction of beam splitters with photon modes in waveguides. Clearly the subject lies deep within the boundaries of experimental physics. And as mentioned, implementation of qbits or qgates requires considerable external equipment, from digital logic to lasers or RF transmitters and antennas to cryogenic coolers.

____Qbit implementation will also dictate how you measure the state of the qbit. You may need a super-sensitive photometer or bolometer, a resistance bridge, or some other incredibly sensitive device to measure the qbits and resolve the superposition state into a base state. And this process of measuring the qbit state brings up another issue unfamiliar to conventional computing: getting the wrong answer.

Doubt

____There are two main kinds of problems with extracting a base state from a qbit. The first is that you are measuring a quantum superposition, not a classical quantity. Assuming the qbit has remained coherent, you will get one or the other of the base states, but you can’t be sure which: you can only be sure that the probability of your getting a particular state will be the square of the coefficient of that state in the superposition. If you measure a qbit in exactly the same state a hundred times, you should expect to get a distribution of 0s and 1s that converges toward the squares of the coefficients.

____So you don’t know that the base state you measured on any give try is the one that had the highest probability. After you have read out a quantum output register by measuring the bits—thereby setting them all to base states—you have three choices. You can bet that you have the correct answer and go ahead. You can check through conventional computing, as Shor’s algorithm does, to see if the number you read is in fact a valid solution. Or you can repeat the computation a large number of times, either sequentially or in parallel, and take the most frequent result. It is also possible to design your computation so that the answer you want is the probability distribution of the base states rather than a particular binary number. In that case too, repetition is in order.

____That is true even in a theoretical perfect quantum computer. But in a real implementation, there is another issue: good old classical noise. Even if everything goes well, there are no decoherent qbits, and the computation is designed to resolve the answer you want with very high probability, you are still observing the qbits by attempting to measure very, very small physical quantities. Noise happens. Once again, the only solution is either to detect an error by further calculation, or to perform the computation so many times that you are willing to accept any remaining uncertainty in the result. The concept of a guaranteed right answer is rather foreign to quantum computing.

____If this is not painting a rosy picture of the future of quantum computing, take heart. Discovery is under way to find the best choice for qbits—though the answer may turn out to be algorithm-dependent. Microelectronics folk are working on miniaturization of quantum components through new materials and structures—allowing very large arrays of quantum computing devices that could be mass-produced like CPU chips. Computer scientists are developing the equivalent of assemblers and compilers that can convert an algorithm into an arrangement of quantum registers and qgates in a particular technology.

____Is it worth it? Here is one data point. Shor estimated that a modest hybrid quantum/conventional computer could crack a powerful RSA cypher faster than a conventional computer could encrypt it. There have been similar results projected for tasks like sorting, and untangling other similarly hard math-based problems. So yes, there is enough promise here that researchers will keep working. But it might not be good to hold your breath.

Ron Wilson

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

8

.

____В большинстве современных микроконтроллеров, процессоров обработки сигналов и ПЛИС имеются аппаратные и программные ресурсы для поддержки распространенных интерфейсных стандартов SPI и I2C – либо одного из них, либо обоих. Этим интерфейсным стандартам присущи существенные недостатки. Например, пропускная способность I2C может составлять 100 Кбит/с, 400 Кбит/с или 3.4 Мбит/с в стандартном, скоростном и высокоскоростном режимах, соответственно, чего не всегда достаточно для соответствия частоте дискретизации современного периферийного преобразователя данных. Даже без учёта кадрирующих и вспомогательных битов, 12 разрядный АЦП с быстродействием 100 Квыб/с должен передавать данные со скоростью не менее 1.2 Мвыб/с, поддерживаемой только высокоскоростным режимом I2C. Между тем во многих процессорах и контроллерах высокоскоростной режим I2C не предусмотрен, и значит, поддерживать быстрое преобразование данных они не могут.

____Одним из главных преимуществ I2C является сокращённое число проводов, соединяющих ведущее устройство с ведомым. Используя всего два провода плюс землю (GND), ведущий контроллер может и адресоваться к ведомому устройству, и обмениваться с ним данными, в то время как SPI требует трех проводов – для сигналов данных, синхронизации и выбора устройства. Несколько ведомых устройств могут использовать общую шину SPI, но для каждого нужна собственная линия выборки.

____При постоянном росте частоты дискретизации невысокая скорость I2C может ограничивать использование этого интерфейса в некоторых приложениях, побуждая разработчикам выбирать SPI. Однако для SPI требуется дополнительная линия от хост контроллера. В ситуациях, когда свободных выводов микроконтроллера у вас нет, а приложению необходим быстрый интерфейс SPI, можно воспользоваться методом, показанным на Рисунке 1.

____Например, выпускаемый Texas Instruments 12-битный АЦП ADS7816 с быстродействием до 200 Квыб/с на максимальной частоте требует битовой скорости передачи данных 3 Мвыб/с. Процесс преобразования инициируется активным низким уровнем на выводе /CS (выбор кристалла) микросхемы ADS7816. Обратно к высокому уровню /CS возвращается по завершении процесса преобразования, заканчивающегося передачей данных.

____Переход сигнала /CS в низкий уровень происходит по спадающему фронту CLOCK. Постоянная времени пикового детектора, образованного элементами D1, R1 и C1, гарантирует, что уровень /CS не станет высоким до тех пор, пока линия сигнала CLOCK не останется на высоком уровне на протяжении более чем одного периода тактовой частоты (Рисунок 2). Хотя данные, синхронизируемые линией CLOCK, выводятся из IC2, уровень /CS остается низким, и после завершения выгрузки данных сигнал CLOCK переходит в высокое состояние, а затем за ним следует и /CS, подготавливая схему к следующему циклу преобразования.

____Поскольку к концу цикла преобразования конденсатор C1 должен быть разряжен, управляющему контроллеру необходимо задержать запуск следующего преобразования на время, необходимое для полного разряда конденсатора. Продуманным выбором величин R1 и C1 эту задержку можно снизить до трех периодов тактовых импульсов. Кроме того, напряжение на C1 не должно опускаться ниже порогового уровня входа инвертора IC1B до прихода следующего тактового импульса, который восстановит заряд конденсатора. Время заряда C1 определяется выходным напряжением и выходным сопротивлением инвертора IC1A, а время разряда зависит от сопротивления резистора R1 и входного импеданса инвертора IC1B. Чтобы сделать надежную схему, учитывайте допуски номиналов и температурные коэффициенты компонентов, а также разбросы пороговых напряжений и выходных уровней логических элементов.

.

Двухпроводное управление SPI интерфейсом быстродействующего АЦП.

Dan Meeks

Перевод: AlexAAN

Источник

____В большинстве современных микроконтроллеров, процессоров обработки сигналов и ПЛИС имеются аппаратные и программные ресурсы для поддержки распространенных интерфейсных стандартов SPI и I2C – либо одного из них, либо обоих. Этим интерфейсным стандартам присущи существенные недостатки. Например, пропускная способность I2C может составлять 100 Кбит/с, 400 Кбит/с или 3.4 Мбит/с в стандартном, скоростном и высокоскоростном режимах, соответственно, чего не всегда достаточно для соответствия частоте дискретизации современного периферийного преобразователя данных. Даже без учёта кадрирующих и вспомогательных битов, 12 разрядный АЦП с быстродействием 100 Квыб/с должен передавать данные со скоростью не менее 1.2 Мвыб/с, поддерживаемой только высокоскоростным режимом I2C. Между тем во многих процессорах и контроллерах высокоскоростной режим I2C не предусмотрен, и значит, поддерживать быстрое преобразование данных они не могут.

____Одним из главных преимуществ I2C является сокращённое число проводов, соединяющих ведущее устройство с ведомым. Используя всего два провода плюс землю (GND), ведущий контроллер может и адресоваться к ведомому устройству, и обмениваться с ним данными, в то время как SPI требует трех проводов – для сигналов данных, синхронизации и выбора устройства. Несколько ведомых устройств могут использовать общую шину SPI, но для каждого нужна собственная линия выборки.

____При постоянном росте частоты дискретизации невысокая скорость I2C может ограничивать использование этого интерфейса в некоторых приложениях, побуждая разработчикам выбирать SPI. Однако для SPI требуется дополнительная линия от хост контроллера. В ситуациях, когда свободных выводов микроконтроллера у вас нет, а приложению необходим быстрый интерфейс SPI, можно воспользоваться методом, показанным на Рисунке 1.

Рисунок 1. Два инвертора и несколько компонентов могут заменить линию выборки кристалла АЦП на интерфейсе SPI.

____Например, выпускаемый Texas Instruments 12-битный АЦП ADS7816 с быстродействием до 200 Квыб/с на максимальной частоте требует битовой скорости передачи данных 3 Мвыб/с. Процесс преобразования инициируется активным низким уровнем на выводе /CS (выбор кристалла) микросхемы ADS7816. Обратно к высокому уровню /CS возвращается по завершении процесса преобразования, заканчивающегося передачей данных.

____Переход сигнала /CS в низкий уровень происходит по спадающему фронту CLOCK. Постоянная времени пикового детектора, образованного элементами D1, R1 и C1, гарантирует, что уровень /CS не станет высоким до тех пор, пока линия сигнала CLOCK не останется на высоком уровне на протяжении более чем одного периода тактовой частоты (Рисунок 2). Хотя данные, синхронизируемые линией CLOCK, выводятся из IC2, уровень /CS остается низким, и после завершения выгрузки данных сигнал CLOCK переходит в высокое состояние, а затем за ним следует и /CS, подготавливая схему к следующему циклу преобразования.

Рисунок 2. Тактовый сигнал (CLOCK) интерфейса SPI (верхняя диаграмма) синхронизирует вывод данных (нижняя диаграмма), а пиковое детектирование тактовых импульсов (точка A на Рисунке 1) формирует сигнал (предпоследняя диаграмма), подменяющий выбор кристалла.

____Поскольку к концу цикла преобразования конденсатор C1 должен быть разряжен, управляющему контроллеру необходимо задержать запуск следующего преобразования на время, необходимое для полного разряда конденсатора. Продуманным выбором величин R1 и C1 эту задержку можно снизить до трех периодов тактовых импульсов. Кроме того, напряжение на C1 не должно опускаться ниже порогового уровня входа инвертора IC1B до прихода следующего тактового импульса, который восстановит заряд конденсатора. Время заряда C1 определяется выходным напряжением и выходным сопротивлением инвертора IC1A, а время разряда зависит от сопротивления резистора R1 и входного импеданса инвертора IC1B. Чтобы сделать надежную схему, учитывайте допуски номиналов и температурные коэффициенты компонентов, а также разбросы пороговых напряжений и выходных уровней логических элементов.

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

9

.

Mark Hastings, Cypress Semiconductor.

____Чтобы принять оптимальное решение относительно того, что наилучшим образом будет работать в вашем проекте, вы должны понять, как реализуют внутреннюю программируемую логику различные производители микроконтроллеров.

____За последние 25 лет внутренние периферийные устройства микроконтроллеров кардинально изменились. Первоначально многие микроконтроллеры содержали только ОЗУ, ПЗУ и, в некоторых случаях, элементарный таймер. С прогрессом микроконтроллеров дополнительные периферийные модули были включены в устройства стоимостью около доллара или меньше. Теперь таймеры/счётчики, ШИМ и стандартные последовательные интерфейсы, такие как UART, SPI и I2C, стали обычными устройствами в этих недорогих микроконтроллерах. Еще одна важная перемена связана с происходящим переходом от 8-битных устройств к 32-битным при сохранении того же ценового диапазона.

____Тем не менее, даже при использовании этих многофункциональных недорогих микроконтроллеров всегда будет возникать необходимость сопряжения с нестандартными аппаратными интерфейсами или с новыми интерфейсами сторонних компаний, поддержка которых производителями микроконтроллеров не может быть обеспечена в короткие сроки. Зачастую это заставляет разработчиков использовать внешние аппаратные устройства или эмулировать интерфейс программно, используя технологию «bit-banging». Эта технология использует программное переключение линий порта ввода/вывода, обычно для того, чтобы воспроизвести работу последовательного интерфейса. Я тоже пользуюсь этим, когда нужно считывать информацию с порта для декодирования последовательных данных. Использование как внешних устройств, так и «bit-banging» приводит к увеличению стоимости проекта. Со стоимостью дополнительного внешнего оборудования всё очевидно, но для использования программной реализации последовательного интерфейса может также потребоваться более быстрый и, следовательно, более дорогой процессор.

____Наиболее распространенные микроконтроллеры сегодня поддерживают интерфейсы SPI, UART и I2C, но существует много случаев, когда очень полезной может оказаться внутренняя логика, программируемая пользователем. Чтобы решить некоторые из этих проблем, ряд компаний, включая Atmel, Cypress, Microchip и NXP, добавили в свои продукты пользовательскую логику. В основном такими устройствами являются микроконтроллеры с добавленной логикой. Процессор здесь по-прежнему остается основной рабочей лошадкой, а дополнительная логика используется для того, чтобы сделать процессор более эффективным. Обычно такие устройства можно увидеть в бюджетных продуктах, но также они используются в качестве небольших сопроцессоров, чтобы повысить эффективность основного процессора, разгрузив его при работе с низкоуровневыми задачами.

____Что касается FPGA (ПЛИС), они двигались к той же цели, но с другого направления. Уже много лет назад Xilinx и Altera стали добавлять аппаратные и программные процессорные ядра, чтобы создать системы-на-кристалле (СнК). Решения на ПЛИС, как правило, дороже, но когда проект требует значительного количества настраиваемых логических элементов, такой подход может быть экономически оправдан. Эти устройства имеют неоценимое значение для прототипирования специализированных микросхем, реализации малотиражных продуктов, где время выхода на рынок является ключевым, а также создания продуктов, требующих регулярной модернизации оборудования.

____Оба типа этих устройств (микроконтроллеры с логикой и микросхемы ПЛИС с процессорами) обеспечивают гибкую настройку в полевых условиях. После повсеместного распространения устройств на основе Flash-памяти обновление в полевых условиях стало нормой. По началу разработчик имел возможность модернизировать только прошивку, но теперь можно легко обновить как аппаратную часть (логику), так и программную. Устройства от компьютерной мыши до высокоскоростных сетевых маршрутизаторов могут обновляться в рабочих условиях с возможностью перепрограммирования аппаратуры и программ в одном устройстве.

____Упомянутые выше четыре компании (Atmel, Cypress, Microchip и NXP) имеют всю настраиваемую логику, необходимую для того, чтобы помочь разгрузить основной процессор или отказаться от внешней логики. Каждая компания придерживается своего подхода, как в отношении типов предоставляемых логических блоков, так и способов, которым эти блоки взаимодействуют друг с другом и с другими объектами на кристалле, такими как таймеры, UART и линии ввода/вывода.

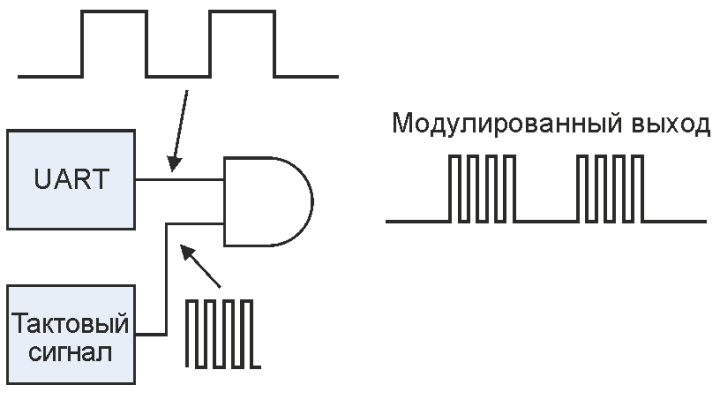

____Для того чтобы принять оптимальное решение относительно того, что будет работать лучше всего в вашем проекте, важно понять, как каждый из этих производителей реализовал внутреннюю программируемую логику. Иногда для того, чтобы исключить внешний компонент или повысить производительность процессора, может быть достаточно простых внутренних вентилей «И» или «ИЛИ». Все четыре метода позволяют пропускать входные и выходные сигналы через настраиваемую логику. Показанный на Рисунке 1 простой пример, поддерживаемый каждым из четырёх типов логических блоков, демонстрирует способ модуляции выходного сигнала UART для ИК-связи. Это не просто факт наличия внутреннего логического элемента «И», но и возможность завести сигналы от тактового генератора или счетчика и выхода UART на элемент «И».

Настраиваемая логика Atmel XMEGA (XCL).

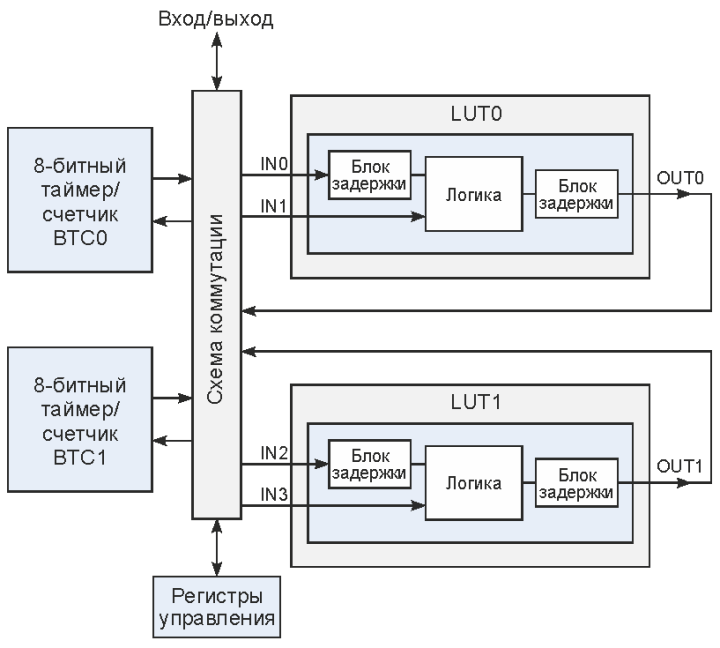

____Блок Atmel XCL содержит два блока LUT (lookup table – таблица истинности) вместе с двумя блоками 8-разрядного таймера/счетчика (Рисунок 2). LUT не должны соединяться с блоками таймера/счетчика, но вместо этого могут быть подключены к UART, блокам EVENT или к линиям ввода/вывода. Два блока LUT могут использоваться в качестве двух независимых двухвходовых модулей или одного модуля с тремя входами. Из логических блоков можно конфигурировать элементы комбинаторной логики, такие как «И», «И-НЕ», «ИЛИ», «ИЛИ-НЕ», «исключающее ИЛИ», «исключающее ИЛИ-НЕ» и мультиплексоры. Помимо этого, с помощью логических блоков можно сформировать элементы последовательной логики, например, D- или RS-триггеры. Благодаря способности подключаться к другим логическим блокам и линиям ввода/вывода, эти простые блоки LUT позволяют разработчику легко сэкономить несколько внешних логических компонентов или освободить циклы процессора. Так, в руководстве по применению Atmel XCL Module (AT01084) объясняется, как может быть сконфигурирован модуль XCL, чтобы обеспечить манчестерское кодирование на выходе UART, не нагружая процессор и не используя внешнюю логику. Устройства AVR XMEGA E содержат один блок XCL.

Конфигурируемая логическая ячейка Microchip (CLC).

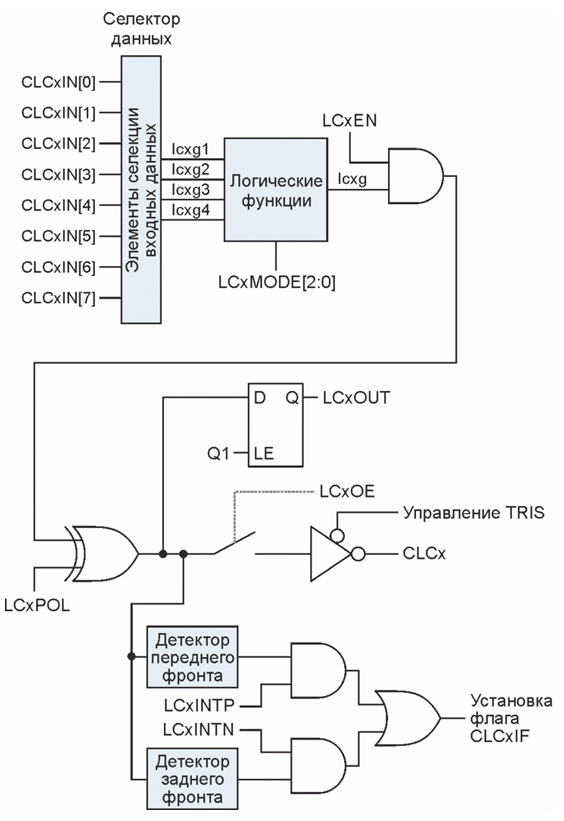

____Конфигурируемая логическая ячейка CLC компании Microchip позволяет пользователю выбрать до четырёх сигналов с восьми входов. Такими входами могут быть комбинации двух линий ввода/вывода, внутренние источники тактовых импульсов, периферийные модули или биты регистров. Эти четыре сигнала затем проходят в программируемый логический блок. Логический блок может быть запрограммирован на выполнение восьми комбинаций таких логических функций как «И-ИЛИ», «исключающее ИЛИ», четырёхвходовая схема «И», RS-триггер или одна из четырёх других комбинаций триггеров. Несколько примеров Microchip предоставляет в своём руководстве по применению Configurable Logic Cell Tips'n Tricks. Один из таких примеров показывает, как следует сконфигурировать эти блоки для декодирования квадратурных сигналов. Без дополнительных логических блоков процессору пришлось бы производить выборку сигналов гораздо чаще, чтобы избежать детектирования ложных переходов, когда один из сигналов находится между переходами, однако при использовании логических блоков процессор прерывается только на реальные смены уровней входных сигналов. Устройства Microchip PIC10(L)F320/322 содержат по одному блоку CLC, состоящему из четырёх блоков, показанных на Рисунке 3.

Конфигурируемая логика NXP (Pattern Match Engine).

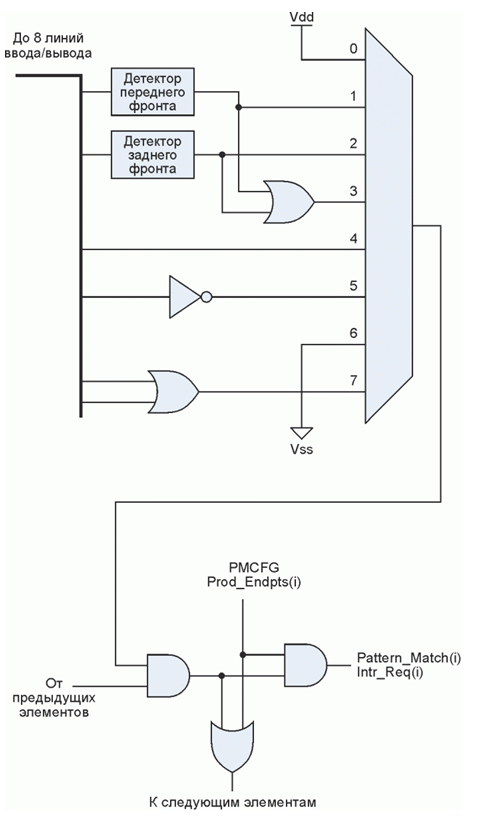

____У NXP есть конфигурируемая пользовательская логика, называемая Pattern Match Engine (Рисунок 4). В качестве входов такого логического блока могут быть выбраны до восьми линий ввода/вывода общего назначения. Эти восемь входов могут быть использованы для создания конъюнктивных членов сложных булевых выражений. Выходы могут использоваться для запуска прерываний, управления специальными линиями ввода/вывода, или же подключаться к следующим логическим блокам или секциям. Другие функции позволяют обнаруживать фронты или срезы импульсов и инвертировать сигналы. Это дополнительное оборудование может быть настроено так, чтобы прерывать процессор только при возникновении сложной (или простой) комбинации событий. Устройства LPC81x компании NXP содержат один блок Pattern Match Engine.

Универсальный цифровой блок Cypress (UDB).

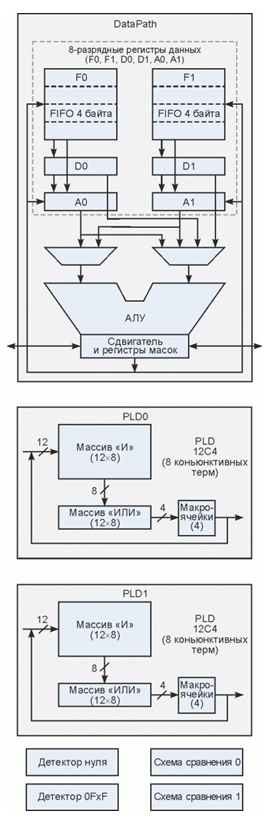

____Cypress выбрала более продвинутое решение, основанное на универсальных цифровых блоках (Universal Digital Blocks – UDB) (Рисунок 5), которое ставит Cypress где-то между подходами, используемыми обсуждавшимися выше тремя производителями и FPGA. UDB состоит из двух программируемых логических устройств (PLD) 12C4 и операционного автомата (DataPath). PLD могут использоваться для управления работой и потоками данных в DataPath, или для реализации универсальной логики и конечных автоматов. DataPath представляет собой настраиваемый блок, реализующий 8-разрядные функции («И», «ИЛИ», сложение, вычитание, инкремент, декремент, «исключающее ИЛИ»), функции сдвига (влево и вправо), а также содержащий два четырёхбайтных буфера FIFO для организации очереди данных. Эти блоки, в свою очередь, могут быть объединены, чтобы получить 16-, 24- или 32-разрядные функции.

____Входы и выходы UDB могут быть подключены к любым линиям ввода/вывода общего назначения, периферийным/компонентным линиям ввода/вывода, прерываниям и т. д. Взаимосвязь между UDB, аналоговыми и цифровыми блоками с фиксированными функциями и линиями ввода/вывода устанавливается с помощью интерфейса цифровых сигналов (Digital Signal Interface, или DSI). UDB могут быть запрограммированы для реализации чего угодно – от простых логических элементов до счётчиков и модулей ШИМ и стандартных последовательных интерфейсов, таких как UART и I2C.

____Пользователю предоставляется несколько опций, с помощью которых он может создать проект на основе UDB. Простейшие логические элементы могут быть либо просто помещены в схему, либо проект может быть создан в среде языка Verilog. Для выполнения разработки без использования Verilog предоставляется пользовательский графический интерфейс. Семейства микроконтроллеров PSoC 3, PSoC 4 и PSoC 5 могут содержать от 4 до 24 таких логических блоков UDB.

Пример создания специализированного интерфейса.

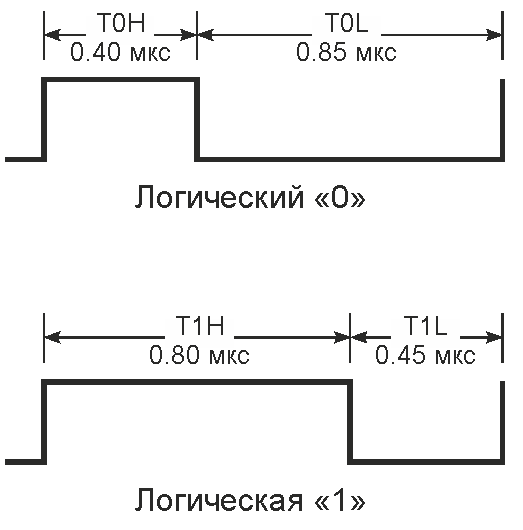

____Недавно я обратил внимание на интересные драйверы RGB светодиодов, предлагаемые компанией Worldsemi. Микросхемы имеют обозначения WS2811, WS2812 и WS2812B, но принцип работы всех устройств одинаков. С помощью лишь одной линии ввода/вывода вы можете управлять такими элементами в количестве 1000 и более. Идея управления столькими RGB драйверами по одной линии показалась мне интригующей. Для соединения этих компонентов использовался специализированный интерфейс, а не SPI, UART или I2C. Сигнал в канале связи является асинхронным, каждый его бит начинается с нарастающего фронта. Логические состояния «1» или «0» определяются длиной импульса, как показано на Рисунке 6.

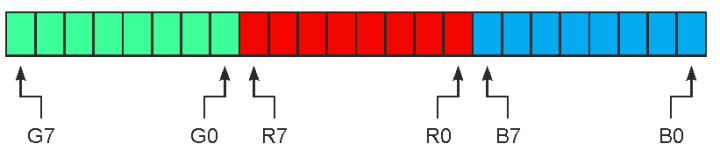

____Каждому RGB светодиоду требуются 24 бита данных – по 8 бит на каждый цвет (красный, зеленый, синий), в формате, изображенном на Рисунке 7.

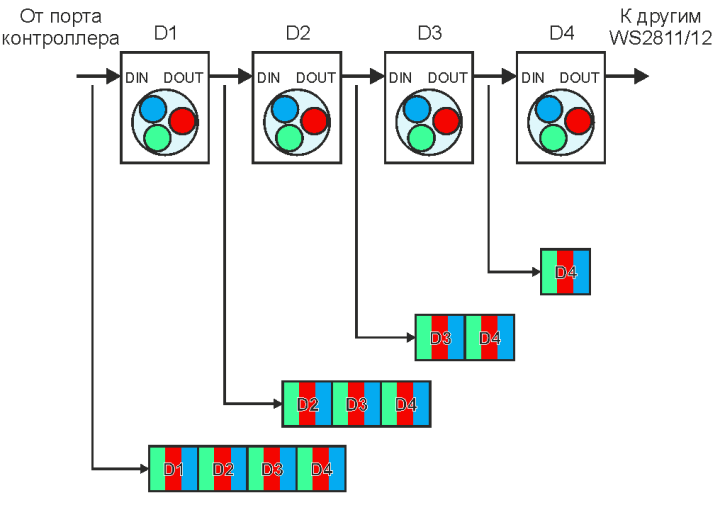

____Устройства WS2811/12 имеют выводы DIN (вход данных) и DOUT (выход данных), с помощью которых они могут быть очень просто соединены в последовательную цепочку. Каждый светодиод сохраняет первые 24 бита, пришедшие по линии DIN, а все остальные данные, как показано на Рисунке 8, ретранслирует на выход DOUT.

____После начала информационного потока каждое устройство ожидает увидеть непрерывную последовательность данных. Если длительность переднего фронта сигнала не превышает 50 мкс, микросхема защёлкивает данные и переходит к ожиданию следующей 24-битной порции предназначающейся ей информации, а все остальное ретранслирует дальше (Рисунок 9).

____Как видите, всё не очень сложно, но сложно адаптировать это к стандартной архитектуре микроконтроллера. Я встречал случаи, когда люди для целей синхронизации использовали интерфейс SPI, но для этого требовалось, по крайней мере, три бита SPI на фактический бит данных, поэтому выигрыш по сравнению с методом программной эмуляции (bit-banging) здесь был бы невелик. Поскольку требования к временной диаграмме достаточно строги, при программной реализации интерфейса до тех пор, пока состояние всех светодиодов не обновится, процессор не мог бы заниматься ничем, кроме отправки управляющих сигналов. Это означает, что во время работы со светодиодами вам придётся запретить все прерывания и не реагировать на любые другие входные сигналы.

____Например, если у вас в цепочке 1000 светодиодов, время обновления составит

(0.40 мкс + 0.85 мкс) × 24 бита × 1000 светодиодов = 30,000 мкс или 30 мс.

____Это не обязательно станет проблемой, но если вы захотите обновлять состояние светодиодов с частотой 30 Гц, вы израсходуете почти 100% ресурсов процессора!

____При написании программы я хотел бы избежать блокирующих кодов или условий, где мне приходилось бы надолго запрещать прерывания. Это особенно важно, если в моей системе есть пользовательский интерфейс или связь с другими процессорами. Таким образом, моя цель заключалась в том, чтобы, насколько это возможно, разгрузить центральный процессор, и возложить основную работу на аппаратуру, как это делают сегодня стандартные внутренние блоки UART или SPI.

____У блоков UDB в составе Cypress PSoC есть пара полезных функций, позволяющих сделать это довольно легко. В DataPath каждого UDB имеются два четырёхбайтных буфера FIFO и сдвиговый регистр. При реализации UART один из них можно использовать для буфера Tx, а другой для буфера Rx. В случае с WS2811/12 мне потребуется только один FIFO и сдвигатель. Я остановился на такой конфигурации аппаратуры, когда для каждого устройства генерируется по одному прерыванию. Обработчик прерываний будет загружать 24 бита (3 байта) и выполнять возврат, пока FIFO не опустеет. Таким образом я получал бы прерывания каждые 30 мкс, и мне не пришлось бы отключить все прерывания и организовать «bit-banging» с разрешением 150 нс или лучше. Выбирая микроконтроллер, я остановился на Cypress PSoC CY8C4245AXI. При оптовых закупках он стоит около $1, имеет четыре UDB и работает на частоте 48 МГц, обеспечивая более чем достаточный запас по скорости и оборудованию, чтобы проделать такой трюк.

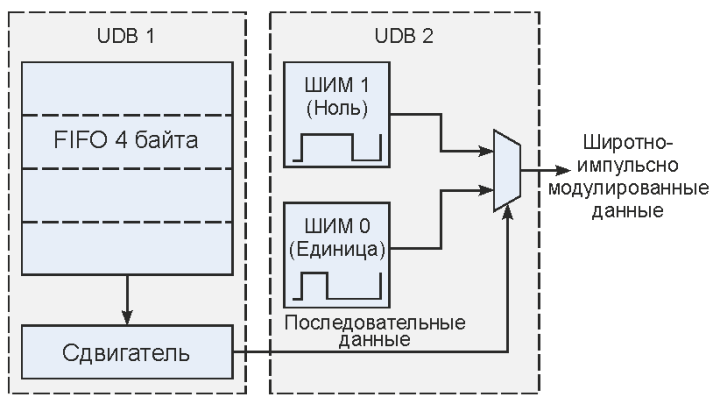

____В моём проекте использовались два из четырех UDB. Один UDB служил для буферизации данных с помощью FIFO и сдвига этих данных для того, чтобы все 24 бита (3 байта), предназначенные одному устройству, могли бы быть записаны за один раз. Второй UDB был задействован для генерации сигнала ШИМ с двумя выходами сравнения. Один формирует логический ноль, другой – логическую единицу. Последовательные данные использовались для управления цифровым мультиплексором для выбора сигнала «1» или «0». Блок-схема показана на Рисунке 10.

____Большинство конъюнктивных членов четырёх программируемых логических устройств (по два на один UDB) в UDB были задействованы для управления операционными автоматами, генерации прерываний и обеспечения функций статуса и управления, но даже на всё это была израсходована лишь половина ресурсов UDB этого недорогого микроконтроллера.

____Далее следует выяснить, насколько такое дополнительное оборудование снижает нагрузку на процессор. Для примера рассмотрим массив из 1000 светодиодов, которые нужно обновлять с частотой 30 Гц. При программной реализации интерфейса это потребует практически 100% ресурсов процессора. Использование программируемых аппаратных средств в устройстве PSoC вызывает прерывания каждые 30 мкс, что, конечно же, весьма ощутимо, но не так уж плохо для ARM Cortex-M0, работающего на частоте 48 МГц. Для проверки загрузки процессора я создал простой цикл, в котором дисплей обновлялся с частотой около 30 Гц. В основном цикле я поочерёдно выводил на линию логические «0» и «1» и с помощью осциллографа подсчитывал количество переключений за период 40 мс. Затем я запретил прерывания, запустил проект снова и сравнил результаты. Непрерывное обновление дисплея отнимало примерно 12% ресурсов процессора, по сравнению с почти 100% при использовании «bit-banging». Соответственно, для внешней связи и пользовательского интерфейса остаётся 88% циклов процессора. Если бы в проект были добавлены DMA (ПДП - устройства прямого доступа к памяти), то нагрузка на процессор снизилась бы с 12% до 2%, или даже меньше. Я использовал самый недорогой (~ $1) из тех микроконтроллеров PSoC, в которых есть UDB, но DMA в нём не было. Впрочем, некоторые старшие модели семейства содержат ПДП.

____Для тестирования этой микросхемы была сделана и использована настоящая «вывеска» с 960 RGB светодиодами, собранными в матрицу 60×16 (Рисунок 11). Она работала точно так, как и ожидалось, и может быть использована в качестве графического интерфейса с поддержкой элементарных линий, прямоугольников, кругов и текста.

____Если у вас есть большая светодиодная панель или простой нестандартный интерфейс, внутренние программируемые аппаратные средства могут оказать огромное влияние на функциональность вашего устройства. Не каждому нестандартному интерфейсу потребуется многобайтный FIFO или полностью аппаратный конечный автомат, но обладание такой гибкостью может дать вам больший выбор вариантов при проектировании, возможность улучшить характеристики и быстро адаптировать существующую конструкцию к требованиям нового проекта.

.

Программируемая логика в микроконтроллерах может дать значительный прирост производительности.

Mark Hastings, Cypress Semiconductor.

EE Times

____Чтобы принять оптимальное решение относительно того, что наилучшим образом будет работать в вашем проекте, вы должны понять, как реализуют внутреннюю программируемую логику различные производители микроконтроллеров.

____За последние 25 лет внутренние периферийные устройства микроконтроллеров кардинально изменились. Первоначально многие микроконтроллеры содержали только ОЗУ, ПЗУ и, в некоторых случаях, элементарный таймер. С прогрессом микроконтроллеров дополнительные периферийные модули были включены в устройства стоимостью около доллара или меньше. Теперь таймеры/счётчики, ШИМ и стандартные последовательные интерфейсы, такие как UART, SPI и I2C, стали обычными устройствами в этих недорогих микроконтроллерах. Еще одна важная перемена связана с происходящим переходом от 8-битных устройств к 32-битным при сохранении того же ценового диапазона.

____Тем не менее, даже при использовании этих многофункциональных недорогих микроконтроллеров всегда будет возникать необходимость сопряжения с нестандартными аппаратными интерфейсами или с новыми интерфейсами сторонних компаний, поддержка которых производителями микроконтроллеров не может быть обеспечена в короткие сроки. Зачастую это заставляет разработчиков использовать внешние аппаратные устройства или эмулировать интерфейс программно, используя технологию «bit-banging». Эта технология использует программное переключение линий порта ввода/вывода, обычно для того, чтобы воспроизвести работу последовательного интерфейса. Я тоже пользуюсь этим, когда нужно считывать информацию с порта для декодирования последовательных данных. Использование как внешних устройств, так и «bit-banging» приводит к увеличению стоимости проекта. Со стоимостью дополнительного внешнего оборудования всё очевидно, но для использования программной реализации последовательного интерфейса может также потребоваться более быстрый и, следовательно, более дорогой процессор.

____Наиболее распространенные микроконтроллеры сегодня поддерживают интерфейсы SPI, UART и I2C, но существует много случаев, когда очень полезной может оказаться внутренняя логика, программируемая пользователем. Чтобы решить некоторые из этих проблем, ряд компаний, включая Atmel, Cypress, Microchip и NXP, добавили в свои продукты пользовательскую логику. В основном такими устройствами являются микроконтроллеры с добавленной логикой. Процессор здесь по-прежнему остается основной рабочей лошадкой, а дополнительная логика используется для того, чтобы сделать процессор более эффективным. Обычно такие устройства можно увидеть в бюджетных продуктах, но также они используются в качестве небольших сопроцессоров, чтобы повысить эффективность основного процессора, разгрузив его при работе с низкоуровневыми задачами.

____Что касается FPGA (ПЛИС), они двигались к той же цели, но с другого направления. Уже много лет назад Xilinx и Altera стали добавлять аппаратные и программные процессорные ядра, чтобы создать системы-на-кристалле (СнК). Решения на ПЛИС, как правило, дороже, но когда проект требует значительного количества настраиваемых логических элементов, такой подход может быть экономически оправдан. Эти устройства имеют неоценимое значение для прототипирования специализированных микросхем, реализации малотиражных продуктов, где время выхода на рынок является ключевым, а также создания продуктов, требующих регулярной модернизации оборудования.

____Оба типа этих устройств (микроконтроллеры с логикой и микросхемы ПЛИС с процессорами) обеспечивают гибкую настройку в полевых условиях. После повсеместного распространения устройств на основе Flash-памяти обновление в полевых условиях стало нормой. По началу разработчик имел возможность модернизировать только прошивку, но теперь можно легко обновить как аппаратную часть (логику), так и программную. Устройства от компьютерной мыши до высокоскоростных сетевых маршрутизаторов могут обновляться в рабочих условиях с возможностью перепрограммирования аппаратуры и программ в одном устройстве.

____Упомянутые выше четыре компании (Atmel, Cypress, Microchip и NXP) имеют всю настраиваемую логику, необходимую для того, чтобы помочь разгрузить основной процессор или отказаться от внешней логики. Каждая компания придерживается своего подхода, как в отношении типов предоставляемых логических блоков, так и способов, которым эти блоки взаимодействуют друг с другом и с другими объектами на кристалле, такими как таймеры, UART и линии ввода/вывода.

____Для того чтобы принять оптимальное решение относительно того, что будет работать лучше всего в вашем проекте, важно понять, как каждый из этих производителей реализовал внутреннюю программируемую логику. Иногда для того, чтобы исключить внешний компонент или повысить производительность процессора, может быть достаточно простых внутренних вентилей «И» или «ИЛИ». Все четыре метода позволяют пропускать входные и выходные сигналы через настраиваемую логику. Показанный на Рисунке 1 простой пример, поддерживаемый каждым из четырёх типов логических блоков, демонстрирует способ модуляции выходного сигнала UART для ИК-связи. Это не просто факт наличия внутреннего логического элемента «И», но и возможность завести сигналы от тактового генератора или счетчика и выхода UART на элемент «И».

Настраиваемая логика Atmel XMEGA (XCL).

____Блок Atmel XCL содержит два блока LUT (lookup table – таблица истинности) вместе с двумя блоками 8-разрядного таймера/счетчика (Рисунок 2). LUT не должны соединяться с блоками таймера/счетчика, но вместо этого могут быть подключены к UART, блокам EVENT или к линиям ввода/вывода. Два блока LUT могут использоваться в качестве двух независимых двухвходовых модулей или одного модуля с тремя входами. Из логических блоков можно конфигурировать элементы комбинаторной логики, такие как «И», «И-НЕ», «ИЛИ», «ИЛИ-НЕ», «исключающее ИЛИ», «исключающее ИЛИ-НЕ» и мультиплексоры. Помимо этого, с помощью логических блоков можно сформировать элементы последовательной логики, например, D- или RS-триггеры. Благодаря способности подключаться к другим логическим блокам и линиям ввода/вывода, эти простые блоки LUT позволяют разработчику легко сэкономить несколько внешних логических компонентов или освободить циклы процессора. Так, в руководстве по применению Atmel XCL Module (AT01084) объясняется, как может быть сконфигурирован модуль XCL, чтобы обеспечить манчестерское кодирование на выходе UART, не нагружая процессор и не используя внешнюю логику. Устройства AVR XMEGA E содержат один блок XCL.

Конфигурируемая логическая ячейка Microchip (CLC).

____Конфигурируемая логическая ячейка CLC компании Microchip позволяет пользователю выбрать до четырёх сигналов с восьми входов. Такими входами могут быть комбинации двух линий ввода/вывода, внутренние источники тактовых импульсов, периферийные модули или биты регистров. Эти четыре сигнала затем проходят в программируемый логический блок. Логический блок может быть запрограммирован на выполнение восьми комбинаций таких логических функций как «И-ИЛИ», «исключающее ИЛИ», четырёхвходовая схема «И», RS-триггер или одна из четырёх других комбинаций триггеров. Несколько примеров Microchip предоставляет в своём руководстве по применению Configurable Logic Cell Tips'n Tricks. Один из таких примеров показывает, как следует сконфигурировать эти блоки для декодирования квадратурных сигналов. Без дополнительных логических блоков процессору пришлось бы производить выборку сигналов гораздо чаще, чтобы избежать детектирования ложных переходов, когда один из сигналов находится между переходами, однако при использовании логических блоков процессор прерывается только на реальные смены уровней входных сигналов. Устройства Microchip PIC10(L)F320/322 содержат по одному блоку CLC, состоящему из четырёх блоков, показанных на Рисунке 3.

Конфигурируемая логика NXP (Pattern Match Engine).

____У NXP есть конфигурируемая пользовательская логика, называемая Pattern Match Engine (Рисунок 4). В качестве входов такого логического блока могут быть выбраны до восьми линий ввода/вывода общего назначения. Эти восемь входов могут быть использованы для создания конъюнктивных членов сложных булевых выражений. Выходы могут использоваться для запуска прерываний, управления специальными линиями ввода/вывода, или же подключаться к следующим логическим блокам или секциям. Другие функции позволяют обнаруживать фронты или срезы импульсов и инвертировать сигналы. Это дополнительное оборудование может быть настроено так, чтобы прерывать процессор только при возникновении сложной (или простой) комбинации событий. Устройства LPC81x компании NXP содержат один блок Pattern Match Engine.

Универсальный цифровой блок Cypress (UDB).

____Cypress выбрала более продвинутое решение, основанное на универсальных цифровых блоках (Universal Digital Blocks – UDB) (Рисунок 5), которое ставит Cypress где-то между подходами, используемыми обсуждавшимися выше тремя производителями и FPGA. UDB состоит из двух программируемых логических устройств (PLD) 12C4 и операционного автомата (DataPath). PLD могут использоваться для управления работой и потоками данных в DataPath, или для реализации универсальной логики и конечных автоматов. DataPath представляет собой настраиваемый блок, реализующий 8-разрядные функции («И», «ИЛИ», сложение, вычитание, инкремент, декремент, «исключающее ИЛИ»), функции сдвига (влево и вправо), а также содержащий два четырёхбайтных буфера FIFO для организации очереди данных. Эти блоки, в свою очередь, могут быть объединены, чтобы получить 16-, 24- или 32-разрядные функции.

____Входы и выходы UDB могут быть подключены к любым линиям ввода/вывода общего назначения, периферийным/компонентным линиям ввода/вывода, прерываниям и т. д. Взаимосвязь между UDB, аналоговыми и цифровыми блоками с фиксированными функциями и линиями ввода/вывода устанавливается с помощью интерфейса цифровых сигналов (Digital Signal Interface, или DSI). UDB могут быть запрограммированы для реализации чего угодно – от простых логических элементов до счётчиков и модулей ШИМ и стандартных последовательных интерфейсов, таких как UART и I2C.

____Пользователю предоставляется несколько опций, с помощью которых он может создать проект на основе UDB. Простейшие логические элементы могут быть либо просто помещены в схему, либо проект может быть создан в среде языка Verilog. Для выполнения разработки без использования Verilog предоставляется пользовательский графический интерфейс. Семейства микроконтроллеров PSoC 3, PSoC 4 и PSoC 5 могут содержать от 4 до 24 таких логических блоков UDB.

Пример создания специализированного интерфейса.

____Недавно я обратил внимание на интересные драйверы RGB светодиодов, предлагаемые компанией Worldsemi. Микросхемы имеют обозначения WS2811, WS2812 и WS2812B, но принцип работы всех устройств одинаков. С помощью лишь одной линии ввода/вывода вы можете управлять такими элементами в количестве 1000 и более. Идея управления столькими RGB драйверами по одной линии показалась мне интригующей. Для соединения этих компонентов использовался специализированный интерфейс, а не SPI, UART или I2C. Сигнал в канале связи является асинхронным, каждый его бит начинается с нарастающего фронта. Логические состояния «1» или «0» определяются длиной импульса, как показано на Рисунке 6.

____Каждому RGB светодиоду требуются 24 бита данных – по 8 бит на каждый цвет (красный, зеленый, синий), в формате, изображенном на Рисунке 7.

____Устройства WS2811/12 имеют выводы DIN (вход данных) и DOUT (выход данных), с помощью которых они могут быть очень просто соединены в последовательную цепочку. Каждый светодиод сохраняет первые 24 бита, пришедшие по линии DIN, а все остальные данные, как показано на Рисунке 8, ретранслирует на выход DOUT.

____После начала информационного потока каждое устройство ожидает увидеть непрерывную последовательность данных. Если длительность переднего фронта сигнала не превышает 50 мкс, микросхема защёлкивает данные и переходит к ожиданию следующей 24-битной порции предназначающейся ей информации, а все остальное ретранслирует дальше (Рисунок 9).

____Как видите, всё не очень сложно, но сложно адаптировать это к стандартной архитектуре микроконтроллера. Я встречал случаи, когда люди для целей синхронизации использовали интерфейс SPI, но для этого требовалось, по крайней мере, три бита SPI на фактический бит данных, поэтому выигрыш по сравнению с методом программной эмуляции (bit-banging) здесь был бы невелик. Поскольку требования к временной диаграмме достаточно строги, при программной реализации интерфейса до тех пор, пока состояние всех светодиодов не обновится, процессор не мог бы заниматься ничем, кроме отправки управляющих сигналов. Это означает, что во время работы со светодиодами вам придётся запретить все прерывания и не реагировать на любые другие входные сигналы.

____Например, если у вас в цепочке 1000 светодиодов, время обновления составит

(0.40 мкс + 0.85 мкс) × 24 бита × 1000 светодиодов = 30,000 мкс или 30 мс.

____Это не обязательно станет проблемой, но если вы захотите обновлять состояние светодиодов с частотой 30 Гц, вы израсходуете почти 100% ресурсов процессора!

____При написании программы я хотел бы избежать блокирующих кодов или условий, где мне приходилось бы надолго запрещать прерывания. Это особенно важно, если в моей системе есть пользовательский интерфейс или связь с другими процессорами. Таким образом, моя цель заключалась в том, чтобы, насколько это возможно, разгрузить центральный процессор, и возложить основную работу на аппаратуру, как это делают сегодня стандартные внутренние блоки UART или SPI.

____У блоков UDB в составе Cypress PSoC есть пара полезных функций, позволяющих сделать это довольно легко. В DataPath каждого UDB имеются два четырёхбайтных буфера FIFO и сдвиговый регистр. При реализации UART один из них можно использовать для буфера Tx, а другой для буфера Rx. В случае с WS2811/12 мне потребуется только один FIFO и сдвигатель. Я остановился на такой конфигурации аппаратуры, когда для каждого устройства генерируется по одному прерыванию. Обработчик прерываний будет загружать 24 бита (3 байта) и выполнять возврат, пока FIFO не опустеет. Таким образом я получал бы прерывания каждые 30 мкс, и мне не пришлось бы отключить все прерывания и организовать «bit-banging» с разрешением 150 нс или лучше. Выбирая микроконтроллер, я остановился на Cypress PSoC CY8C4245AXI. При оптовых закупках он стоит около $1, имеет четыре UDB и работает на частоте 48 МГц, обеспечивая более чем достаточный запас по скорости и оборудованию, чтобы проделать такой трюк.