Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

HM-SHA256-FPGA_v001. R0_I1_B0.

RUЭВМ :: Отечественные ЭВМ, ПЭВМ и МВК :: _______вход :: HM-SHA256-FPGA_v001 :: HM-SHA256-FPGA_v001. R0_I0...63_B0+ADDER

Страница 1 из 1 • Поделиться

HM-SHA256-FPGA_v001. R0_I1_B0.

HM-SHA256-FPGA_v001. R0_I1_B0.

1

HM-SHA256-FPGA_v001. R0_I1_B0.

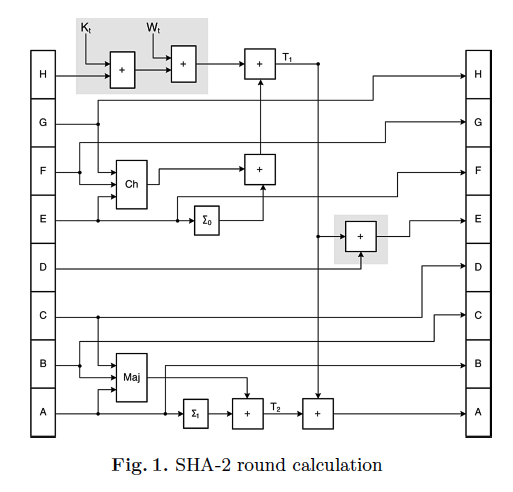

Все итерации абсолютно идентичны. Ниже картинка для наглядности и удобства разработки. Благодаря константам есть возможность избавиться от большого числа "железа" и произвести предварительные расчёты. Хоть и число 65536 кажется огромным, но благодаря детальной, побитовой проработке, в "железе" всё становится намного компактнее. Например сумматор R0_I0_B0_ADDER_A который находится в нулевой ветке, будет отличаться всего на один логический элемент, инвертор НЕ (not), так как поле поиска будет увеличено на единицу с 0x0000 для нулевой ветки до 0x0001 в первой ветке. И соответственно все остальные биты остаются без изменений и данные уже полученные в нулевой ветки можно использовать в первой ветке и т. д.

В чём суть, в обычных майнерах делается одна итерация, и потом данные гоняются с выхода на вход с подстановкой соответствующих слов и константы ki, что происходит последовательно и очень медленно, зато очень компактно в железе. Почему медленно, потому что, прогнав данные в нулевом раунде и получив промежуточный хеш, данные прогоняются через первый раун для получения окончательного хеша и смотрится результат, если он получается больше заданного числа, характеризующего сложность, то поле nonce увеличивается на единицу и снова прогоняется как минимум первый раунд и так до посинения, пока итоговый хеш не окажется равным или меньшим числа, характеризующего сложность.

Хоть на каждом углу и пишут, что алгоритм не возможно распараллелить, но это не так, сам алгоритм частично распараллеливается, например, те же дополнительные 48 слов можно находить параллельно с проходом данных через итерации. Но я всё же считаю правильным если и не полное распараллеливание, так как он прекрасно распараллеливается на 65536 значений в нулевом раунде, и затем каждая ветвь прекрасно распараллеливается на что-то в районе 4 млд. ветвей, то хотя бы на 65536 ветвей в нулевом раунде и уже последовательный перебор в первом раунде этих 4+ млд. значений, но это всё пока мысли в слух, так как пока рано говорить о первом раунде, в виду того, что там огромное количество нулей, благодаря дополнению и всё возможно, всё может быть...

Ну а пока переходим обратно к Раунду0, Итерации1 и ниже картинка:

Так как мы пока просчитали и реализовали упрощённый сумматор только для числа А, в соседней теме, то и будем двигаться дальше от A до H, снизу вверх. Для начала реализуем отдельные компоненты, состоящие из логических элементов, а потом из этих компонентов соберём компонент более высокого уровня иерархии, то есть компонент реализующий итерацию 1. Как уже стало понятно, начальные итерации, благодаря константам сильно можно упростить, уменьшить объём "железа", но в то же время на это уходит много времени, дальнейшие же итерации почти утратят константы и там придётся реализовать скорее все 100% железа, но это будет один универсальный, стандартный компонент, он на данный момент уже частично описан и написан, но всему своё время...

Компонент: R0_I1_B0_ADD_ROTR_0.

Для начала нам нужно разработать блок реализующий данную операцию Σ0, на рисунке кстати эти блоки Σ0 и Σ1 местами перепутаны, но это мелочи, с учётом имеющихся констант, упростить его по максимуму.

Σ0 := (a rotr 2) xor (a rotr 13) xor (a rotr 22)

Для числа А у нас константы, только отдельные биты, что тоже не плохо, возможно блок вообще... колапсирует и не потребуется, поживём, посчитаем, посмотрим...

Вот ниже представлены наши входные данные, наше число А которое поступает на блок, называться он будет так: R0_I1_B0_ADD_ROTR_0, я думаю тут всё понятно, но на всякий случай, расшифрую:

Раунд0, итерация1, ветвь0 тут я думаю всё понятно, далее ADD, это от ADDER сумматор, так как операция исключающее ИЛИ, это сложение по модулю два, ROTR из-за имеющихся циклических сдвигов вправо на 2, 13 и 22, ну и 0 в конце от Σ0. Данные, входные:

Разряд 0: 1

Разряд 1: 0

Разряд 2: 1

Разряд 3: 1

Разряд 4: 0

Разряд 5: W0-5

Разряд 6: S6 (R0_I0_B0_Aout(0))

Разряд 7: S7 (R0_I0_B0_Aout(1))

Разряд 8: S8 (R0_I0_B0_Aout(2))

Разряд 9: 0

Разряд 10: 0

Разряд 11: 1

Разряд 12: 0

Разряд 13: 0

Разряд 14: 0

Разряд 15: 1

Разряд 16: П W0-16

Разряд 17: П W0-17

Разряд 18: П W0-18

Разряд 19: S19 (R0_I0_B0_Aout(3))

Разряд 20: S20 (R0_I0_B0_Aout(4))

Разряд 21: S21 (R0_I0_B0_Aout(5))

Разряд 22: 0

Разряд 23: 0

Разряд 24: П W0-24

Разряд 25: П W0-25

Разряд 26: S26 (R0_I0_B0_Aout(6))

Разряд 27: S27 (R0_I0_B0_Aout(7))

Разряд 28: S28 (R0_I0_B0_Aout(8 ))

Разряд 29: S29 (R0_I0_B0_Aout(9))

Разряд 30: S30 (R0_I0_B0_Aout(10))

Разряд 31: S31 (R0_I0_B0_Aout(11))

Теперь делаем первый циклический сдвиг вправо на 2.

Разряд 0: 1

Разряд 1: 1

Разряд 2: 0

Разряд 3: W0-5

Разряд 4: S6 (R0_I0_B0_Aout(0))

Разряд 5: S7 (R0_I0_B0_Aout(1))

Разряд 6: S8 (R0_I0_B0_Aout(2))

Разряд 7: 0

Разряд 8: 0

Разряд 9: 1

Разряд 10: 0

Разряд 11: 0

Разряд 12: 0

Разряд 13: 1

Разряд 14: П W0-16

Разряд 15: П W0-17

Разряд 16: П W0-18

Разряд 17: S19 (R0_I0_B0_Aout(3))

Разряд 18: S20 (R0_I0_B0_Aout(4))

Разряд 19: S21 (R0_I0_B0_Aout(5))

Разряд 20: 0

Разряд 21: 0

Разряд 22: П W0-24

Разряд 23: П W0-25

Разряд 24: S26 (R0_I0_B0_Aout(6))

Разряд 25: S27 (R0_I0_B0_Aout(7))

Разряд 26: S28 (R0_I0_B0_Aout(8 ))

Разряд 27: S29 (R0_I0_B0_Aout(9))

Разряд 28: S30 (R0_I0_B0_Aout(10))

Разряд 29: S31 (R0_I0_B0_Aout(11))

Разряд 30: 1

Разряд 31: 0

Далее делаем циклический сдвиг вправо изначальных данных на 13.

Разряд 0: 0

Разряд 1: 0

Разряд 2: 1

Разряд 3: П W0-16

Разряд 4: П W0-17

Разряд 5: П W0-18

Разряд 6: S19 (R0_I0_B0_Aout(3))

Разряд 7: S20 (R0_I0_B0_Aout(4))

Разряд 8: S21 (R0_I0_B0_Aout(5))

Разряд 9: 0

Разряд 10: 0

Разряд 11: П W0-24

Разряд 12: П W0-25

Разряд 13: S26 (R0_I0_B0_Aout(6))

Разряд 14: S27 (R0_I0_B0_Aout(7))

Разряд 15: S28 (R0_I0_B0_Aout(8 ))

Разряд 16: S29 (R0_I0_B0_Aout(9))

Разряд 17: S30 (R0_I0_B0_Aout(10))

Разряд 18: S31 (R0_I0_B0_Aout(11))

Разряд 19: 1

Разряд 20: 0

Разряд 21: 1

Разряд 22: 1

Разряд 23: 0

Разряд 24: W0-5

Разряд 25: S6 (R0_I0_B0_Aout(0))

Разряд 26: S7 (R0_I0_B0_Aout(1))

Разряд 27: S8 (R0_I0_B0_Aout(2))

Разряд 28: 0

Разряд 29: 0

Разряд 30: 1

Разряд 31: 0

И теперь мы можем смотреть, какие элементы XOR у нас превратятся в повторители, какие в инверторы, а какие возможно останутся.

Разряд 0: 1 xor Разряд 0: 0 = повторитель, на выходе лог. 1 константа.

Разряд 1: 1 xor Разряд 1: 0 = повторитель, на выходе лог. 1 константа.

Разряд 2: 0 xor Разряд 2: 1 = повторитель, на выходе лог. 1 константа.

Разряд 3: W0-5 xor Разряд 3: П W0-16 = Пока, полноценный LE_XOR2

Разряд 4: S6 (R0_I0_B0_Aout(0)) xor Разряд 4: П W0-17 = Пока, полноценный LE_XOR2

Разряд 5: S7 (R0_I0_B0_Aout(1)) xor Разряд 5: П W0-18 = Пока, полноценный LE_XOR2

Разряд 6: S8 (R0_I0_B0_Aout(2)) xor Разряд 6: S19 (R0_I0_B0_Aout(3)) = Пока, полноценный LE_XOR2

Разряд 7: 0 xor Разряд 7: S20 (R0_I0_B0_Aout(4)) = повторитель, S20 (R0_I0_B0_Aout(4))

Разряд 8: 0 xor Разряд 8: S21 (R0_I0_B0_Aout(5)) = повторитель, S21 (R0_I0_B0_Aout(5))

Разряд 9: 1 xor Разряд 9: 0 = повторитель, на выходе лог. 1 константа.

Разряд 10: 0 xor Разряд 10: 0 = повторитель, на выходе лог. 0 константа.

Разряд 11: 0 xor Разряд 11: П W0-24 = повторитель, W0-24

Разряд 12: 0 xor Разряд 12: П W0-25 = повторитель, W0-25

Разряд 13: 1 xor Разряд 13: S26 (R0_I0_B0_Aout(6)) = инвертор НЕ (not), /R0_I0_B0_Aout(6) = (W0-26)

Разряд 14: П W0-16 xor Разряд 14: S27 (R0_I0_B0_Aout(7)) = Пока, полноценный LE_XOR2

Разряд 15: П W0-17 xor Разряд 15: S28 (R0_I0_B0_Aout(8 )) = Пока, полноценный LE_XOR2

Разряд 16: П W0-18 xor Разряд 16: S29 (R0_I0_B0_Aout(9)) = Пока, полноценный LE_XOR2

Разряд 17: S19 (R0_I0_B0_Aout(3)) xor Разряд 17: S30 (R0_I0_B0_Aout(10)) = Пока, полноценный LE_XOR2

Разряд 18: S20 (R0_I0_B0_Aout(4)) xor Разряд 18: S31 (R0_I0_B0_Aout(11)) = Пока, полноценный LE_XOR2

Разряд 19: S21 (R0_I0_B0_Aout(5)) xor Разряд 19: 1 = инвертор НЕ (not), /R0_I0_B0_Aout(5)

Разряд 20: 0 xor Разряд 20: 0 = повторитель, на выходе лог. 0 константа.

Разряд 21: 0 xor Разряд 21: 1 = повторитель, на выходе лог. 1 константа.

Разряд 22: П W0-24 xor Разряд 22: 1 = инвертор НЕ (not), /W0-24

Разряд 23: П W0-25 xor Разряд 23: 0 = повторитель, W0-25

Разряд 24: S26 (R0_I0_B0_Aout(6)) xor Разряд 24: W0-5 = Пока, полноценный LE_XOR2

Разряд 25: S27 (R0_I0_B0_Aout(7)) xor Разряд 25: S6 (R0_I0_B0_Aout(0)) = Пока, полноценный LE_XOR2

Разряд 26: S28 (R0_I0_B0_Aout(8 )) xor Разряд 26: S7 (R0_I0_B0_Aout(1)) = Пока, полноценный LE_XOR2

Разряд 27: S29 (R0_I0_B0_Aout(9)) xor Разряд 27: S8 (R0_I0_B0_Aout(2)) = Пока, полноценный LE_XOR2

Разряд 28: S30 (R0_I0_B0_Aout(10)) xor Разряд 28: 0 = повторитель, S30 (R0_I0_B0_Aout(10))

Разряд 29: S31 (R0_I0_B0_Aout(11)) xor Разряд 29: 0 = повторитель, S31 (R0_I0_B0_Aout(11))

Разряд 30: 1 xor Разряд 30: 1 = инвертор, но так как две константы, использовать лог. 0 константа.

Разряд 31: 0 xor Разряд 31: 0 = повторитель, на выходе лог. 0 константа.

Вот промежуточные данные, теперь ещё один циклический сдвиг на 22 изначальных данных и будем видеть, что мы имеем на выходе и как сократится окончательно объём "железа".

Далее делаем циклический сдвиг вправо изначальных данных на 22.

Разряд 0: 0

Разряд 1: 0

Разряд 2: П W0-24

Разряд 3: П W0-25

Разряд 4: S26 (R0_I0_B0_Aout(6))

Разряд 5: S27 (R0_I0_B0_Aout(7))

Разряд 6: S28 (R0_I0_B0_Aout(8 ))

Разряд 7: S29 (R0_I0_B0_Aout(9))

Разряд 8: S30 (R0_I0_B0_Aout(10))

Разряд 9: S31 (R0_I0_B0_Aout(11))

Разряд 10: 1

Разряд 11: 0

Разряд 12: 1

Разряд 13: 1

Разряд 14: 0

Разряд 15: W0-5

Разряд 16: S6 (R0_I0_B0_Aout(0))

Разряд 17: S7 (R0_I0_B0_Aout(1))

Разряд 18: S8 (R0_I0_B0_Aout(2))

Разряд 19: 0

Разряд 20: 0

Разряд 21: 1

Разряд 22: 0

Разряд 23: 0

Разряд 24: 0

Разряд 25: 1

Разряд 26: П W0-16

Разряд 27: П W0-17

Разряд 28: П W0-18

Разряд 29: S19 (R0_I0_B0_Aout(3))

Разряд 30: S20 (R0_I0_B0_Aout(4))

Разряд 31: S21 (R0_I0_B0_Aout(5))

И далее:

Разряд 0: 0 xor 1 = константа 1

Разряд 1: 0 xor 1 = константа 1

Разряд 2: П W0-24 xor 1 = инвертор, /W0-24

Разряд 3: П W0-25 xor (W0-5 xor W0-16) = LE_XOR2

Разряд 4: S26 (R0_I0_B0_Aout(6)) xor (R0_I0_B0_Aout(0) xor W0-17) = LE_XOR2

Разряд 5: S27 (R0_I0_B0_Aout(7)) xor (R0_I0_B0_Aout(1) xor W0-18) = LE_XOR2

Разряд 6: S28 (R0_I0_B0_Aout(8 )) xor (R0_I0_B0_Aout(2) xor R0_I0_B0_Aout(3)) = LE_XOR2

Разряд 7: S29 (R0_I0_B0_Aout(9)) xor (R0_I0_B0_Aout(4)) = LE_XOR2

Разряд 8: S30 (R0_I0_B0_Aout(10)) xor (R0_I0_B0_Aout(5)) = LE_XOR2

Разряд 9: S31 (R0_I0_B0_Aout(11)) xor 1 конст. = инвертор, /R0_I0_B0_Aout(11)

Разряд 10: 1 xor 0 константа. = повторитель, 1 конст.

Разряд 11: 0 xor W0-24 = повторитель, W0-24

Разряд 12: 1 xor W0-25 = инвертор, /W0-25

Разряд 13: 1 xor W0-26 = инвертор, /W0-26 (нет смысла ставить инвертор), R0_I0_B0_Aout(6) = /W0-26

Разряд 14: 0 xor (W0-16 xor R0_I0_B0_Aout(7)) = повторитель.

Разряд 15: W0-5 xor (W0-17 xor R0_I0_B0_Aout(8 )) = LE_XOR2

Разряд 16: S6 (R0_I0_B0_Aout(0)) xor (W0-18 xor R0_I0_B0_Aout(9)) = LE_XOR2

Разряд 17: S7 (R0_I0_B0_Aout(1)) xor (R0_I0_B0_Aout(3) xor R0_I0_B0_Aout(10)) = LE_XOR2

Разряд 18: S8 (R0_I0_B0_Aout(2)) xor (R0_I0_B0_Aout(4) xor R0_I0_B0_Aout(11)) = LE_XOR2

Разряд 19: 0 xor /R0_I0_B0_Aout(5) = повторитель! /R0_I0_B0_Aout(5)

Разряд 20: 0 xor 0 константа. = 0 константа.

Разряд 21: 1 xor 1 константа. = 0 константа.

Разряд 22: 0 xor /W0-24 = повторитель.

Разряд 23: 0 xor W0-24 = W0-24 (внутрь компонента не заводить)

Разряд 24: 0 xor (R0_I0_B0_Aout(6) xor W0-5) = повторитель.

Разряд 25: 1 xor (R0_I0_B0_Aout(7) xor R0_I0_B0_Aout(0)) = инвертор.

Разряд 26: П W0-16 xor (R0_I0_B0_Aout(6) xor W0-5)- разряд 24 = LE_XOR2

Разряд 27: П W0-17 xor (R0_I0_B0_Aout(9) xor R0_I0_B0_Aout(2)) = LE_XOR2

Разряд 28: П W0-18 xor R0_I0_B0_Aout(10) = LE_XOR2

Разряд 29: S19 (R0_I0_B0_Aout(3)) xor R0_I0_B0_Aout(11) = LE_XOR2

Разряд 30: S20 (R0_I0_B0_Aout(4)) xor 0 константа. = повторитель, R0_I0_B0_Aout(4)

Разряд 31: S21 (R0_I0_B0_Aout(5)) xor 0 константа. = повторитель, R0_I0_B0_Aout(5)

...

Что-то я задолбался, устал... Буду отдыхать...

- Спойлер:

Вот, теперь мне весело, и можно двигаться дальше, думать, размышлять, извращаться, и рвать всё и вся...

https://cloud.mail.ru/public/iDmL/AjE4Jf3yY

https://cloud.mail.ru/public/3PP2/Fz7473CU4

https://cloud.mail.ru/public/ScJv/axWgjb1Js

Выходные данные числа А, итерация 0 / Входные данные числа А, итерация 1.

Резервная копия: https://cloud.mail.ru/public/sZxC/CDf7tKWXV

.

Последний раз редактировалось: Viktor2312 (Вт Фев 01 2022, 12:22), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

2

Пока черновик, там уже вон в названии компонента ошибка, написано I0, но он находится в итерации 1 (R0_I1_B0_...). Но, она допущена из-за того, что скопировал и подправил название от сумматора для А из нулевой итерации. Ещё раз доказывает, что нужно выжидать время и потом всё проверять и перепроверять, и находишь то, что до этого не видел, не обращал внимания. Хотя и ошибка в названии ни на что не влияет, кроме внесения путаницы, но не люблю, ошибки и опечатки.

Отвлекли меня... Пусть будет так...

Если действовать напрямую в лоб, по формуле Σ0 := (a rotr 2) xor (a rotr 13) xor (a rotr 22), то видно, что потребуется 32 + 32 логических элемента XOR, всего 64 шт. Но, благодаря константам вышло реализовать на 31 логическом элементе, сэкономилось 33 логических элемента.

Предварительно, окончательный вариант:

.

Отвлекли меня... Пусть будет так...

Если действовать напрямую в лоб, по формуле Σ0 := (a rotr 2) xor (a rotr 13) xor (a rotr 22), то видно, что потребуется 32 + 32 логических элемента XOR, всего 64 шт. Но, благодаря константам вышло реализовать на 31 логическом элементе, сэкономилось 33 логических элемента.

Предварительно, окончательный вариант:

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

3

Компонент: R0_I1_B0_MAJ.

Maj := (a and b) xor (a and c) xor (b and c)

Можно преобразовать:

Maj := (a and b) or (c and (a or b))

У нас есть три входных 32-разрядных слова: a, b, c. Входное слово a, оно же A, было найдено в нулевой итерации. Поэтому мы имеем таблицу где указаны входные сигналы и константы слова A.

Входное слово b, оно же B, в первой итерации, это входное слово A из нулевой итерации, и оно представляет из себя константу: B = 0x6A09E667. Так же входное слово c, оно же C, в первой итерации, это входное слово B из нулевой итерации, и оно так же представляет из себя константу: C = 0xBB67AE85.

В данном конкретном случае, нет особого смысла применять преобразованную формулу, поэтому для построения схемы воспользуемся оригинальной:

Maj := (a and b) xor (a and c) xor (b and c)

Maj := (a and 0x6A09E667) xor (a and 0xBB67AE85) xor (0x6A09E667 and 0xBB67AE85)

Константы в третьей скобочке после логического умножения дают нам конкретное число: 0x2A01A605

Maj := (a and 0x6A09E667) xor (a and 0xBB67AE85) xor 0x2A01A605

Теперь по распределительному закону преобразуем первую часть с двумя скобочками:

Maj := (a and (0x6A09E667 xor 0xBB67AE85)) xor 0x2A01A605

теперь вычисляем xor между константами и получаем конкретное число: 0xD16E48E2

Maj := (a and 0xD16E48E2) xor 0x2A01A605

Теперь можно разрабатывать схему, максимально её упрощая из-за имеющихся констант.

(a and 0xD16E48E2)

0xD16E48E2 = 1101 0001 0110 1110 0100 1000 1110 0010

Входные сигналы и константы числа A:

Разряд 0: 1

Разряд 1: 0

Разряд 2: 1

Разряд 3: 1

Разряд 4: 0

Разряд 5: R0_W0-5_IS5

Разряд 6: R0_I0_B0_Aout(0)_IS513

Разряд 7: R0_I0_B0_Aout(1)_IS514

Разряд 8: R0_I0_B0_Aout(2)_IS515

Разряд 9: 0

Разряд 10: 0

Разряд 11: 1

Разряд 12: 0

Разряд 13: 0

Разряд 14: 0

Разряд 15: 1

Разряд 16: R0_W0-16_IS16

Разряд 17: R0_W0-17_IS17

Разряд 18: R0_W0-18_IS18

Разряд 19: R0_I0_B0_Aout(3)_IS516

Разряд 20: R0_I0_B0_Aout(4)_IS517

Разряд 21: R0_I0_B0_Aout(5)_IS518

Разряд 22: 0

Разряд 23: 0

Разряд 24: R0_W0-24_IS24

Разряд 25: R0_W0-25_IS25

Разряд 26: R0_I0_B0_Aout(6)_IS519

Разряд 27: R0_I0_B0_Aout(7)_IS520

Разряд 28: R0_I0_B0_Aout(8 )_IS521

Разряд 29: R0_I0_B0_Aout(9)_IS522

Разряд 30: R0_I0_B0_Aout(10)_IS523

Разряд 31: R0_I0_B0_Aout(11)_IS524

После логического умножения на 0xD16E48E2 = 1101 0001 0110 1110 0100 1000 1110 0010

Разряд 0: 1 and 0 = константа. Лог. 0

Разряд 1: 0 and 1 = константа. Лог. 0

Разряд 2: 1 and 0 = константа. Лог. 0

Разряд 3: 1 and 0 = константа. Лог. 0

Разряд 4: 0 and 0 = константа. Лог. 0

Разряд 5: R0_W0-5_IS5 and 1 = R0_W0-5_IS5

Разряд 6: R0_I0_B0_Aout(0)_IS513 and 1 = R0_I0_B0_Aout(0)_IS513

Разряд 7: R0_I0_B0_Aout(1)_IS514 and 1 = R0_I0_B0_Aout(1)_IS514

Разряд 8: R0_I0_B0_Aout(2)_IS515 and 0 = константа. Лог. 0

Разряд 9: 0 and 0 = константа. Лог. 0

Разряд 10: 0 and 0 = константа. Лог. 0

Разряд 11: 1 and 1 = константа. Лог. 1

Разряд 12: 0 and 0 = константа. Лог. 0

Разряд 13: 0 and 0 = константа. Лог. 0

Разряд 14: 0 and 1 = константа. Лог. 0

Разряд 15: 1 and 0 = константа. Лог. 0

Разряд 16: R0_W0-16_IS16 and 0 = константа. Лог. 0

Разряд 17: R0_W0-17_IS17 and 1 = R0_W0-17_IS17

Разряд 18: R0_W0-18_IS18 and 1 = R0_W0-18_IS18

Разряд 19: R0_I0_B0_Aout(3)_IS516 and 1 = R0_I0_B0_Aout(3)_IS516

Разряд 20: R0_I0_B0_Aout(4)_IS517 and 0 = константа. Лог. 0

Разряд 21: R0_I0_B0_Aout(5)_IS518 and 1 = R0_I0_B0_Aout(5)_IS518

Разряд 22: 0 and 1 = константа. Лог. 0

Разряд 23: 0 and 0 = константа. Лог. 0

Разряд 24: R0_W0-24_IS24 and 1 = R0_W0-24_IS24

Разряд 25: R0_W0-25_IS25 and 0 = константа. Лог. 0

Разряд 26: R0_I0_B0_Aout(6)_IS519 and 0 = константа. Лог. 0

Разряд 27: R0_I0_B0_Aout(7)_IS520 and 0 = константа. Лог. 0

Разряд 28: R0_I0_B0_Aout(8 )_IS521 and 1 = R0_I0_B0_Aout(8 )_IS521

Разряд 29: R0_I0_B0_Aout(9)_IS522 and 0 = константа. Лог. 0

Разряд 30: R0_I0_B0_Aout(10)_IS523 and 1 = R0_I0_B0_Aout(10)_IS523

Разряд 31: R0_I0_B0_Aout(11)_IS524 and 1 = R0_I0_B0_Aout(11)_IS524

Теперь имеем:

Разряд 0: константа. Лог. 0

Разряд 1: константа. Лог. 0

Разряд 2: константа. Лог. 0

Разряд 3: константа. Лог. 0

Разряд 4: константа. Лог. 0

Разряд 5: R0_W0-5_IS5

Разряд 6: R0_I0_B0_Aout(0)_IS513

Разряд 7: R0_I0_B0_Aout(1)_IS514

Разряд 8: константа. Лог. 0

Разряд 9: константа. Лог. 0

Разряд 10: константа. Лог. 0

Разряд 11: константа. Лог. 1

Разряд 12: константа. Лог. 0

Разряд 13: константа. Лог. 0

Разряд 14: константа. Лог. 0

Разряд 15: константа. Лог. 0

Разряд 16: константа. Лог. 0

Разряд 17: R0_W0-17_IS17

Разряд 18: R0_W0-18_IS18

Разряд 19: R0_I0_B0_Aout(3)_IS516

Разряд 20: константа. Лог. 0

Разряд 21: R0_I0_B0_Aout(5)_IS518

Разряд 22: константа. Лог. 0

Разряд 23: константа. Лог. 0

Разряд 24: R0_W0-24_IS24

Разряд 25: константа. Лог. 0

Разряд 26: константа. Лог. 0

Разряд 27: константа. Лог. 0

Разряд 28: R0_I0_B0_Aout(8 )_IS521

Разряд 29: константа. Лог. 0

Разряд 30: R0_I0_B0_Aout(10)_IS523

Разряд 31: R0_I0_B0_Aout(11)_IS524

Теперь делаем логическую операцию "Исключающее ИЛИ" (суммирование по модулю 2) с числом 0x2A01A605

0x2A01A605 = 0010 1010 0000 0001 1010 0110 0000 0101

Разряд 0: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 1: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 2: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 3: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 4: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 5: R0_W0-5_IS5 xor 0 = R0_W0-5_IS5

Разряд 6: R0_I0_B0_Aout(0)_IS513 xor 0 = R0_I0_B0_Aout(0)_IS513

Разряд 7: R0_I0_B0_Aout(1)_IS514 xor 0 = R0_I0_B0_Aout(1)_IS514

Разряд 8: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 9: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 10: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 11: константа. Лог. 1 xor 0 = константа. Лог. 1

Разряд 12: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 13: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 14: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 15: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 16: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 17: R0_W0-17_IS17 xor 0 = R0_W0-17_IS17

Разряд 18: R0_W0-18_IS18 xor 0 = R0_W0-18_IS18

Разряд 19: R0_I0_B0_Aout(3)_IS516 xor 0 = R0_I0_B0_Aout(3)_IS516

Разряд 20: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 21: R0_I0_B0_Aout(5)_IS518 xor 0 = R0_I0_B0_Aout(5)_IS518

Разряд 22: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 23: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 24: R0_W0-24_IS24 xor 0 = R0_W0-24_IS24

Разряд 25: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 26: константа. Лог. 0 xor 0 = константа. Лог. 0

Разряд 27: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 28: R0_I0_B0_Aout(8 )_IS521 xor 0 = R0_I0_B0_Aout(8 )_IS521

Разряд 29: константа. Лог. 0 xor 1 = константа. Лог. 1

Разряд 30: R0_I0_B0_Aout(10)_IS523 xor 0 = R0_I0_B0_Aout(10)_IS523

Разряд 31: R0_I0_B0_Aout(11)_IS524 xor 0 = R0_I0_B0_Aout(11)_IS524

Таким образом имеем, что никаких логических элементов в этом блоке не требуется, при неизвестных входных данных, нам бы потребовалось 128 логических элементов, а так вышло 0. Мы имеем 11 сигналов из предыдущих компонентов, либо непосредственно разряды входного слова W[0], которые и будут поступать на сумматор Σ0 + Maj.

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» HM-SHA256-FPGA_v001. R0_I0_B0.

» HM-SHA256-FPGA_v001. Main.

» HM-SHA256-SMD-v1. 001_Детали, Datasheet.

» HM-SHA256-SMD-v1. 004_Обсуждение, флейм.

» HM-SHA256-SMD-v1. 005_Итерация0, Раунд0 (ITER0_ADDER_v001).

» HM-SHA256-FPGA_v001. Main.

» HM-SHA256-SMD-v1. 001_Детали, Datasheet.

» HM-SHA256-SMD-v1. 004_Обсуждение, флейм.

» HM-SHA256-SMD-v1. 005_Итерация0, Раунд0 (ITER0_ADDER_v001).

RUЭВМ :: Отечественные ЭВМ, ПЭВМ и МВК :: _______вход :: HM-SHA256-FPGA_v001 :: HM-SHA256-FPGA_v001. R0_I0...63_B0+ADDER

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|