Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

МКБ-8601: Технический проект процессора-эмулятора.

Страница 1 из 1 • Поделиться

МКБ-8601: Технический проект процессора-эмулятора.

МКБ-8601: Технический проект процессора-эмулятора.

1

Технический проект процессора-эмулятора "МКБ-8601".

1. Общие положения.

Процессор-эмулятор “МКБ-8601” разрабатывается и изготавливается в ЛВТА ОИЯИ с участием Опытного производства ОИЯИ.

АВТОРЫ: Давыдов А. Л., Емелин И. А., Кадыков В. М., Левчановский Ф. В., Ломидзе О. Н., Попов М. Ю., Сапожников А. П., Сапожникова Т. Ф., Силин И. Н.

ОТВЕТСТВЕННЫЕ РУКОВОДИТЕЛИ:

- инженерная часть: Левчановский Ф. В.

- программное обеспечение: Силин И. Н.

ЦЕЛЬ ПРОЕКТА: создать универсальную ЭВМ, программно совместимую с БЭСМ-6 и тем самым сохранить накопленное за длительный период её эксплуатации программное обеспечение. Устранить присущие ЭВМ БЭСМ-6 основные недостатки: короткий адрес, малый порядок чисел с плавающей запятой, недостаточный объём оперативной памяти.

В проектируемом процессоре-эмуляторе с точки зрения выполнения команд предусматривается возможность его работы в следующих трех режимах:

- режим исполнения команд БЭСМ-6;

- режим исполнения команд вычислительной системы ЭЛЬБРУС-Б;

- режим исполнения нового списка команд (расширение команд БЭСМ-6 и ЭЛЬБРУС-Б).

Первый режим позволит работать с программами, написанными для БЭСМ-6. Во втором режиме возможно применение процессора-эмулятора в качестве программно совместимой младшей модели вычислительной системы ЭЛЬБРУС-Б. В новый список команд вводятся команды, необходимые для работы с целочисленной арифметикой, команды, обеспечивающие обработку отдельных полей 64-разрядного слова, команды с непосредственным операндом и др., способствующие улучшению рабочих характеристик процессора.

Аппаратно процессор-эмулятор выполняется с привлечением современной технологии микропроцессорных БИС, схем интегральной памяти большого объёма и программируемых логических матриц (ПЛМ).

В архитектуру процессора-эмулятора вводится тег, что будет способствовать созданию эффективной системы программного обеспечения, пословной защите памяти от несанкционированного доступа и удобству отладки программ пользователем.

Предусматривается также возможность работы в многопроцессорном и мультипрограммном режимах, вводятся средства для работы в режиме реального времени. Производительность двухпроцессорного варианта оценивается равной производительности БЭСМ-6.

Данная работа проводится впервые.

Работы, аналогичные представленному проекту, в нашей стране и в странах-участницах не проводились. Известны реализованные проекты в США и ЦЕРН процессоров-эмуляторов 168Е и 38Е, эмулирующих урезанный список команд (только целочисленная арифметика) ЭВМ IВМ 370/168 и SYSTEM 38.

ЗАИНТЕРЕСОВАННЫЕ НАУЧНЫЕ УЧРЕЖДЕНИЯ И ОРГАНИЗАЦИИ: институт Атомной Энергии им. И. В. Курчатова, институт Точной Механики и Вычислительной Техники им. Лебедева, завод “САМ”. Формы сотрудничества в настоящее время не установлены.

2. Физическое и методическое обоснование.

АКТУАЛЬНОСТЬ. Учитывая то, что ЭВМ БЭСМ-6 промышленностью больше не выпускается и в ОИЯИ планируется её вывод из эксплуатации, путь аппаратной модернизации этой машины представляется экономически более целесообразным, чем перенос и переработка огромного объёма оригинального программного обеспечения на другие типы ЭВМ.

Архитектура БЭСМ-6, несмотря на длительный период её эксплуатации, достаточно современна и может быть переведена на новую технологическую базу больших интегральных схем без существенных затрат ресурсов и сил. Малые геометрические размеры разрабатываемого процессора-эмулятора открывают возможности его использования в качестве мощной ЭВМ индивидуального пользования не только как вычислителя, но и в системах управления экспериментальными физическими установками, спектральном анализе, триггерах второго уровня, автоматизированных рабочих местах проектировщика и т.д.

ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ. Самым высоким показателем по параметрам “быстродействие - степень интеграции - потребляемая мощность - структурный базис” на сегодняшний день обладает ТТЛ-технология, поэтому аппаратную реализацию процессора-эмулятора целесообразно выполнить, опираясь на эту технологию. В схемотехнических решениях проекта будут использованы следующие серии интегральных схем: К1804, К1802, К580, К589, К531, К555, К541, К565, К556. В будущем возможен переход на ЭСЛ-технологию, что позволит в 2-3 раза увеличить быстродействие процессора-эмулятора.

На этапах проектирования и изготовления предполагается использование системы логического моделирования “ПУЛЬС” и системы автоматизированного проектирования печатных плат “ТЕХПРО”. Система “ПУЛЬС” позволяет создать математическую модель как отдельных блоков, так и в целом всего процессора-эмулятора, что значительно ускорит его комплексную отладку.

3. Основные методические и технические характеристики процессора-эмулятора.

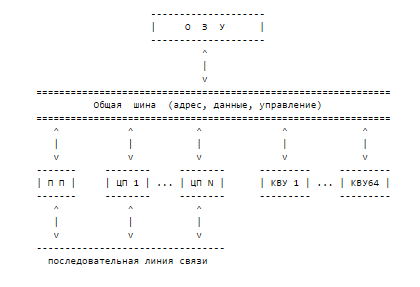

Проектируемая ЭВМ является микропрограммно управляемой машиной общего назначения с модульной организацией. Основными модулями, входящими в состав машины, являются: Оперативное Запоминающее Устройство (ОЗУ), Центральный Процессор (ЦП) (может быть несколько), контроллеры для связи с внешними устройствами (КВУ), а также Пультовой Процессор (ПП). Связь между ними осуществляется через общую шину данных. Кроме того, для загрузки микропрограмм и для исполнения функций инженерного пульта машины существует дополнительная последовательная линия связи между пультовым процессором и центральными процессорами.

3.1. Центральный процессор.

Центральный процессор (ЦП) предназначен для исполнения команд, записанных в ОЗУ.

Функции ЦП:

- Вычисление физических адресов команд и операндов;

- Чтение из ОЗУ машинных команд;

- Приведение команд к единому внутреннему виду;

- Извлечение операндов;

- Выполнение команд;

- Запись результатов в память.

Центральный процессор (ЦП) состоит из:

- блока микропроцессорных секций (МПС), содержащего АЛУ и регистровое запоминающее устройство (РЗУ);

- блока микропрограммного управления, состоящего из преобразователей начального адреса (ПНА), схемы управления адресом микрокоманды (СУАМ), управляющей памяти микропрограмм (ППЗУ И ОЗУ МП), конвейерного регистра (КР);

- ППЗУ констант;

- арифметических блоков, исполняющих умножение (УМН), сдвиги, поиск левой единицы (ПЛЕ) и подсчет числа единиц (N ЕД);

- блоков обмена информацией с общей шиной на 64 разряда для команд и данных и на 8 разрядов для тега (БОИ);

- ОЗУ модификаторов;

- стандартизатора команд, приводящего команды БЭСМ-6 к общему виду с 8-разрядным кодом операции, и схемы размножения знака адресной части команды (АК);

- регистров:

- исполнительного адреса,

- номера группы модификатиров (РНГ),

- номера процесса (РНП),

- регистра счетного времени процесса,

- таймера счетного времени процесса,

- регистра астрономического времени,

- таймера астрономического времени;

Структурная схема ЦП.

3.2. Оперативное запоминающее устройство (ОЗУ).

Максимальная ёмкость оперативного запоминающего устройства - 1 миллион 72 - разрядных слов (9 Мбайт). В ОЗУ используется БИС динамической памяти К565РУ5 емкостью 64Кх1. В связи с повышенным коэффициентом отказов указанной БИС необходим блок коррекции и исправления ошибок - генератор кода Хемминга.

Оперативное запоминающее устройство должно работать в следующих режимах:

- Регенерация памяти;

- Чтение слова с коррекцией 1-кратной ошибки, перезапись исправленного слова и фиксация ошибок кратности 2 и более;

- Запись слова с проверкой и без проверки бита тега “запрещенная запись” (при проверке необходимо предварительное считывание слова);

- Чтение семафорного слова;

- Чтение и запись в режиме блочной передачи;

- Тестирование генератора Хемминга.

Тестирование генератора Хемминга осуществляется с помощью статусного регистра ОЗУ, установленного в блоке управления.

Значения разряда статусного регистра ОЗУ:

- 1 - запрет записи контрольного кода Хемминга в матрицу ОЗУ;

- 0 - нормальный режим.

Под нормальным режимом подразумеваются режимы 1-5. Адресуются к статусному регистру как ко внешнему устройству (ВУ).

Адреса регистров в блоке управления памятью:

- FFFF FFFF - регистр синдрома (только чтение);

- FFFF FFFE - регистр адреса ОЗУ (только чтение);

- FFFF FFFD - статусный регистр ОЗУ;

- 14FFF, 14FFE, 14FFD - адреса этих же регистров для пультового процессора, доступных через его приписку.

3.3. О внешних устройствах.

Каждый тип устройств (диски, ленты, терминалы) подключается к машине через свой контроллер. С каждым контроллером связано некоторое количество последовательных “адресов физической памяти” из диапазона [F0000H - FFFFFH].

Структура адреса внешних устройств :

- 16:13 разряды - номер контроллера = 0, 1, ..., 15;

- 12:1 разряды - адрес внутри контроллера.

Часть адресов, связанных с каждым контроллером, предназначается для задания на обмен, и содержат также адреса регистра состояния и регистра маски всех устройств, подключённых к данному контроллеру. Допускается возможность приписки этой “памяти” к виртуальным страницам пользователей, тем самым открывая для них возможность самостоятельного управления отдельными внешними устройствами. Другая часть адресов контроллера может представлять из себя обменный буфер внешнего устройства, который также можно “приписать” к процессу.

В заказе на обмен находится следующая информация:

- Код операции (8 бит);

- Физический адрес начала массива в памяти (20 бит);

- Длина обменной порции в байтах (16 бит);

- Поле дополнительной информации (20 бит);

- Режим и направление обмена (16 бит);

- Адрес на внешнем устройстве (32 бита);

- Бит запуска контроллера (1 бит).

Таким образом, заказ на работу внешнего устройства должен занимать как минимум 2 слова.

Поскольку к каждому контроллеру может быть подключено в общем случае несколько устройств, желательно по каждому из этих устройств иметь в качестве регистра состояния целое слово. В любой момент времени регистр состояния должен соответствовать текущему состоянию соответствующего устройства.

Адреса контроллера FH используются центральным или пультовым процессорами для доступа к статусному регистру или адресному регистру общей памяти, а также к астрономическим часам и таймеру астрономического времени.

3.3.1. Магнитная лента.

Наиболее целесообразно в процессоре-эмуляторе применять ленты с ЕС - форматом записи, работающие на плотности 800-1600 бит/дюйм. Для управления лентами должен использоваться ленточный контроллер типа СМ ЭВМ.

Минимальный набор операций :

- Чтение блока;

- Запись блока заданной длины (в байтах);

- Движение вперед на 1 блок;

- Движение назад на 1 блок;

- Запись маркера;

- Поиск маркера в прямом направлении;

- Поиск маркера в обратном направлении;

- Стирание (по счетчику байтов);

- Перемотка;

- Разгрузка;

Режим НМЛ БЭСМ-6 предполагается имитировать программно при наличии следующих возможностей контроллера :

- Обмен должен совершаться в зависимости от заданного режима, как с тегами слов, так и без них.

- Должен быть режим чтения, когда в память попадает всё: ЦКС, ПКС, биты четности каждого байта (их можно собирать в теге слова!).

- В заказе на обмен кроме 20-разрядного физического адреса начала обменной порции можно дополнительно указывать еще и номер физической страницы, где продолжается массив информации.

- Окончание обмена происходит по концу блока на ленте либо по исчерпанию заданного счётчика байтов.

- Непременным условием должно быть наличие счётчика прочитанных байтов и признака, что считан маркер.

- Режима чтения с наложением здесь не потребуется.

3.3.2. Магнитный диск (НМД).

Служебная информация на диске:

- Регистр номера модуля;

- Регистр адреса служебных слов;

- Регистр номера физической страницы с информацией;

- Регистры монополизации (по числу модулей), где записывается номер процесса и номер процессора, захватившего диск;

- Командный регистр контроллера;

- Регистр состояния контроллера.

Замечание: регистры номера физической страницы, номера модуля, адреса служебных слов и монополизации находятся на одной странице, командный регистр и регистр состояния - на другой.

Командный регистр контроллера содержит:

- команду;

- адрес по диску;

- признак запуска обмена;

- признак обмена с тегом;

- признак разрешения прерывания по изменению готовности (стоит ли диск, есть ли питание);

- признак разрешения прерывания по концу обмена.

Регистр состояния контроллера содержит:

- тип ошибки;

- текущую команду;

- адрес заменяющей дорожки;

- признак замены дорожек;

- признак окончания операции;

- текущий адрес по диску.

Типы ошибок:

- нет питания;

- нет диска;

- нет готовности;

- ошибка в дорожке;

- нет цилиндра;

- попытка повторного обмена;

- неправильный заказ обмена;

Команды:

- подвод (SЕЕК);

- установка головок на нулевой цилиндр или калибровка (CALIBR);

- чтение (READ);

- запись (WRITE);

- сравнение с памятью (VERIFY);

- форматирование или разметка (запись заголовков без поиска) (FORMAT);

- установка и снятие монополизации отдельного модуля (MONOPOL);

- команда сброса с задержкой на один обмен. Она не должна влиять на текущий обмен в течение достаточно большого времени.

3.4. Пульт-процессор.

Пультовой процессор представляет из себя программируемый терминал с собственной памятью, возможностью доступа к основной памяти и ко всем регистрам центрального процессора. Пультовой процессор выполняет следующие функции:

- Загрузка памяти микропрограмм ЦП.

- Имитация инженерного пульта машины: считывание и запись содержимого регистров ЦП, запуск микропрограммнных тестов.

- Ввод двоичных программ в общую память.

- Запуск диспетчера или тестов на ЦП.

- “Пультовая” отладка программ в ЦП: пошаговое выполнение команд, останов по адресу.

- Обслуживание операторского терминала.

Пультовой процессор может прерывать ЦП или приостанавливать его работу. В свою очередь, деятельность самого ПП может быть прервана по одной из следующих причин :

- По запросу от ЦП;

- По аварии в ЦП;

- По сбою в памяти;

- По инициативе оператора.

В связи с разнородностью исполняемых функций, обмен информацией ПП с различными узлами машины осуществляется 2 способами:

- Через последовательную линию связи - с центральными процессорами (если их несколько) для доступа к регистрам и памяти ЦП, памяти микропрограмм, для организации пультового останова;

- Через общую шину данных - для обмена с общей памятью и внешними устройствами, подключенными к общей шине.

Для реализации функций операторского терминала обмен информацией между ПП и системой предполагается осуществлять следующим образом. Система, сформировав сообщение по известному адресу ОЗУ, посылает запрос ПП, который, получив запрос и зная адрес, принимает сообщение. Аналогично наоборот.

Адреса ВУ в пультовом процессоре:

- FFFF FFFC - регистр маски прерываний от ПП (только запись).

- FFFF FFFB - таймер астрономического времени (рг. RG3, 64р.).

- FFFF FFFA - регистр обмена с ПП (рг. RG2, 64р.).

- FFFF FFF9 - регистр обмена с ПП (рг. RG1, 64р.).

- FFFF FFF8 - часы астрономического времени (рг. RG0, 64р.).

- FFFF 0000 : FFFF 07FF - память двойного доступа в ПП, 72р.

3.5. Описание общей шины.

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» Микро-БЭСМ (МКБ-8601).

» Технический портал радиолюбителей (cqham.ru).

» ПЭВМ "Ириша". Модуль процессора (МП-ВМ80).

» Электроника КР-04. Разработка эмулятора.

» Конфиги для эмулятора EMU80 V4

» Технический портал радиолюбителей (cqham.ru).

» ПЭВМ "Ириша". Модуль процессора (МП-ВМ80).

» Электроника КР-04. Разработка эмулятора.

» Конфиги для эмулятора EMU80 V4

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|