Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

STM32G0. Статьи, заметки, очерки, разное...

Страница 1 из 1 • Поделиться

STM32G0. Статьи, заметки, очерки, разное...

STM32G0. Статьи, заметки, очерки, разное...

1

.

____Компания STMicroelectronics начала выпуск нового бюджетного семейства микроконтроллеров STM32G0. В данной статье рассматриваются особенности STM32G0, анализируются ключевые отличия между STM32G0 и другим бюджетным семейством STM32F0, а также рассказывается о планах STMicroelectronics по дальнейшему развитию нового семейства.

____Появление каждого нового семейства STM32 вызывает повышенный интерес у разработчиков. Микроконтроллеры STM32G0 не являются исключением. Еще бы, бюджетные 32-битные микроконтроллеры с рабочей частотой 64 МГц и малым числом выводов становятся весьма заманчивой альтернативой для 8- и 16-битных процессоров в широком спектре приложений. При этом выражение «с малым числом выводов» оказывается как никогда правдивым – в планах STMicroelectronics значится скорое начало выпуска STM32G0 в 8-выводном корпусном исполнении.

____У некоторых пользователей может возникнуть вопрос: зачем нужны STM32G0, если есть STM32F0? Дело в том, что семейство STM32G0 является результатом глубокой модернизации STM32F0, что обеспечивает новым микроконтроллерам целый ряд преимуществ. Необходимо сразу успокоить поклонников STM32F0: по заявлениям STMicroelectronics, поддержка этого семейства продолжится и прекращение выпуска не ожидается.

____В настоящий момент номенклатура микроконтроллеров STM32 включает 12 семейств (рисунок 1). Семейства можно условно разделить на 4 сегмента:

____Самыми последними с конвейера STMicroelectronics начали сходить представители нового семейства STM32G0. Как видно из рисунка 1, STM32G0 и STM32F0 расположены рядом. Такое соседство не случайно, так как оба семейства представляют бюджетный сегмент микроконтроллеров с небольшим объёмом памяти и базовым набором периферии. Естественно, у разработчиков возникает вопрос, чем отличаются эти семейства, и не является ли STM32G0 своего рода «могильщиком» для STM32F0. Ответ на эти вопросы является неоднозначным. Несмотря на высокий потенциал и целый ряд преимуществ STM32G0, производство STM32F0 будет продолжено. При этом STM32G0 расширяет возможности и области применения 32-битных микроконтроллеров.

____Микроконтроллеры STM32G0 построены на базе процессорного ядра ARM Cortex-M0+, это первое и одно из наиболее важных отличий STM32G0 от семейства STM32F0, в котором используется ядро ARM Cortex-M0.

____Ядро ARM Cortex-M0+ является результатом глубокой модернизации ARM Cortex-M0. При разработке нового процессора основное требование заключалось в существенном повышении энергоэффективности при сохранении высокой производительности. ARM Cortex-M0+ стал первым ARM-процессором с двухуровневым конвейером, в результате чего динамическая потребляемая мощность сократилась примерно на 30% и составила 11,21 мкВт/МГц, в то время как для Cortex-M0 аналогичный показатель составил 16,36 мкВт/МГц. Среди других преимуществ Cortex-M0+ можно отметить новый интерфейс портов ввода/вывода, наличие модуля защиты памяти MPU и прочее.

____При производстве STM32G0 используются более совершенные топологические нормы. Это позволяет увеличить объём памяти, уменьшить габариты и повысить уровень интеграции. Первые два пункта наглядно демонстрирует диаграмма, представленная на рисунке 2. Из неё видно, что, в соответствии с планами STMicroelectronics, семейство STM32G0 существенно перекроет возможности STM32F0. Представители STM32G0 при тех же корпусных исполнениях обеспечат вдвое больший объем памяти (521 Кбайт Flash и 128 Кбайт ОЗУ), а уменьшение размера кристалла позволит создавать 8-выводные корпусные исполнения.

____Повышение степени интеграции совместно с оптимизацией структуры позволило создать более совершенную периферию. Среди ключевых новшеств можно отметить:

____Оптимизация внутренней структуры STM32G0 дала ещё один существенный плюс – уменьшение числа выводов питания (рисунок 3). Если в STM32F0 даже в 32-выводных исполнениях присутствовало по две пары выводов VDD/VSS, то во всех корпусных исполнениях STM32G0 (до 64-выводных включительно) для питания предназначена всего одна пара VDD/VSS. Уменьшение числа выводов питания упрощает трассировку и уменьшает число развязывающих конденсаторов, что в свою очередь делает решение более компактным и бюджетным.

Рис. 3. В отличие от STM32F0 новые микроконтроллеры STM32G0 имеют всего одну пару выводов питания (для всех моделей с числом выводов до 64 включительно).

____Производительность STM32G0 оказывается значительно выше, чем у STM32F0 (рисунок 4). В тесте Drystone микроконтроллеры STM32F0 набирают 38 DMIPS при рабочей частоте 48 МГц (около 0,8 DMIPS/МГц), а STM32G0 демонстрируют пиковую производительность 59,5 DMIPS на частоте 64 МГц (около 0,93 DMIPS/МГц). Преимущество STM32G0 подтверждает и рейтинг CoreMark: 142 у STM32G0, и 106 у STM32F0.

____Главным требованием при разработке процессорного ядра ARM Cortex-M0+ было обеспечение минимального потребления при сохранении производительности. Показатели STM32G0 доказывают, что данная задача была решена. Несмотря на более высокую производительность, STM32G0 потребляют значительно меньше чем STM32F0 (рисунок 5). Это касается работы как в активном режиме, так и в режимах пониженного потребления.

____Кроме того, плюсом STM32F0 является богатейшая линейка моделей (около 100 микроконтроллеров), в то время как номенклатура STM32G0 пока ограничена и будет расширяться в течение ближайших полутора лет.

____В настоящее время номенклатура семейства STM32G0 насчитывает только два десятка моделей, объединённых в три линейки (рисунок 6):

____Линейки STM32G071 и STM32G081 являются наиболее развитыми. В их состав входят полтора десятка микроконтроллеров с рабочей частотой ядра до 64 МГц, объемом Flash 128 или 64 Кбайт и объёмом ОЗУ 36 Кбайт (таблица 1). К услугам пользователей предлагаются различные варианты корпусных исполнений: 28-выводные UFQFPN 28, 32-выводные LQFP 32 и UFQFPN 32, 48-выводные LQFP 48 и UFQFPN 48, 64-выводные LQFP 64 и 25-выводные WLCSP25.

Таблица 1. Номенклатура и параметры микроконтроллеров STM32G0

____На фоне старших семейств STM32 набор периферии STM32G071 кажется достаточно скромным, однако на фоне 8-/16-битных микроконтроллеров он выглядит достаточно внушительно (рисунок 7).

____Аналоговая периферия STM32G071 представлена 12-битным ЦАП, парой компараторов и 12-битным АЦП. Число каналов АЦП достигает 16, а время преобразования составляет 0,4 мкс (2,5 миллиона выборок в секунду). При необходимости пользователь может использовать аппаратную передискретизацию для увеличения разрядности измерений АЦП до 16 бит.

____Микроконтроллеры STM32G071 предлагают большой выбор таймеров:

____Коммуникационные интерфейсы в STM32G071 представлены стандартным набором USART/SPI/I²C/I²S. Кроме того, на борту этих микроконтроллеров присутствует аппаратный контроллер USB PDI. Интерфейс USB PDI (Power Delivery Interface) был разработан для точного соблюдения параметров электропитания USB-портов. При работе с устаревшими версиями USB были часты случаи, когда потребитель отбирал значительно больше энергии, чем допускалось по спецификации. USB PDI исключает такую возможность. Этот интерфейс позволяет определять параметры потребления во время обмена сообщениями при подключении устройств: роли устройств (кто источник, а кто приёмник), профиль источника (напряжение и выходную мощность) и другое.

____Представители линеек STM32G071 и STM32G081 отличаются наличием у последних блоков криптографии AES и генератора случайных числе RNG (рисунок 8 ).

____Стоит отметить, что при разработке STM32G0 вопросам безопасности уделялось большое внимание, и данные микроконтроллеры обеспечивают значительный уровень защиты (рисунок 9). Это касается не только защищённого обмена, но и безопасного обновления ПО, защиты памяти от чтения/записи, закрытия процессов при использовании операционных систем и прочего.

____Номенклатура бюджетной линейки STM32G0 оказывается более скромной и в настоящий момент включает только трёх представителей:

____Все перечисленные модели имеют в своём составе 128 Кбайт Flash и 36 Кбайт ОЗУ, то есть не уступают по объёму памяти старшим линейкам. Однако состав периферии для STM32G070 оказывается значительно скромнее (рисунок 10). Коммуникационные интерфейсы ограничены базовым набором (USART/SPI/I²C/I²S). Аналоговая периферия представлена 12-битным АЦП. По сравнению с STM32G071, число каналов DMA было уменьшено до 5, отсутствует ЦАП, компараторы и 32-битный таймер TIM2.

____Кроме сокращения периферии, бюджетные микроконтроллеры STM32G070 имеют и целый ряд других ограничений по сравнению с STM32G071 (таблица 2). Они характеризуются более узким диапазоном рабочих напряжений и температур, меньшим быстродействием таймеров TIM1 и TIM15, отсутствием калибровки RC-генератора и так далее.

Таблица 2. Сравнение параметров микроконтроллеров из линеек STM32G0 Access lines и Value line.

____Как видно из рисунка 6, компания STMicroelectronics планирует в ближайшем будущем существенно нарастить номенклатуру STM32G0.

____В этом году планируется выпуск трёх линеек микроконтроллеров: STM32G031, STM32G041 и STM32G030.

____Линейка STM32G031 по своим характеристикам должна занять промежуточное место между STM32G071 и STM32G070. Например, набор таймеров у новых микроконтроллеров будет таким же, как и у STM32G071, а вот аналоговая периферия будет состоять только из АЦП (рисунок 11). Объем памяти для STM32G031 и STM32G041 составит 16/32/64 Кбайт Flash и 8 Кбайт ОЗУ.

____Линейка STM32G041 будет отличаться от STM32G031 наличием блоков шифрования AES (рисунок 12).

____Многие разработчики с нетерпением ожидают выпуска STM32G031 и STM32G041 в первую очередь из-за появления моделей с малым числом выводов. Так, например, STM32G031J и STM32G041J будут иметь 8-выводной корпус. Кроме того, предполагается выпуск моделей с 20-, 28-, 32- и 48-выводными корпусами.

____Можно с большой уверенностью предположить, что появление бюджетных 32-битных микроконтроллеров с малым числом выводов существенно потеснит позиции 8-битных процессоров. Поэтому особое внимание будет приковано в первую очередь к новой бюджетной линейке STM32G030. По своим характеристикам она близка к STM32G070, но имеет ограниченный набор таймеров и уменьшенный объём памяти: 32 Кбайт Flash и 8 Кбайт ОЗУ (рисунок 13).

____Несмотря на ограничения памяти и периферии, характеристики STM32G030 на фоне 8- и 16-битных микроконтроллеров выглядят вполне достойно. К этому следует прибавить высокую производительность 32-битного ядра Cortex-M0+, наличие DMA, четыре варианта корпусных исполнений, в том числе 8-выводное. В результате STM32G030 кажется отличной альтернативой для 8-/16-битных систем.

____Кроме того, не стоит забывать, что поклонники STM32G030 смогут использовать те же инструменты разработки, что и для других STM32, а это является огромным плюсом с точки зрения как удобства, так и экономии.

____У разработчиков, использующих STM32, есть широкий выбор интегрированных систем программирования (IDE), как платных, так и бесплатных, например, Athollic TrueSTUDIO, IAR. При этом у пользователей STM32F0 и STM32L0 был дополнительный повод для радости – бесплатная лицензия Keil ARM, открытая именно для этих семейств. Теперь точно такую же привилегию получают пользователи STM32G0.

____Среди огромных плюсов STM32 следует в обязательном порядке упомянуть программу STM32Cube, которая станет незаменимым инструментом и при работе с STM32G0. Кроме того, STMicroelectronics в ближайшее время начнёт ударными темпами выпускать различные программные пакеты и примеры программ для этого нового семейства.

____Что касается аппаратных средств разработки, то сейчас к услугам разработчиков предлагается три отладочных набора: платы NUCLEO-G070RB и NUCLEO-G071RB, а также STM32G081B-EVAL. Платы NUCLEO-G070RB и NUCLEO-G071RB предлагают стандартный набор функций плат NUCLEO (рисунок 14).

____В видеоролике, приведённом ниже, демонстрируется небольшой пример совместной работы отладочной платы NUCLEO-G071RB, конфигуратора STM32CubeMX и компилятора ARM Keil.

____Набор STM32G081B-EVAL представляет собой развитую отладочную платформу с двумя платами расширения, TFT-дисплеем и многочисленными интерфейсами (рисунок 15).

____Новое семейство STM32G0 представляет собой существенно переработанный вариант микроконтроллеров STM32F0. Изменения коснулись технологии изготовления, процессорного ядра, архитектуры системы и возможностей периферии. По сравнению с STM32F0, микроконтроллеры STM32G0 обеспечивают меньшее потребление, увеличенную производительность, расширенный объём памяти и продвинутый функционал периферии.

____Маловыводные бюджетные линейки STM32G070 и STM32G030 станут серьёзной альтернативой для 8-/16-битных микроконтроллеров. При этом пользователи получат дополнительное преимущество от использования единой экосиcтемы STM32.

.

Новое семейство микроконтроллеров STM32G0.

____Компания STMicroelectronics начала выпуск нового бюджетного семейства микроконтроллеров STM32G0. В данной статье рассматриваются особенности STM32G0, анализируются ключевые отличия между STM32G0 и другим бюджетным семейством STM32F0, а также рассказывается о планах STMicroelectronics по дальнейшему развитию нового семейства.

____Появление каждого нового семейства STM32 вызывает повышенный интерес у разработчиков. Микроконтроллеры STM32G0 не являются исключением. Еще бы, бюджетные 32-битные микроконтроллеры с рабочей частотой 64 МГц и малым числом выводов становятся весьма заманчивой альтернативой для 8- и 16-битных процессоров в широком спектре приложений. При этом выражение «с малым числом выводов» оказывается как никогда правдивым – в планах STMicroelectronics значится скорое начало выпуска STM32G0 в 8-выводном корпусном исполнении.

____У некоторых пользователей может возникнуть вопрос: зачем нужны STM32G0, если есть STM32F0? Дело в том, что семейство STM32G0 является результатом глубокой модернизации STM32F0, что обеспечивает новым микроконтроллерам целый ряд преимуществ. Необходимо сразу успокоить поклонников STM32F0: по заявлениям STMicroelectronics, поддержка этого семейства продолжится и прекращение выпуска не ожидается.

Место STM32G0 в семействе микроконтроллеров STM32.

____В настоящий момент номенклатура микроконтроллеров STM32 включает 12 семейств (рисунок 1). Семейства можно условно разделить на 4 сегмента:

- базовые семейства STM32G0 (ядро Cortex-M0+), STM32F0 (ядро Cortex-M0), STM32F1 (ядро Cortex-M3), STM32F3 (ядро Cortex-M4);

- мало потребляющие семейства STM32L0 (ядро Cortex-M0+), STM32L1 (ядро Cortex-M3), STM32L4 (ядро Cortex-M4);

- высокопроизводительные семейства STM32F2 (ядро Cortex-M3), STM32F4 (ядро Cortex-M4), STM32F7 (ядро Cortex-M7), STM32H7 (ядро Cortex-M7);

- беспроводное STM32WB(ядро Cortex-M4).

____Самыми последними с конвейера STMicroelectronics начали сходить представители нового семейства STM32G0. Как видно из рисунка 1, STM32G0 и STM32F0 расположены рядом. Такое соседство не случайно, так как оба семейства представляют бюджетный сегмент микроконтроллеров с небольшим объёмом памяти и базовым набором периферии. Естественно, у разработчиков возникает вопрос, чем отличаются эти семейства, и не является ли STM32G0 своего рода «могильщиком» для STM32F0. Ответ на эти вопросы является неоднозначным. Несмотря на высокий потенциал и целый ряд преимуществ STM32G0, производство STM32F0 будет продолжено. При этом STM32G0 расширяет возможности и области применения 32-битных микроконтроллеров.

____Микроконтроллеры STM32G0 построены на базе процессорного ядра ARM Cortex-M0+, это первое и одно из наиболее важных отличий STM32G0 от семейства STM32F0, в котором используется ядро ARM Cortex-M0.

____Ядро ARM Cortex-M0+ является результатом глубокой модернизации ARM Cortex-M0. При разработке нового процессора основное требование заключалось в существенном повышении энергоэффективности при сохранении высокой производительности. ARM Cortex-M0+ стал первым ARM-процессором с двухуровневым конвейером, в результате чего динамическая потребляемая мощность сократилась примерно на 30% и составила 11,21 мкВт/МГц, в то время как для Cortex-M0 аналогичный показатель составил 16,36 мкВт/МГц. Среди других преимуществ Cortex-M0+ можно отметить новый интерфейс портов ввода/вывода, наличие модуля защиты памяти MPU и прочее.

____При производстве STM32G0 используются более совершенные топологические нормы. Это позволяет увеличить объём памяти, уменьшить габариты и повысить уровень интеграции. Первые два пункта наглядно демонстрирует диаграмма, представленная на рисунке 2. Из неё видно, что, в соответствии с планами STMicroelectronics, семейство STM32G0 существенно перекроет возможности STM32F0. Представители STM32G0 при тех же корпусных исполнениях обеспечат вдвое больший объем памяти (521 Кбайт Flash и 128 Кбайт ОЗУ), а уменьшение размера кристалла позволит создавать 8-выводные корпусные исполнения.

____Повышение степени интеграции совместно с оптимизацией структуры позволило создать более совершенную периферию. Среди ключевых новшеств можно отметить:

- повышение скорости встроенных АЦП. Если 12-битные АЦП микроконтроллеров STM32F0 выполняли преобразования за 1 мкс, то для STM32G0 время преобразования занимает 0,4 мкс;

- появление в составе STM32G0 сразу двух быстродействующих таймеров, способных работать на удвоенной частоте ядра (до 128 МГц);

- встроенный RC-резонатор STM32G0 обеспечивает точность -2/+1,5% во всём диапазоне рабочих температур -40…125°С. В то же время для STM32F0 погрешность составляет ±5%.

____Оптимизация внутренней структуры STM32G0 дала ещё один существенный плюс – уменьшение числа выводов питания (рисунок 3). Если в STM32F0 даже в 32-выводных исполнениях присутствовало по две пары выводов VDD/VSS, то во всех корпусных исполнениях STM32G0 (до 64-выводных включительно) для питания предназначена всего одна пара VDD/VSS. Уменьшение числа выводов питания упрощает трассировку и уменьшает число развязывающих конденсаторов, что в свою очередь делает решение более компактным и бюджетным.

Рис. 3. В отличие от STM32F0 новые микроконтроллеры STM32G0 имеют всего одну пару выводов питания (для всех моделей с числом выводов до 64 включительно).

____Производительность STM32G0 оказывается значительно выше, чем у STM32F0 (рисунок 4). В тесте Drystone микроконтроллеры STM32F0 набирают 38 DMIPS при рабочей частоте 48 МГц (около 0,8 DMIPS/МГц), а STM32G0 демонстрируют пиковую производительность 59,5 DMIPS на частоте 64 МГц (около 0,93 DMIPS/МГц). Преимущество STM32G0 подтверждает и рейтинг CoreMark: 142 у STM32G0, и 106 у STM32F0.

____Главным требованием при разработке процессорного ядра ARM Cortex-M0+ было обеспечение минимального потребления при сохранении производительности. Показатели STM32G0 доказывают, что данная задача была решена. Несмотря на более высокую производительность, STM32G0 потребляют значительно меньше чем STM32F0 (рисунок 5). Это касается работы как в активном режиме, так и в режимах пониженного потребления.

____Кроме того, плюсом STM32F0 является богатейшая линейка моделей (около 100 микроконтроллеров), в то время как номенклатура STM32G0 пока ограничена и будет расширяться в течение ближайших полутора лет.

Существующая номенклатура семейства STM32G0.

____В настоящее время номенклатура семейства STM32G0 насчитывает только два десятка моделей, объединённых в три линейки (рисунок 6):

- STM32G070 ValueLine – бюджетная линейка;

- STM32G071 AccessLine – базовая линейка семейства;

- STM32G081 STM32G0 AccessLines + Encryption – базовая линейка с функциями криптографии.

____Линейки STM32G071 и STM32G081 являются наиболее развитыми. В их состав входят полтора десятка микроконтроллеров с рабочей частотой ядра до 64 МГц, объемом Flash 128 или 64 Кбайт и объёмом ОЗУ 36 Кбайт (таблица 1). К услугам пользователей предлагаются различные варианты корпусных исполнений: 28-выводные UFQFPN 28, 32-выводные LQFP 32 и UFQFPN 32, 48-выводные LQFP 48 и UFQFPN 48, 64-выводные LQFP 64 и 25-выводные WLCSP25.

Таблица 1. Номенклатура и параметры микроконтроллеров STM32G0

____На фоне старших семейств STM32 набор периферии STM32G071 кажется достаточно скромным, однако на фоне 8-/16-битных микроконтроллеров он выглядит достаточно внушительно (рисунок 7).

____Аналоговая периферия STM32G071 представлена 12-битным ЦАП, парой компараторов и 12-битным АЦП. Число каналов АЦП достигает 16, а время преобразования составляет 0,4 мкс (2,5 миллиона выборок в секунду). При необходимости пользователь может использовать аппаратную передискретизацию для увеличения разрядности измерений АЦП до 16 бит.

____Микроконтроллеры STM32G071 предлагают большой выбор таймеров:

- TIM1 – 16-битный таймер с расширенным функционалом и возможностью формирования четырёх ШИМ-сигналов и трёх дополнительных комплементарных сигналов для управления инверторами и трехфазными двигателями. Рабочая частота TIM1 достигает 128 МГц (удвоенная частота ядра);

- TIM2 – 32-битный таймер общего назначения с четырьмя каналами захвата/сравнения;

- TIM3…TIM6, TIM7…TIM14, а также TIM16 и TIM17 – 16-битные таймеры общего назначения с различным числом каналов захвата/сравнения;

- TIM15 – 16-битный таймер общего назначения с рабочей частотой до 128 МГц (удвоенная частота ядра);

- TIM6 и TIM7 – 16-битные таймеры общего назначения. Эти таймеры не имеют внешних каналов захвата/сравнения. Они используются для управления ЦАП или АЦП, а также в качестве простых таймеров.

- LPTIM1 и LPTIM2 – 16-битные таймеры для работы в режимах пониженного потребления, вплоть до режима STOP (не работают в режимах Standby и Shutdown);

- к этому также стоит прибавить системный 32-битный таймер SysTick.

____Коммуникационные интерфейсы в STM32G071 представлены стандартным набором USART/SPI/I²C/I²S. Кроме того, на борту этих микроконтроллеров присутствует аппаратный контроллер USB PDI. Интерфейс USB PDI (Power Delivery Interface) был разработан для точного соблюдения параметров электропитания USB-портов. При работе с устаревшими версиями USB были часты случаи, когда потребитель отбирал значительно больше энергии, чем допускалось по спецификации. USB PDI исключает такую возможность. Этот интерфейс позволяет определять параметры потребления во время обмена сообщениями при подключении устройств: роли устройств (кто источник, а кто приёмник), профиль источника (напряжение и выходную мощность) и другое.

____Представители линеек STM32G071 и STM32G081 отличаются наличием у последних блоков криптографии AES и генератора случайных числе RNG (рисунок 8 ).

____Стоит отметить, что при разработке STM32G0 вопросам безопасности уделялось большое внимание, и данные микроконтроллеры обеспечивают значительный уровень защиты (рисунок 9). Это касается не только защищённого обмена, но и безопасного обновления ПО, защиты памяти от чтения/записи, закрытия процессов при использовании операционных систем и прочего.

____Номенклатура бюджетной линейки STM32G0 оказывается более скромной и в настоящий момент включает только трёх представителей:

- STM32G070KB с 32-выводным корпусом LQFP 32;

- STM32G070CB с 48-выводным корпусом LQFP 48;

- STM32G070RB с 64-выводным корпусом LQFP 64.

____Все перечисленные модели имеют в своём составе 128 Кбайт Flash и 36 Кбайт ОЗУ, то есть не уступают по объёму памяти старшим линейкам. Однако состав периферии для STM32G070 оказывается значительно скромнее (рисунок 10). Коммуникационные интерфейсы ограничены базовым набором (USART/SPI/I²C/I²S). Аналоговая периферия представлена 12-битным АЦП. По сравнению с STM32G071, число каналов DMA было уменьшено до 5, отсутствует ЦАП, компараторы и 32-битный таймер TIM2.

____Кроме сокращения периферии, бюджетные микроконтроллеры STM32G070 имеют и целый ряд других ограничений по сравнению с STM32G071 (таблица 2). Они характеризуются более узким диапазоном рабочих напряжений и температур, меньшим быстродействием таймеров TIM1 и TIM15, отсутствием калибровки RC-генератора и так далее.

Таблица 2. Сравнение параметров микроконтроллеров из линеек STM32G0 Access lines и Value line.

____Как видно из рисунка 6, компания STMicroelectronics планирует в ближайшем будущем существенно нарастить номенклатуру STM32G0.

Планы по развитию семейства STM32G0 в 2019 году.

____В этом году планируется выпуск трёх линеек микроконтроллеров: STM32G031, STM32G041 и STM32G030.

____Линейка STM32G031 по своим характеристикам должна занять промежуточное место между STM32G071 и STM32G070. Например, набор таймеров у новых микроконтроллеров будет таким же, как и у STM32G071, а вот аналоговая периферия будет состоять только из АЦП (рисунок 11). Объем памяти для STM32G031 и STM32G041 составит 16/32/64 Кбайт Flash и 8 Кбайт ОЗУ.

____Линейка STM32G041 будет отличаться от STM32G031 наличием блоков шифрования AES (рисунок 12).

____Многие разработчики с нетерпением ожидают выпуска STM32G031 и STM32G041 в первую очередь из-за появления моделей с малым числом выводов. Так, например, STM32G031J и STM32G041J будут иметь 8-выводной корпус. Кроме того, предполагается выпуск моделей с 20-, 28-, 32- и 48-выводными корпусами.

____Можно с большой уверенностью предположить, что появление бюджетных 32-битных микроконтроллеров с малым числом выводов существенно потеснит позиции 8-битных процессоров. Поэтому особое внимание будет приковано в первую очередь к новой бюджетной линейке STM32G030. По своим характеристикам она близка к STM32G070, но имеет ограниченный набор таймеров и уменьшенный объём памяти: 32 Кбайт Flash и 8 Кбайт ОЗУ (рисунок 13).

____Несмотря на ограничения памяти и периферии, характеристики STM32G030 на фоне 8- и 16-битных микроконтроллеров выглядят вполне достойно. К этому следует прибавить высокую производительность 32-битного ядра Cortex-M0+, наличие DMA, четыре варианта корпусных исполнений, в том числе 8-выводное. В результате STM32G030 кажется отличной альтернативой для 8-/16-битных систем.

____Кроме того, не стоит забывать, что поклонники STM32G030 смогут использовать те же инструменты разработки, что и для других STM32, а это является огромным плюсом с точки зрения как удобства, так и экономии.

Инструменты разработки и отладки.

____У разработчиков, использующих STM32, есть широкий выбор интегрированных систем программирования (IDE), как платных, так и бесплатных, например, Athollic TrueSTUDIO, IAR. При этом у пользователей STM32F0 и STM32L0 был дополнительный повод для радости – бесплатная лицензия Keil ARM, открытая именно для этих семейств. Теперь точно такую же привилегию получают пользователи STM32G0.

____Среди огромных плюсов STM32 следует в обязательном порядке упомянуть программу STM32Cube, которая станет незаменимым инструментом и при работе с STM32G0. Кроме того, STMicroelectronics в ближайшее время начнёт ударными темпами выпускать различные программные пакеты и примеры программ для этого нового семейства.

____Что касается аппаратных средств разработки, то сейчас к услугам разработчиков предлагается три отладочных набора: платы NUCLEO-G070RB и NUCLEO-G071RB, а также STM32G081B-EVAL. Платы NUCLEO-G070RB и NUCLEO-G071RB предлагают стандартный набор функций плат NUCLEO (рисунок 14).

____В видеоролике, приведённом ниже, демонстрируется небольшой пример совместной работы отладочной платы NUCLEO-G071RB, конфигуратора STM32CubeMX и компилятора ARM Keil.

____Набор STM32G081B-EVAL представляет собой развитую отладочную платформу с двумя платами расширения, TFT-дисплеем и многочисленными интерфейсами (рисунок 15).

Заключение.

____Новое семейство STM32G0 представляет собой существенно переработанный вариант микроконтроллеров STM32F0. Изменения коснулись технологии изготовления, процессорного ядра, архитектуры системы и возможностей периферии. По сравнению с STM32F0, микроконтроллеры STM32G0 обеспечивают меньшее потребление, увеличенную производительность, расширенный объём памяти и продвинутый функционал периферии.

____Маловыводные бюджетные линейки STM32G070 и STM32G030 станут серьёзной альтернативой для 8-/16-битных микроконтроллеров. При этом пользователи получат дополнительное преимущество от использования единой экосиcтемы STM32.

.

Re: STM32G0. Статьи, заметки, очерки, разное...

Re: STM32G0. Статьи, заметки, очерки, разное...

2

.

____Серия публикаций основана на материалах цикла STM32G0 Online Training от компании STMicroelectronics. Первая статья посвящена описанию особенностей процессорного ядра, архитектуры и системной периферии микроконтроллеров STM32G0.

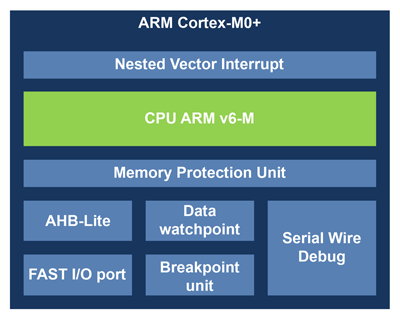

____Микроконтроллеры STM32G0 построены на базе мало потребляющего и высокопроизводительного процессорного ядра ARM Cortex-M0+ (рисунок 1).

____ARM Cortex-M0+ является частью семейства 32-битных процессорных RISC-ядер Cortex-M (рисунок 2). В нём используется архитектура ARMv6-M и двухуровневый конвейер. Системная шина AHB-Lite применяется для взаимодействия с памятью и периферией. Кроме того, для прямого взаимодействия с портами ввода-вывода предназначен специальный порт Fast I/O. В составе ядра также присутствует модуль защиты памяти MPU (Memory protection unit), блоки отладки (DWP и BPU), контроллер прерываний и отладочный интерфейс SWD. Набор инструкций ARM Cortex-M0+ практически полностью состоит из 16-битных команд, за исключением некоторых команд управления. Это позволяет создавать очень компактный программный код.

____Одним из важнейших изменений Cortex-M0+ по сравнению с Cortex-M0 стало уменьшение числа ступеней конвейера. В Cortex-M0+ используется двухуровневый конвейер, который позволяет выполнять обработку команд в два этапа. На первом этапе производится выборка и предварительное декодирование, а на втором декодирование и выполнение. Как уже было сказано, большинство команд ARMv6-M имеет длину 16 бит. Только 6 команд управления имеют длину 32 бита, при том что используются они относительно редко. В результате в идеальном случае за один системный такт может выбираться сразу две 16-битные инструкции.

____На рисунке 3 показан простой пример обработки двух 16-битных команд. На первом такте происходит выборка команд и предварительное декодирование первой команды. На втором такте выборка новых инструкций не производится, вместо этого декодируется и выполняется первая команда, а также предварительно декодируется вторая команда, выбранная на первом такте. На третьем такте декодируется и выполняется вторая команда, а также происходит выборка следующих двух 16-битных команд. Как видно из рисунка 3, на втором такте команды не выбираются, а значит, ничто не мешает выполнять выборку данных.

Рисунок 3, в большом разрешении: Скачать

____К сожалению, при выполнении команд с переходами происходит потеря содержимого конвейера. На рисунке 4 показан пример выполнения команды условного перехода. На первом такте, как обычно, выполняется выборка двух команд: простой («Инструкция 0») и команды перехода («Переход к метке»). На втором такте выполняется инструкция 0. На третьем такте происходит выборка двух новых команд («Инструкция 1» и «Инструкция 2»). Однако в результате выполнения команды условного перехода процессору требуется обработать команду, расположенную по заданному адресу метки («Инструкция N»). В результате содержимое конвейера теряется, так как уже выбранные команды «Инструкция 1» и «Инструкция 2» оказываются неактуальными.

Рисунок 4, в большом разрешении: Скачать

____Спецификация Cortex-M0+ не предусматривает кэш-памяти или встроенного ОЗУ. Однако в микроконтроллерах STM32G0, в отличие от STM32F0, кэш-память добавлена на уровне SoC.

____Шина AHB-Lite подключена к матрице шин (bus matrix) которая обеспечивает взаимодействие процессора с периферией и памятью. Дополнительный порт Single-cycle I/O Port позволяет процессору выполнять доступ к данным за один такт. Производитель микроконтроллеров может произвольно определять диапазон адресов, с которым будет работать этот порт. В микроконтроллерах STM32G0 от STMicroelectronics этот диапазон выделен для регистров GPIO, что позволяет работать с портами ввода-вывода на частоте процессора. В результате переключение выходов занимает всего два такта.

____В составе процессорного ядра Cortex-M0+ есть модуль защиты памяти MPU (Memory protection unit), который поддерживает до восьми областей памяти с независимыми настройками защиты:

____При создании ядра Cortex-M0+ была успешно решена задача по уменьшению уровня потребления. Микроконтроллеры, построенные на базе Cortex-M0+, становятся оптимальным выбором для малопотребляющих устройств с батарейным питанием.

____Матрица межсоединений периферийных блоков IMX (Interconnect Matrix) позволяет периферийным блокам взаимодействовать без участия процессора. Наличие тех или иных связей зависит от линейки контроллеров STM32G0. По этой причине здесь и далее параметры семейства STM32G0 будут рассматриваться на примере наиболее продвинутой линейки – STM32G0x1. Например, в таблице 1 представлены возможные варианты взаимодействия периферии согласно RM0444. Reference manual. STM32G0x1 advanced Arm-based 32-bit MCUs. (Rev.2 2019). Как мы видим, одни и те же периферийные блоки могут выступать и в качестве источников, и в качестве приёмников сигналов управления.

Таблица 1. Возможности взаимодействия периферии в STM32G0x1.

____Рассмотрим несколько конкретных примеров взаимодействия периферийных блоков:

____Связи между периферийными блоками остаются активными даже в режимах пониженного потребления Run, Sleep и Low-power sleep. Кроме того, некоторые блоки могут взаимодействовать также и в режимах Stop 0 и Stop 1. В таблице 2 представлена информация по работе IMX в спящих режимах.

Таблица 2. Возможности использования матрицы межсоединений в режимах пониженного потребления.

____Таким образом, прямые связи между периферийными блоками дают целый ряд преимуществ:

____Системный контроллер SYSCFG в STM32G0 выполняет целый ряд задач:

____Рассмотрим эти задачи подробнее.

____В микроконтроллерах STM32G0 присутствуют встроенные I2C-контроллеры, которые поддерживают три режима скорости передачи: режим Standard-mode с максимальной скоростью обмена данными до 100 Кбит/с, режим Fast-mode с максимальной скоростью 400 Кбит/с, режим Fast-mode Plus со скоростью обмена до 1 Мбит/с. Режим Fast-mode Plus требует повышенной нагрузочной способности от портов микроконтроллера. Активизацию функции повышенной нагрузочной способности осуществляет SYSCFG. Для индивидуальной активизации повышенной нагрузочной способности отдельных выводов используются биты I2C_PA9…10_FMP и I2C_PB6…9_FMP регистра SYSCFG_CFGR1. Для активизации повышенной нагрузочной способности всех выводов, относящихся к I2C, могут использоваться биты I2C1_FMP и I2C2_FMP регистра SYSCFG_CFGR1.

____SYSCFG также отвечает за начальную настройку подтягивающих резисторов на выводах CC1 и CC2, которые используются контроллерами USB Power Delivery. Для управления этой функцией предназначены биты UCPD1_STROBE и UCPD2_STROBE из регистра SYSCFG_CFGR1.

____При работе аналоговых входов STM32G0 при низком напряжении питания (VDD < 2,4 В) рекомендуется использовать специальный повышающий преобразователь. Для его активации предназначен бит BOOSTEN из регистра SYSCFG_CFGR1.

____Инфракрасный интерфейс IRTIM требует модуляции, которая может выполняться либо таймером TIM16, либо передатчиком USART1 или USART6. Выбор источника модуляции производится с помощью бита IR_MOD из регистра SYSCFG_CFGR1. Кроме того, бит IR_POL из того же регистра SYSCFG_CFGR1 определяет инверсию выходного сигнала IR_OUT (0 = не инвертируется, 1 = инвертируется).

____Выводы PA11 и PA12 доступны не во всех корпусных исполнениях. В таких случаях возможна их переадресация на выводы PA9 и PA10 соответственно. Для этого предназначен бит PA11_PA12_RMP из регистра SYSCFG_CFGR1.

____Бит MEM_MODE регистра SYSCFG_CFGR1 определяет выбор памяти доступной по адресу 0x0000 0000 (рисунок 5):

____Регистр SYSCFG_CFGR2 содержит биты статуса и управления, относящиеся к функциям безопасности и надёжности. В частности, биты PBx_CDEN и PAx_CDEN отвечают за подключение защитных диодов между соответствующими выводами микроконтроллера и VDD. Биты ECC_LOCK, PVD_LOCK, SRAM_PARITY_LOCK, LOCKUP_LOCK отвечают за разрешение подачи соответствующих сигналов ошибок на входы Break таймеров TIM1/15/16/17. В этом же регистре располагается флаг SRAM_PEF, выставляемый при возникновении ошибки чётности SRAM.

____Контроллер SYSCFG обеспечивает коммутацию источников прерываний на входы NVIC. При этом SYSCFG имеет 32 регистра SYSCFG_ITLINE0…SYSCFG_ITLINE31, содержащих информацию о статусе всех прерываний по каждому каналу NVIC. Так как к одному и тому же входу контроллера прерываний NVIC могут подключаться несколько источников прерываний, то эти регистры помогают быстро определить, какой из источников был активен. На рисунке 6 представлен пример линии INT5, к которой с помощью вентиля ИЛИ подключены EXTI2 и EXTI3. У SYSCFG для этой линий выделен регистр SYSCFG_ITLINE6, содержащий отдельные флаги по прерываниям EXTI2 и EXTI3. Если возникло прерывание INT5, программа обработчик должна вычитать регистр SYSCFG_ITLINE6 и определить реальный источник прерывания.

____Контроллер прерываний NVIC, реализованный в семействе STM32G0, имеет 32 входа прерываний, позволяет задавать четыре уровня приоритетов и динамически изменять их в процессе работы микроконтроллера, обеспечивает быструю реакцию на прерывания, даёт возможность изменять положение таблицы векторов прерываний.

____NVIC-контроллер процессорного ядра Cortex-M0+ имеет только 32 входа, однако благодаря системному контроллеру SYSCFG количество поддерживаемых источников прерываний оказывается значительно выше. Некоторые входы NVIC получают сигналы от нескольких источников прерываний, объединенных по схеме логического ИЛИ (см. рисунок 6). При этом, как уже отмечалось ранее, для того чтобы определить конкретный источник, вызвавший прерывание, удобно использовать регистры SYSCFG_ITLINE0…SYSCFG_ITLINE31.

____В процессе работы микроконтроллеров нередки случаи, когда несколько источников генерируют прерывания практически одновременно. Для того чтобы определить очерёдность обработки прерываний, используется система приоритетов. В таблице 3 представлены приоритеты источников прерываний для контроллеров STM32G0x1.

____Чем ниже уровень приоритета (первый столбец), тем выше приоритет прерывания. Как видно из таблицы 3, наивысший приоритет имеет сброс Reset (приоритет: -3), далее следуют немаскируемые прерывания NMI (приоритет: -2) и аппаратные ошибки HardFault (приоритет: -1). Приоритеты этих прерываний являются фиксированными и не могут быть изменены пользователем.

____По умолчанию для прерываний с уровнями приоритетов от 3 до 38 используется аппаратный приоритет, указанный в первом столбце таблицы 3. Однако для этих прерываний есть возможность назначения дополнительного программируемого приоритета от 0 до 3. Например, согласно таблице 3 уровень аппаратного приоритета WWDG равен 7, а уровень приоритета PVD равен 8. То есть при одновременной генерации прерываний сначала будет обработано прерывание от WWDG, и лишь потом прерывание от PVD. Однако пользователь может определить программный приоритет для WWDG равным 1, а для PVD равным 0. В таком случае при одновременной генерации прерываний сначала будет обработано прерывание от PVD, а потом прерывание от WWDG. Важно отметить, что программные приоритеты этой группы прерываний могут изменяться динамически в ходе выполнения программы.

Таблица 3. Приоритеты источников прерываний для контроллеров STM32G0x1.

____Обработка прерываний в STM32G0 подразумевает процессы сохранения контекста перед выполнением обработки прерывания и восстановление контекста после обработки (рисунок 7).

____На рисунке 7а представлен процесс обработки одиночного прерывания.

____Если в процессе обработки прерывания возникло прерывание с более высоким приоритетом, то система автоматически выполняет ещё одну пару операций сохранения/восстановления контекста, как показано на рисунке 7б. В данном случае вначале возникло прерывание IRQ1. Система сохранила контекст исходного приложения и перешла к обработчику IRQ1. Однако в процессе обработки IRQ1 произошло прерывание IRQ2 с более высоким приоритетом. Система сохраняет контекст обработчика IRQ1, выполняет обработку IRQ2, восстанавливает контекст обработчика IRQ1, заканчивает обработку IRQ1 и восстанавливает контекст исходного приложения.

Если в процессе обработки прерывания возникло прерывание с меньшим приоритетом, то система продолжает выполнять обработку исходного обработчика прерывания, как показано на рисунке 7в. После окончания обработки прерывания IRQ1 система не производит восстановления контекста исходного приложения, а переходит к обработке прерывания с более низким приоритетом IRQ2. Только после выполнения обработки IRQ2 восстанавливается контекст исходного приложения.

____Стоит отметить, что если в процессе сохранения контекста после возникновения первого прерывания возникло второе прерывание с более высоким приоритетом, то система автоматически переключается на обработку второго прерывания, как показано на рисунке 7г.

____Запрет или разрешение прерываний определяет, будет ли выполнено то или иное прерывание процессором или нет. Однако флаги NVIC выставляются вне зависимости от того, разрешено прерывание или нет.

____В микроконтроллерах STM32G0x1 используется семиканальный контроллер прямого доступа к памяти DMA (в некоторых линейках пятиканальный, например, в STM32G031xx и STM32G041xx). DMA обеспечивает быстрый обмен данными между периферийными блоками и памятью без участия процессора. Таким образом, процессор освобождается для выполнения других задач.

____На рисунке 8 представлена структурная схема контроллера DMA. DMA взаимодействует с шиной AHB с помощью двух 32-битных интерфейсов. Один из интерфейсов AHB является ведущим (мастер). С его помощью производится обмен данными между памятью и периферией. Второй интерфейс AHB является ведомым и предназначен для работы с регистрами управления и состояния DMA.

____DMA поддерживает четыре режима обмена данными:

____Каждый канал DMA может иметь индивидуальные настройки следующих параметров:

____В контроллере DMA применяется двухуровневая система приоритетов на тот случай, если доступ к DMA потребуется нескольким процессам одновременно. По умолчанию используется аппаратный приоритет, который совпадает с номером канала: канал dma_req[0] имеет приоритет 0 (см. рисунок 8 ), канал dma_req[1] имеет приоритет 1 и т. д. Чем меньше номер приоритета, тем выше приоритет. Например, если одновременно возникли запросы на DMA со стороны канала dma_req[0] и dma_req[1], то сначала будет выполнен запрос от dma_req[0].

____Кроме того, для каждого канала может быть назначен программный приоритет четырёх уровней: very high, high, medium, и low. Сравнение приоритетов выполняется перед каждой транзакцией данных. При равенстве программных приоритетов арбитраж будет выполнен на основе аппаратных приоритетов.

____Каждый канал DMA имеет независимые флаги, сообщающие о завершении передачи (TCIFx), о передаче половины данных (HTIFx ), об обнаружении ошибок (TEIFx), о возникновении прерываний (GIFx).

____До сих пор, говоря о каналах DMA, мы не касались конкретных периферийных блоков. Дело в том, что в отличие, например, от семейства STM32F0, в микроконтроллерах STM32G0 запросы прерываний от периферии поступают к DMA-контроллеру не напрямую, а через специальный мультиплексор DMAMUX. Благодаря DMAMUX, запросы к DMA могут направлять до 64 передатчиков/приёмников. Подробнее о DMAMUX рассказывается в следующем разделе.

____DMAMUX – специализированный мультиплексор в составе STM32G0, который позволяет практически произвольно перенаправлять запросы прямого доступа к памяти от периферийных блоков на каналы DMA-контроллера.

____Блок схема DMAMUX представлена на рисунке 9. Информация по количеству входов и выходов DMAMUX представлена в таблице 4. Основными функциональными блоками в составе DMAMUX являются семь мультиплексоров запросов (Request multiplexor) и один генератор запросов (Request generator). Каждый мультиплексор запросов выполняет коммутацию запросов DMA на конкретный канал DMA-контроллера. Генератор запросов принимает входные сигналы-триггеры, которые также могут использоваться в качестве источников запросов DMA (подробнее об этом рассказывается ниже).

Таблица 4. Количество входов и выходов DMAMUX в микроконтроллерах STM32G0x1.

____Каждый мультиплексор запросов имеет по 64 входа. Из них 57 приходится на периферийные блоки (dmamux_req_inx), четыре линии подключены к выходам генератора запросов (dmamux_req_genx), остальные находятся в резерве. Назначение входов представлено в таблице 5. Из таблицы видно, что запрос прерывания может сформировать практически любое периферийное устройство. Коммутация каналов на выход мультиплексора выполняется с помощью поля DMAREQ_ID в регистрах DMAMUX_CxCR.

Таблица 5. Назначение каналов мультиплексора запросов в микроконтроллерах STM32G0x1.

____Выходы мультиплексоров подаются на соответствующие входы DMA-контроллера (dmamux_req_outx) (рисунок 8 ). Существует два режима работы мультиплексора: простой и с синхронизацией. В простом режиме запросы DMA обрабатываются традиционным способом без каких-либо дополнительных условий. При этом стоит отметить, что у всех мультиплексоров есть встроенный вычитающий счётчик, содержимое которого уменьшается на 1 при обработке каждого запроса DMA (рисунок 10). После перехода через ноль счетчик перезагружается значением, задаваемым в поле NBREQ соответствующего регистра DMAMUX_CxCR. Кроме того, при переходе счётчика через 0 формируется сигнал dmamux_evtx. Такие сигналы могут использоваться в качестве триггерных сигналов для генератора запросов.

____Формирование запросов DMA на выходе мультиплексоров может синхронизироваться со входными сигналами dmamux_syncx. В качестве сигналов синхронизации используются: EXTI LINE0… EXTI LINE15, выходы dmamux_evt0…dmamux_evt3, LPTIM1_OUT, TIM14_OC. Выбор источника синхронизации выполняется с помощью поля SYNC_ID в регистрах DMAMUX_CxCR. На рисунке 11 представлены диаграммы работы мультиплексора в синхронном режиме. До прихода сигнала синхронизации запрос DMA не обрабатывается. После возникновения сигнала синхронизации обработка запросов DMA выбранного источника разрешается, при этом активизируется встроенный счётчик. При обработке каждого запроса содержимое счётчика уменьшается на 1. При переходе счётчика через ноль канал вновь блокируется и формируется сигнал события dmamux_evtx. В дальнейшем обработка запроса DMA возможна только после прихода следующего сигнала синхронизации. Полярность сигналов синхронизации выбирается пользователем с помощью поля SPOL из регистра DMAMUX_CxCR.

____Стоит отдельно коснуться генератора запросов. Этот блок принимает 23 триггерных сигнала и имеет четыре выхода. Коммутация входных каналов на выход генератора осуществляется с помощью полей SIG_ID соответствующих регистров конфигурации DMAMUX_RGxCR. Стоит отметить, что на вход генератора поступают те же сигналы, что используются для синхронизации: EXTI LINE0… EXTI LINE15, выходы dmamux_evt0…dmamux_evt3, LPTIM1_OUT, TIM14_OC. С другой стороны, выходные сигналы генератора могут выступать в качестве сигналов запроса DMA. Таким образом, оказывается возможным создание автоматических цепочек запросов DMA.

____Мультиплексор DMAMUX может генерировать два типа прерываний и выставлять соответствующие флаги:

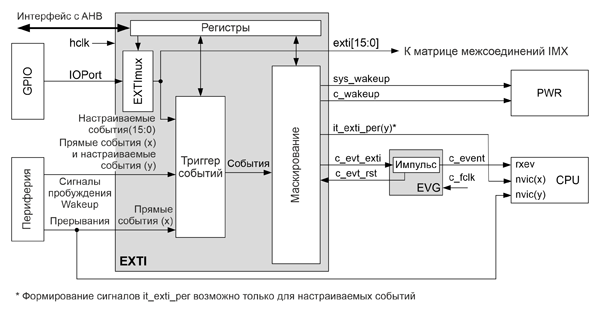

____Контроллер EXTI используется для пробуждения системы и процессорного ядра, формирования сигналов событий, а также для генерации прерываний.

____Прежде чем говорить о EXTI, необходимо коснуться различий между прерываниями и событиями. Процессорное ядро Cortex M0+ поддерживает два способа перехода в спящий режим: с помощью инструкции WFE (Wait For Event) и с помощью инструкции WFI (Wait For Interrupt).

____После выполнения инструкции WFE процессор засыпает, и для его пробуждения необходимо формирование сигнала на специальном входе rxev. Такие сигналы пробуждения называются событиями, а их источниками могут быть порты ввода-вывода и периферийные блоки. Далее процессор просыпается и продолжает выполнять код с того места, на котором остановился. Другими словами, если перед выполнением инструкции WFE выполнялась команда N, то после пробуждения будет выполнена следующая за ней команда N+1.

____При работе с прерываниями дело обстоит несколько иначе. После выполнения команды WFI процессор также переходит в спящий режим, но для его пробуждения требуется возникновение прерывания. Прерываниями называются специализированные сигналы, которые формируются в системной и общей периферии и поступают на контроль NVIC. После пробуждения процессор выполняет не следующую команду, а соответствующий обработчик прерывания. Благодаря контроллеру EXTI в микроконтроллерах STM32G0 сигналы прерываний могут выступать также и в роли событий.

____Блок схема контроллера EXTI представлена на рисунке 12. Контроллер принимает сигналы от портов ввода-вывода GPIO и от периферии. Все входные сигналы условно называются событиями и бывают двух типов: настраиваемые и прямые.

____Прямые события – это сигналы прерываний, сформированные в периферийных блоках, например, прерывания от USART. Они уже аппаратно подключены к контроллеру NVIC (входы nvic(y)). Контроллер EXTI позволяет использовать эти же сигналы в качестве событий для пробуждения системы и ядра.

____Настраиваемые события – это сигналы от периферии, которые не имеют собственных прерываний и флагов: сигналы от GPIO, от схемы контроля напряжения питания PVD и от аналоговых компараторов COMP1 и COMP2. Контроллер EXTI позволяет использовать эти события для пробуждения системы и ядра, а также для генерации прерываний. На рисунке 12 прерывания от этих событий обозначены как it_exti_per. Полная расшифровка всех линий EXTI приведена в таблице 7.

Таблица 6. Назначение входов и выходов контроллера EXTI.

Таблица 7. Источники сигналов для линий EXTI.

____Подключение линий GPIO выполняется с помощью шестнадцати мультиплексоров (рисунок 13). Таким образом, линии EXTI[15:0] являются производными именно от линий GPIO.

____Рассмотрим подробнее подключение и использование выходов контроллера EXTI.

____Выходы EXTI[15:0]. Эти выходы поступают в матрицу межсоединений IMX и используются в качестве триггерных сигналов для АЦП и ЦАП (см. раздел, посвященный IMX). EXTI[15:0] также поступают на входы системного контроллера SYSCFG, а далее через логические схемы на контроллер прерываний NVIC (см. раздел, посвященный NVIC).

____Выходы sys_wakeup и c_wakeup необходимы для пробуждения из различных спящих режимов. Сигнал sys_wakeup активизирует источники тактирования (сигналы ck_sys и hclk), а сигнал c_wakeup пробуждает процессорное ядро. Для формирования этих сигналов могут использоваться как прямые, так и настраиваемые события (при этом у пользователя есть возможность выбор фронта/среза). Все разрешенные события объединены по схеме ИЛИ. Стоит отметить, что маскирование событий-источников выполняется либо с помощью регистров EXTI_IMR, либо с помощью регистров EXTI_EMR (в данной схеме эти регистры объединяются по схеме ИЛИ).

____Как уже говорилось выше, выходы it_exti_per подключаются к NVIC и необходимы для генерации прерываний от GPIO и периферийных блоков, не имеющих собственных прерываний. Для маскирования этих прерываний используется регистр EXTI_IMR1.

____Сигнал c_event подключён ко входу процессора rxev и используется для пробуждения ядра после выполнения команды WFE. Источниками этого сигнала являются прямые и настраиваемые события, объединение с помощью схемы ИЛИ. Маскирование событий-источников выполняется с помощью регистров EXTI_EMR.

____Стоит еще раз подчеркнуть, что для прерываний и событий есть собственные регистры маскирования EXTI_EMRx и EXTI_IMRx. Причём если для настраиваемых событий эти регистры имеют понятное назначение, то для прямых событий необходимо дать некоторые пояснения. Дело в том, что линии прямых событий уже подключены к NVIC и имеют собственные регистры маскирования в составе периферийных блоков. Для них функционал регистров EXTI_IMRx ограничен маскированием при формировании сигналов sys_wakeup и c_wakeup.

____Модуль DBG обеспечивает пользователям широкие возможности отладки при работе с микроконтроллерами STM32G0: программирование flash-памяти, поддержка точек останова, чтение содержимого регистров и памяти. Инфраструктура DBG использует стандарт ARM CoreSight, который поддерживается большинством производителей отладочных инструментов.

____DBG включает в себя функционал, заложенный на уровне ядра Cortex-M0+, и дополнительный функционал на уровне SoC. Блок схема DBG представлена на рисунке 14.

____Подключение внешних отладчиков производится с помощью специального порта Debug Access Port (DAP) и двухпроводного интерфейса Serial Wire Debug (SWD). Использование для отладки всего двух линий (SWDIO – вывод PA13, SWCLK – вывод PA14) является большим плюсом для маловыводных микроконтроллеров STM32G0. Кроме того, при необходимости эти выводы могут выступать и в качестве выводов общего назначения. Сразу после сброса порты PA13 и PA14 по умолчанию настраиваются для работы в качестве линий SWD, однако пользователь может вручную перенастроить их для своих собственных нужд.

____Все отладочные блоки, входящие в состав процессора, подключены к ядру и к DAP посредством отдельной шины (Private Peripheral Bus). При этом отладчик имеет доступ к регистрам отладочных блоков даже когда процессор выполняет программу. Кроме функциональных блоков модуль DBG имеет и ROM-память, которая содержит различную служебную информацию.

____Основными отладочными блоками в составе DBG являются:

Продолжение в следующем посте...

.

Микроконтроллеры STM32G0: Архитектура и системная периферия.

Вячеслав Гавриков (г. Смоленск)

____Серия публикаций основана на материалах цикла STM32G0 Online Training от компании STMicroelectronics. Первая статья посвящена описанию особенностей процессорного ядра, архитектуры и системной периферии микроконтроллеров STM32G0.

Процессорное ядро ARM Cortex-M0+.

____Микроконтроллеры STM32G0 построены на базе мало потребляющего и высокопроизводительного процессорного ядра ARM Cortex-M0+ (рисунок 1).

____ARM Cortex-M0+ является частью семейства 32-битных процессорных RISC-ядер Cortex-M (рисунок 2). В нём используется архитектура ARMv6-M и двухуровневый конвейер. Системная шина AHB-Lite применяется для взаимодействия с памятью и периферией. Кроме того, для прямого взаимодействия с портами ввода-вывода предназначен специальный порт Fast I/O. В составе ядра также присутствует модуль защиты памяти MPU (Memory protection unit), блоки отладки (DWP и BPU), контроллер прерываний и отладочный интерфейс SWD. Набор инструкций ARM Cortex-M0+ практически полностью состоит из 16-битных команд, за исключением некоторых команд управления. Это позволяет создавать очень компактный программный код.

____Одним из важнейших изменений Cortex-M0+ по сравнению с Cortex-M0 стало уменьшение числа ступеней конвейера. В Cortex-M0+ используется двухуровневый конвейер, который позволяет выполнять обработку команд в два этапа. На первом этапе производится выборка и предварительное декодирование, а на втором декодирование и выполнение. Как уже было сказано, большинство команд ARMv6-M имеет длину 16 бит. Только 6 команд управления имеют длину 32 бита, при том что используются они относительно редко. В результате в идеальном случае за один системный такт может выбираться сразу две 16-битные инструкции.

____На рисунке 3 показан простой пример обработки двух 16-битных команд. На первом такте происходит выборка команд и предварительное декодирование первой команды. На втором такте выборка новых инструкций не производится, вместо этого декодируется и выполняется первая команда, а также предварительно декодируется вторая команда, выбранная на первом такте. На третьем такте декодируется и выполняется вторая команда, а также происходит выборка следующих двух 16-битных команд. Как видно из рисунка 3, на втором такте команды не выбираются, а значит, ничто не мешает выполнять выборку данных.

Рисунок 3, в большом разрешении: Скачать

____К сожалению, при выполнении команд с переходами происходит потеря содержимого конвейера. На рисунке 4 показан пример выполнения команды условного перехода. На первом такте, как обычно, выполняется выборка двух команд: простой («Инструкция 0») и команды перехода («Переход к метке»). На втором такте выполняется инструкция 0. На третьем такте происходит выборка двух новых команд («Инструкция 1» и «Инструкция 2»). Однако в результате выполнения команды условного перехода процессору требуется обработать команду, расположенную по заданному адресу метки («Инструкция N»). В результате содержимое конвейера теряется, так как уже выбранные команды «Инструкция 1» и «Инструкция 2» оказываются неактуальными.

Рисунок 4, в большом разрешении: Скачать

____Спецификация Cortex-M0+ не предусматривает кэш-памяти или встроенного ОЗУ. Однако в микроконтроллерах STM32G0, в отличие от STM32F0, кэш-память добавлена на уровне SoC.

____Шина AHB-Lite подключена к матрице шин (bus matrix) которая обеспечивает взаимодействие процессора с периферией и памятью. Дополнительный порт Single-cycle I/O Port позволяет процессору выполнять доступ к данным за один такт. Производитель микроконтроллеров может произвольно определять диапазон адресов, с которым будет работать этот порт. В микроконтроллерах STM32G0 от STMicroelectronics этот диапазон выделен для регистров GPIO, что позволяет работать с портами ввода-вывода на частоте процессора. В результате переключение выходов занимает всего два такта.

____В составе процессорного ядра Cortex-M0+ есть модуль защиты памяти MPU (Memory protection unit), который поддерживает до восьми областей памяти с независимыми настройками защиты:

- Разрешение доступа (access permission): разрешён или запрещён для записи/чтения в привилегированном/непривилегированном режиме;

- Разрешение выполнения (access permission): исполняемая область или область, запрещённая для исполнения.

____При создании ядра Cortex-M0+ была успешно решена задача по уменьшению уровня потребления. Микроконтроллеры, построенные на базе Cortex-M0+, становятся оптимальным выбором для малопотребляющих устройств с батарейным питанием.

Interconnect Matrix (IMX): матрица межсоединений периферийных блоков.

____Матрица межсоединений периферийных блоков IMX (Interconnect Matrix) позволяет периферийным блокам взаимодействовать без участия процессора. Наличие тех или иных связей зависит от линейки контроллеров STM32G0. По этой причине здесь и далее параметры семейства STM32G0 будут рассматриваться на примере наиболее продвинутой линейки – STM32G0x1. Например, в таблице 1 представлены возможные варианты взаимодействия периферии согласно RM0444. Reference manual. STM32G0x1 advanced Arm-based 32-bit MCUs. (Rev.2 2019). Как мы видим, одни и те же периферийные блоки могут выступать и в качестве источников, и в качестве приёмников сигналов управления.

Таблица 1. Возможности взаимодействия периферии в STM32G0x1.

____Рассмотрим несколько конкретных примеров взаимодействия периферийных блоков:

- Синхронизация и каскадирование таймеров;

- Запуск АЦП по сигналам с таймеров или по событиям EXTI;

- Формирование триггерных сигналов для таймеров по сигналам от цифрового компаратора (ADC watchdog);

- Запуск ЦАП по событиям EXTI;

- Калибровка встроенных генераторов LSI и HSI с помощью таймеров и встроенных генераторов LSE и HSE;

- Запуск таймеров LPTIM0 и LPTIM1 по сигналам от RTC, TAMPER или аналоговых компараторов;

- Формирование слепых окон для компараторов с помощью таймеров;

- Мониторинг датчика температуры, а также внутренних напряжений VBAT и VREFINT с помощью АЦП;

- Формирование триггерных сигналов для таймеров по сигналам от компараторов;

- Формирование триггерных сигналов для таймеров при возникновении системных ошибок;

- Модуляция инфракрасного интерфейса с помощью двух таймеров;

- Формирование триггерных сигналов для DMA по сигналам от таймеров.

____Связи между периферийными блоками остаются активными даже в режимах пониженного потребления Run, Sleep и Low-power sleep. Кроме того, некоторые блоки могут взаимодействовать также и в режимах Stop 0 и Stop 1. В таблице 2 представлена информация по работе IMX в спящих режимах.

Таблица 2. Возможности использования матрицы межсоединений в режимах пониженного потребления.

____Таким образом, прямые связи между периферийными блоками дают целый ряд преимуществ:

- Максимальная временная детерминированность операций. Вместо программного кода задачи решаются на аппаратном уровне с чётко определенными временными задержками.

- Уменьшение потребления. Вместо выполнения множества операций чтения/записи с участием процессора, матрица межсоединений позволяет блокам взаимодействовать напрямую, затрачивая минимум энергии.

- Уменьшение числа задействованных портов ввода-вывода. Наличие внутренних связей позволяет в некоторых случаях обходиться без внешних подключений и без привлечения портов ввода-вывода.

- Расширение функционала при работе в режимах пониженного потребления.

System Configuration Controller: системный контроллер.

____Системный контроллер SYSCFG в STM32G0 выполняет целый ряд задач:

- Разрешает/запрещает высокоскоростной режим I2C и повышенную нагрузочную способность выводов I2C.

- Настраивает USPD-интерфейс.

- Разрешает/запрещает работу повышающего преобразователя.

- Настраивает работу модуля IRTIM.

- Переназначает порты PA11 и PA12 на выводы, занимаемые портами PA9 и PA10 соответственно.

- Определяет расположение памяти по адресу 0x0000 0000.

- Разрешает/запрещает некоторые функции безопасности.

____Рассмотрим эти задачи подробнее.

____В микроконтроллерах STM32G0 присутствуют встроенные I2C-контроллеры, которые поддерживают три режима скорости передачи: режим Standard-mode с максимальной скоростью обмена данными до 100 Кбит/с, режим Fast-mode с максимальной скоростью 400 Кбит/с, режим Fast-mode Plus со скоростью обмена до 1 Мбит/с. Режим Fast-mode Plus требует повышенной нагрузочной способности от портов микроконтроллера. Активизацию функции повышенной нагрузочной способности осуществляет SYSCFG. Для индивидуальной активизации повышенной нагрузочной способности отдельных выводов используются биты I2C_PA9…10_FMP и I2C_PB6…9_FMP регистра SYSCFG_CFGR1. Для активизации повышенной нагрузочной способности всех выводов, относящихся к I2C, могут использоваться биты I2C1_FMP и I2C2_FMP регистра SYSCFG_CFGR1.

____SYSCFG также отвечает за начальную настройку подтягивающих резисторов на выводах CC1 и CC2, которые используются контроллерами USB Power Delivery. Для управления этой функцией предназначены биты UCPD1_STROBE и UCPD2_STROBE из регистра SYSCFG_CFGR1.

____При работе аналоговых входов STM32G0 при низком напряжении питания (VDD < 2,4 В) рекомендуется использовать специальный повышающий преобразователь. Для его активации предназначен бит BOOSTEN из регистра SYSCFG_CFGR1.

____Инфракрасный интерфейс IRTIM требует модуляции, которая может выполняться либо таймером TIM16, либо передатчиком USART1 или USART6. Выбор источника модуляции производится с помощью бита IR_MOD из регистра SYSCFG_CFGR1. Кроме того, бит IR_POL из того же регистра SYSCFG_CFGR1 определяет инверсию выходного сигнала IR_OUT (0 = не инвертируется, 1 = инвертируется).

____Выводы PA11 и PA12 доступны не во всех корпусных исполнениях. В таких случаях возможна их переадресация на выводы PA9 и PA10 соответственно. Для этого предназначен бит PA11_PA12_RMP из регистра SYSCFG_CFGR1.

____Бит MEM_MODE регистра SYSCFG_CFGR1 определяет выбор памяти доступной по адресу 0x0000 0000 (рисунок 5):

- x0: основная память Main Flash;

- 01: Системная память System Flash;

- 11: ОЗУ.

____Регистр SYSCFG_CFGR2 содержит биты статуса и управления, относящиеся к функциям безопасности и надёжности. В частности, биты PBx_CDEN и PAx_CDEN отвечают за подключение защитных диодов между соответствующими выводами микроконтроллера и VDD. Биты ECC_LOCK, PVD_LOCK, SRAM_PARITY_LOCK, LOCKUP_LOCK отвечают за разрешение подачи соответствующих сигналов ошибок на входы Break таймеров TIM1/15/16/17. В этом же регистре располагается флаг SRAM_PEF, выставляемый при возникновении ошибки чётности SRAM.

____Контроллер SYSCFG обеспечивает коммутацию источников прерываний на входы NVIC. При этом SYSCFG имеет 32 регистра SYSCFG_ITLINE0…SYSCFG_ITLINE31, содержащих информацию о статусе всех прерываний по каждому каналу NVIC. Так как к одному и тому же входу контроллера прерываний NVIC могут подключаться несколько источников прерываний, то эти регистры помогают быстро определить, какой из источников был активен. На рисунке 6 представлен пример линии INT5, к которой с помощью вентиля ИЛИ подключены EXTI2 и EXTI3. У SYSCFG для этой линий выделен регистр SYSCFG_ITLINE6, содержащий отдельные флаги по прерываниям EXTI2 и EXTI3. Если возникло прерывание INT5, программа обработчик должна вычитать регистр SYSCFG_ITLINE6 и определить реальный источник прерывания.

Nested Vectored Interrupt Control (NVIC): контроллер прерываний.

____Контроллер прерываний NVIC, реализованный в семействе STM32G0, имеет 32 входа прерываний, позволяет задавать четыре уровня приоритетов и динамически изменять их в процессе работы микроконтроллера, обеспечивает быструю реакцию на прерывания, даёт возможность изменять положение таблицы векторов прерываний.

____NVIC-контроллер процессорного ядра Cortex-M0+ имеет только 32 входа, однако благодаря системному контроллеру SYSCFG количество поддерживаемых источников прерываний оказывается значительно выше. Некоторые входы NVIC получают сигналы от нескольких источников прерываний, объединенных по схеме логического ИЛИ (см. рисунок 6). При этом, как уже отмечалось ранее, для того чтобы определить конкретный источник, вызвавший прерывание, удобно использовать регистры SYSCFG_ITLINE0…SYSCFG_ITLINE31.

____В процессе работы микроконтроллеров нередки случаи, когда несколько источников генерируют прерывания практически одновременно. Для того чтобы определить очерёдность обработки прерываний, используется система приоритетов. В таблице 3 представлены приоритеты источников прерываний для контроллеров STM32G0x1.

____Чем ниже уровень приоритета (первый столбец), тем выше приоритет прерывания. Как видно из таблицы 3, наивысший приоритет имеет сброс Reset (приоритет: -3), далее следуют немаскируемые прерывания NMI (приоритет: -2) и аппаратные ошибки HardFault (приоритет: -1). Приоритеты этих прерываний являются фиксированными и не могут быть изменены пользователем.

____По умолчанию для прерываний с уровнями приоритетов от 3 до 38 используется аппаратный приоритет, указанный в первом столбце таблицы 3. Однако для этих прерываний есть возможность назначения дополнительного программируемого приоритета от 0 до 3. Например, согласно таблице 3 уровень аппаратного приоритета WWDG равен 7, а уровень приоритета PVD равен 8. То есть при одновременной генерации прерываний сначала будет обработано прерывание от WWDG, и лишь потом прерывание от PVD. Однако пользователь может определить программный приоритет для WWDG равным 1, а для PVD равным 0. В таком случае при одновременной генерации прерываний сначала будет обработано прерывание от PVD, а потом прерывание от WWDG. Важно отметить, что программные приоритеты этой группы прерываний могут изменяться динамически в ходе выполнения программы.

Таблица 3. Приоритеты источников прерываний для контроллеров STM32G0x1.

____Обработка прерываний в STM32G0 подразумевает процессы сохранения контекста перед выполнением обработки прерывания и восстановление контекста после обработки (рисунок 7).

____На рисунке 7а представлен процесс обработки одиночного прерывания.

____Если в процессе обработки прерывания возникло прерывание с более высоким приоритетом, то система автоматически выполняет ещё одну пару операций сохранения/восстановления контекста, как показано на рисунке 7б. В данном случае вначале возникло прерывание IRQ1. Система сохранила контекст исходного приложения и перешла к обработчику IRQ1. Однако в процессе обработки IRQ1 произошло прерывание IRQ2 с более высоким приоритетом. Система сохраняет контекст обработчика IRQ1, выполняет обработку IRQ2, восстанавливает контекст обработчика IRQ1, заканчивает обработку IRQ1 и восстанавливает контекст исходного приложения.

Если в процессе обработки прерывания возникло прерывание с меньшим приоритетом, то система продолжает выполнять обработку исходного обработчика прерывания, как показано на рисунке 7в. После окончания обработки прерывания IRQ1 система не производит восстановления контекста исходного приложения, а переходит к обработке прерывания с более низким приоритетом IRQ2. Только после выполнения обработки IRQ2 восстанавливается контекст исходного приложения.

____Стоит отметить, что если в процессе сохранения контекста после возникновения первого прерывания возникло второе прерывание с более высоким приоритетом, то система автоматически переключается на обработку второго прерывания, как показано на рисунке 7г.

____Запрет или разрешение прерываний определяет, будет ли выполнено то или иное прерывание процессором или нет. Однако флаги NVIC выставляются вне зависимости от того, разрешено прерывание или нет.

Direct Memory Access Controller (DMA): контроллер прямого доступа к памяти.

____В микроконтроллерах STM32G0x1 используется семиканальный контроллер прямого доступа к памяти DMA (в некоторых линейках пятиканальный, например, в STM32G031xx и STM32G041xx). DMA обеспечивает быстрый обмен данными между периферийными блоками и памятью без участия процессора. Таким образом, процессор освобождается для выполнения других задач.

____На рисунке 8 представлена структурная схема контроллера DMA. DMA взаимодействует с шиной AHB с помощью двух 32-битных интерфейсов. Один из интерфейсов AHB является ведущим (мастер). С его помощью производится обмен данными между памятью и периферией. Второй интерфейс AHB является ведомым и предназначен для работы с регистрами управления и состояния DMA.

____DMA поддерживает четыре режима обмена данными:

- Из периферии в память (Peripheral-to-memory).

- Из памяти в периферию (memory-to-peripheral).

- Из памяти в память (memory-to-memory).

- Из периферии в периферию (peripheral-to-peripheral).

____Каждый канал DMA может иметь индивидуальные настройки следующих параметров:

- Формат данных (8/16/32 бита). DMA не упаковывает или распаковывает данные, а пересылает их «как есть», поэтому необходимо учитывать возможные проблемы с выравниванием, если формат данных источника не совпадает с форматом приёмника.

- Объем передачи от 1 до 65635 циклов пересылки данных.

- Адрес источника данных.

- Адрес приёмника данных.

- Тип инкремента адреса приёмника (адрес не изменяется или увеличивается с заданным шагом).

- Тип инкремента адреса передатчика (адрес не изменяется или увеличивается с заданным шагом).

- Использование кругового буфера для реализации непрерывного потока данных с автоматической перезагрузкой адресов передатчика и приёмника, а также с обновлением счётчика циклов передач. Данный режим удобен, например, при накоплении данных от АЦП.

- Приоритет.

____В контроллере DMA применяется двухуровневая система приоритетов на тот случай, если доступ к DMA потребуется нескольким процессам одновременно. По умолчанию используется аппаратный приоритет, который совпадает с номером канала: канал dma_req[0] имеет приоритет 0 (см. рисунок 8 ), канал dma_req[1] имеет приоритет 1 и т. д. Чем меньше номер приоритета, тем выше приоритет. Например, если одновременно возникли запросы на DMA со стороны канала dma_req[0] и dma_req[1], то сначала будет выполнен запрос от dma_req[0].

____Кроме того, для каждого канала может быть назначен программный приоритет четырёх уровней: very high, high, medium, и low. Сравнение приоритетов выполняется перед каждой транзакцией данных. При равенстве программных приоритетов арбитраж будет выполнен на основе аппаратных приоритетов.

____Каждый канал DMA имеет независимые флаги, сообщающие о завершении передачи (TCIFx), о передаче половины данных (HTIFx ), об обнаружении ошибок (TEIFx), о возникновении прерываний (GIFx).

____До сих пор, говоря о каналах DMA, мы не касались конкретных периферийных блоков. Дело в том, что в отличие, например, от семейства STM32F0, в микроконтроллерах STM32G0 запросы прерываний от периферии поступают к DMA-контроллеру не напрямую, а через специальный мультиплексор DMAMUX. Благодаря DMAMUX, запросы к DMA могут направлять до 64 передатчиков/приёмников. Подробнее о DMAMUX рассказывается в следующем разделе.

Direct Memory Access Multiplexer (DMAMUX): мультиплексор запросов DMA.

____DMAMUX – специализированный мультиплексор в составе STM32G0, который позволяет практически произвольно перенаправлять запросы прямого доступа к памяти от периферийных блоков на каналы DMA-контроллера.

____Блок схема DMAMUX представлена на рисунке 9. Информация по количеству входов и выходов DMAMUX представлена в таблице 4. Основными функциональными блоками в составе DMAMUX являются семь мультиплексоров запросов (Request multiplexor) и один генератор запросов (Request generator). Каждый мультиплексор запросов выполняет коммутацию запросов DMA на конкретный канал DMA-контроллера. Генератор запросов принимает входные сигналы-триггеры, которые также могут использоваться в качестве источников запросов DMA (подробнее об этом рассказывается ниже).

Таблица 4. Количество входов и выходов DMAMUX в микроконтроллерах STM32G0x1.

____Каждый мультиплексор запросов имеет по 64 входа. Из них 57 приходится на периферийные блоки (dmamux_req_inx), четыре линии подключены к выходам генератора запросов (dmamux_req_genx), остальные находятся в резерве. Назначение входов представлено в таблице 5. Из таблицы видно, что запрос прерывания может сформировать практически любое периферийное устройство. Коммутация каналов на выход мультиплексора выполняется с помощью поля DMAREQ_ID в регистрах DMAMUX_CxCR.

Таблица 5. Назначение каналов мультиплексора запросов в микроконтроллерах STM32G0x1.

____Выходы мультиплексоров подаются на соответствующие входы DMA-контроллера (dmamux_req_outx) (рисунок 8 ). Существует два режима работы мультиплексора: простой и с синхронизацией. В простом режиме запросы DMA обрабатываются традиционным способом без каких-либо дополнительных условий. При этом стоит отметить, что у всех мультиплексоров есть встроенный вычитающий счётчик, содержимое которого уменьшается на 1 при обработке каждого запроса DMA (рисунок 10). После перехода через ноль счетчик перезагружается значением, задаваемым в поле NBREQ соответствующего регистра DMAMUX_CxCR. Кроме того, при переходе счётчика через 0 формируется сигнал dmamux_evtx. Такие сигналы могут использоваться в качестве триггерных сигналов для генератора запросов.

____Формирование запросов DMA на выходе мультиплексоров может синхронизироваться со входными сигналами dmamux_syncx. В качестве сигналов синхронизации используются: EXTI LINE0… EXTI LINE15, выходы dmamux_evt0…dmamux_evt3, LPTIM1_OUT, TIM14_OC. Выбор источника синхронизации выполняется с помощью поля SYNC_ID в регистрах DMAMUX_CxCR. На рисунке 11 представлены диаграммы работы мультиплексора в синхронном режиме. До прихода сигнала синхронизации запрос DMA не обрабатывается. После возникновения сигнала синхронизации обработка запросов DMA выбранного источника разрешается, при этом активизируется встроенный счётчик. При обработке каждого запроса содержимое счётчика уменьшается на 1. При переходе счётчика через ноль канал вновь блокируется и формируется сигнал события dmamux_evtx. В дальнейшем обработка запроса DMA возможна только после прихода следующего сигнала синхронизации. Полярность сигналов синхронизации выбирается пользователем с помощью поля SPOL из регистра DMAMUX_CxCR.

____Стоит отдельно коснуться генератора запросов. Этот блок принимает 23 триггерных сигнала и имеет четыре выхода. Коммутация входных каналов на выход генератора осуществляется с помощью полей SIG_ID соответствующих регистров конфигурации DMAMUX_RGxCR. Стоит отметить, что на вход генератора поступают те же сигналы, что используются для синхронизации: EXTI LINE0… EXTI LINE15, выходы dmamux_evt0…dmamux_evt3, LPTIM1_OUT, TIM14_OC. С другой стороны, выходные сигналы генератора могут выступать в качестве сигналов запроса DMA. Таким образом, оказывается возможным создание автоматических цепочек запросов DMA.

____Мультиплексор DMAMUX может генерировать два типа прерываний и выставлять соответствующие флаги: