Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

HM-SHA256-v1. Разные наработки. Часть-1.

Страница 1 из 2 • Поделиться

Страница 1 из 2 • 1, 2

HM-SHA256-v1. Разные наработки. Часть-1.

HM-SHA256-v1. Разные наработки. Часть-1.

1

.

Различнные ссылки.

1. http://cryptography.gmu.edu/index.php

2. https://forum.cxem.net/index.php?/topic/158806-получение-хеша-sha256-и-вывод-по-uart-на-atmega16/

3. https://github.com/progranism/Open-Source-FPGA-Bitcoin-Miner.git

4. https://marsohod.org/projects/proekty-dlya-platy-marsokhod3/340-miner-bitcoin

5. https://habr.com/ru/post/318174/

6. https://habr.com/ru/company/selectel/blog/530262/

7. ...

Данную тему можете не читать, она для разработки устройства, просто так удобно и наглядно, хранить мне данные...

.

____Алгоритм использует следующие битовые операции:

ǁ — конкатенация,

+ — сложение,

and — побитовое «И»,

xor — исключающее «ИЛИ»,

shr (shift right) — логический сдвиг вправо,

rotr (rotate right) — циклический сдвиг вправо.

Пояснения:

Все переменные беззнаковые, имеют размер 32 бита и при вычислениях суммируются по модулю 232

message — исходное двоичное сообщение

m — преобразованное сообщение

Инициализация переменных

(первые 32 бита дробных частей квадратных корней первых восьми простых чисел [от 2 до 19]):

h0 := 0x6A09E667

h1 := 0xBB67AE85

h2 := 0x3C6EF372

h3 := 0xA54FF53A

h4 := 0x510E527F

h5 := 0x9B05688C

h6 := 0x1F83D9AB

h7 := 0x5BE0CD19

Таблица констант

(первые 32 бита дробных частей кубических корней первых 64 простых чисел [от 2 до 311]):

k[0..63] :=

0x428A2F98, 0x71374491, 0xB5C0FBCF, 0xE9B5DBA5,

0x3956C25B, 0x59F111F1, 0x923F82A4, 0xAB1C5ED5,

0xD807AA98, 0x12835B01, 0x243185BE, 0x550C7DC3,

0x72BE5D74, 0x80DEB1FE, 0x9BDC06A7, 0xC19BF174,

0xE49B69C1, 0xEFBE4786, 0x0FC19DC6, 0x240CA1CC,

0x2DE92C6F, 0x4A7484AA, 0x5CB0A9DC, 0x76F988DA,

0x983E5152, 0xA831C66D, 0xB00327C8, 0xBF597FC7,

0xC6E00BF3, 0xD5A79147, 0x06CA6351, 0x14292967,

0x27B70A85, 0x2E1B2138, 0x4D2C6DFC, 0x53380D13,

0x650A7354, 0x766A0ABB, 0x81C2C92E, 0x92722C85,

0xA2BFE8A1, 0xA81A664B, 0xC24B8B70, 0xC76C51A3,

0xD192E819, 0xD6990624, 0xF40E3585, 0x106AA070,

0x19A4C116, 0x1E376C08, 0x2748774C, 0x34B0BCB5,

0x391C0CB3, 0x4ED8AA4A, 0x5B9CCA4F, 0x682E6FF3,

0x748F82EE, 0x78A5636F, 0x84C87814, 0x8CC70208,

0x90BEFFFA, 0xA4506CEB, 0xBEF9A3F7, 0xC67178F2

Предварительная обработка:

m := message ǁ [единичный бит]

m := m ǁ [k нулевых бит],

где k — наименьшее неотрицательное число, такое что

(L + 1 + K) mod 512 = 448, где L — число бит в сообщении (сравнима по модулю 512 c 448)

m := m ǁ Длина(message)

- длина исходного сообщения в битах в виде 64-битного числа с порядком байтов от старшего к младшему

Далее сообщение обрабатывается последовательными порциями по 512 бит:

разбить сообщение на куски по 512 бит

для каждого куска разбить кусок на 16 слов длиной 32 бита (с порядком байтов от старшего к младшему внутри слова): w[0..15]

Сгенерировать дополнительные 48 слов:

для i от 16 до 63

s0 := (w[i-15] rotr 7) xor (w[i-15] rotr 18) xor (w[i-15] shr 3)

s1 := (w[i-2] rotr 17) xor (w[i-2] rotr 19) xor (w[i-2] shr 10)

w[i] := w[i-16] + s0 + w[i-7] + s1

Инициализация вспомогательных переменных:

a := h0

b := h1

c := h2

d := h3

e := h4

f := h5

g := h6

h := h7

Основной цикл:

для i от 0 до 63

Σ0 := (a rotr 2) xor (a rotr 13) xor (a rotr 22)

Ma := (a and b) xor (a and c) xor (b and c)

t2 := Σ0 + Ma

Σ1 := (e rotr 6) xor (e rotr 11) xor (e rotr 25)

Ch := (e and f) xor ((not e) and g)

t1 := h + Σ1 + Ch + k[i] + w[i]

h := g

g := f

f := e

e := d + t1

d := c

c := b

b := a

a := t1 + t2

Добавить полученные значения к ранее вычисленному результату:

h0 := h0 + a

h1 := h1 + b

h2 := h2 + c

h3 := h3 + d

h4 := h4 + e

h5 := h5 + f

h6 := h6 + g

h7 := h7 + h

Получить итоговое значение хеша:

digest = hash = h0 ǁ h1 ǁ h2 ǁ h3 ǁ h4 ǁ h5 ǁ h6 ǁ h7

___________________________________________________________________________________________

Полезные ссылки, а может и не очень:

1. https://github.com/JerryWm/Stratum-proxy-SHA256

.

Различнные ссылки.

1. http://cryptography.gmu.edu/index.php

2. https://forum.cxem.net/index.php?/topic/158806-получение-хеша-sha256-и-вывод-по-uart-на-atmega16/

- Спойлер:

- UART

#include <avr/io.h>

#include <avr/delay.h>

void init_UART(void)

{

UBRRH = 0;

UBRRL = 12;

UCSRA=0b00000000;

UCSRB=0b00011100;

UCSRC=0b10000110;

}

void send_Uart(unsigned char c)// Отправка байта

{

while(!(UCSRA & (1 << UDRE))) // Устанавливается, когда регистр свободен

{}

UDR = c;

}

void send_Uart_str(unsigned char *s)// Отправка строки

{

while(*s != 0) send_Uart(*s++);

}

void main(void)

{

DDRD = 0b00010010; // RXD = 0, TXD = 1

init_UART(); // инициализация UART

_delay_ms(1000);

while(1){

if( UCSRA & (1 << UDRE ))

{

send_Uart_str("lalalalalalalalala");

PORTD |= ( 1 << 4 ); // Включаем диод PC0 = 1 = Vcc

_delay_ms(50); // задержка 50мс

// LED off

PORTD &=~ ( 1 << 4 ); // Выключаем диод PC0 = 0 = Vcc

_delay_ms(1000);

}

}

}

3. https://github.com/progranism/Open-Source-FPGA-Bitcoin-Miner.git

4. https://marsohod.org/projects/proekty-dlya-platy-marsokhod3/340-miner-bitcoin

5. https://habr.com/ru/post/318174/

6. https://habr.com/ru/company/selectel/blog/530262/

7. ...

____________________________________________________________________________

Данную тему можете не читать, она для разработки устройства, просто так удобно и наглядно, хранить мне данные...

.

Псевдокод.

____Алгоритм использует следующие битовые операции:

ǁ — конкатенация,

+ — сложение,

and — побитовое «И»,

xor — исключающее «ИЛИ»,

shr (shift right) — логический сдвиг вправо,

rotr (rotate right) — циклический сдвиг вправо.

Пояснения:

Все переменные беззнаковые, имеют размер 32 бита и при вычислениях суммируются по модулю 232

message — исходное двоичное сообщение

m — преобразованное сообщение

Инициализация переменных

(первые 32 бита дробных частей квадратных корней первых восьми простых чисел [от 2 до 19]):

h0 := 0x6A09E667

h1 := 0xBB67AE85

h2 := 0x3C6EF372

h3 := 0xA54FF53A

h4 := 0x510E527F

h5 := 0x9B05688C

h6 := 0x1F83D9AB

h7 := 0x5BE0CD19

Таблица констант

(первые 32 бита дробных частей кубических корней первых 64 простых чисел [от 2 до 311]):

k[0..63] :=

0x428A2F98, 0x71374491, 0xB5C0FBCF, 0xE9B5DBA5,

0x3956C25B, 0x59F111F1, 0x923F82A4, 0xAB1C5ED5,

0xD807AA98, 0x12835B01, 0x243185BE, 0x550C7DC3,

0x72BE5D74, 0x80DEB1FE, 0x9BDC06A7, 0xC19BF174,

0xE49B69C1, 0xEFBE4786, 0x0FC19DC6, 0x240CA1CC,

0x2DE92C6F, 0x4A7484AA, 0x5CB0A9DC, 0x76F988DA,

0x983E5152, 0xA831C66D, 0xB00327C8, 0xBF597FC7,

0xC6E00BF3, 0xD5A79147, 0x06CA6351, 0x14292967,

0x27B70A85, 0x2E1B2138, 0x4D2C6DFC, 0x53380D13,

0x650A7354, 0x766A0ABB, 0x81C2C92E, 0x92722C85,

0xA2BFE8A1, 0xA81A664B, 0xC24B8B70, 0xC76C51A3,

0xD192E819, 0xD6990624, 0xF40E3585, 0x106AA070,

0x19A4C116, 0x1E376C08, 0x2748774C, 0x34B0BCB5,

0x391C0CB3, 0x4ED8AA4A, 0x5B9CCA4F, 0x682E6FF3,

0x748F82EE, 0x78A5636F, 0x84C87814, 0x8CC70208,

0x90BEFFFA, 0xA4506CEB, 0xBEF9A3F7, 0xC67178F2

Предварительная обработка:

m := message ǁ [единичный бит]

m := m ǁ [k нулевых бит],

где k — наименьшее неотрицательное число, такое что

(L + 1 + K) mod 512 = 448, где L — число бит в сообщении (сравнима по модулю 512 c 448)

m := m ǁ Длина(message)

- длина исходного сообщения в битах в виде 64-битного числа с порядком байтов от старшего к младшему

Далее сообщение обрабатывается последовательными порциями по 512 бит:

разбить сообщение на куски по 512 бит

для каждого куска разбить кусок на 16 слов длиной 32 бита (с порядком байтов от старшего к младшему внутри слова): w[0..15]

Сгенерировать дополнительные 48 слов:

для i от 16 до 63

s0 := (w[i-15] rotr 7) xor (w[i-15] rotr 18) xor (w[i-15] shr 3)

s1 := (w[i-2] rotr 17) xor (w[i-2] rotr 19) xor (w[i-2] shr 10)

w[i] := w[i-16] + s0 + w[i-7] + s1

Инициализация вспомогательных переменных:

a := h0

b := h1

c := h2

d := h3

e := h4

f := h5

g := h6

h := h7

Основной цикл:

для i от 0 до 63

Σ0 := (a rotr 2) xor (a rotr 13) xor (a rotr 22)

Ma := (a and b) xor (a and c) xor (b and c)

t2 := Σ0 + Ma

Σ1 := (e rotr 6) xor (e rotr 11) xor (e rotr 25)

Ch := (e and f) xor ((not e) and g)

t1 := h + Σ1 + Ch + k[i] + w[i]

h := g

g := f

f := e

e := d + t1

d := c

c := b

b := a

a := t1 + t2

Добавить полученные значения к ранее вычисленному результату:

h0 := h0 + a

h1 := h1 + b

h2 := h2 + c

h3 := h3 + d

h4 := h4 + e

h5 := h5 + f

h6 := h6 + g

h7 := h7 + h

Получить итоговое значение хеша:

digest = hash = h0 ǁ h1 ǁ h2 ǁ h3 ǁ h4 ǁ h5 ǁ h6 ǁ h7

___________________________________________________________________________________________

Полезные ссылки, а может и не очень:

1. https://github.com/JerryWm/Stratum-proxy-SHA256

.

Последний раз редактировалось: Viktor2312 (Ср Мар 16 2022, 00:07), всего редактировалось 14 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

2

.

SHA-2 хеш алгоритм.

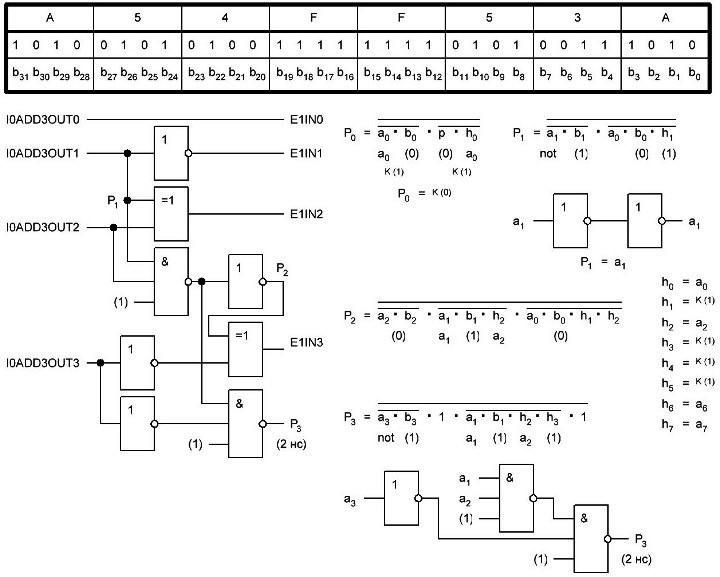

____В 1993 году NIST впервые опубликовал Стандарт Безопасного Хеша (SHA). В 1995 году этот алгоритм был пересмотрен с целью устранения некоторых начальных недостатков, а в 2001 году были предложены новые алгоритмы хеширования. Это новое семейство алгоритмов хеширования, известное как SHA-2, использует большие дайджест-сообщения, делая их более устойчивыми к возможным атакам и позволяя использовать их с большими блоками данных, вплоть до 2128 бит, например, в случае SHA512. Алгоритм хеширования SHA-2 одинаков для хэш-функций SHA256, SHA224, SHA384 и SHA512, различаясь только размером операндов, векторами инициализации и размером окончательного дайджест-сообщения.

____Далее описывается алгоритм SHA-2, применяемый к хеш-функции SHA256, после чего следует описание хеш-функции SHA512, которая отличается в основном размером операндов, используя 64-битные слова вместо 32-битных. Обратите внимание, что SHA224 и SHA384 вычисляются как SHA256 и SHA512, соответственно, с окончательным значением хеш-функции, усеченным до соответствующего размера, вектор инициализации также отличается.

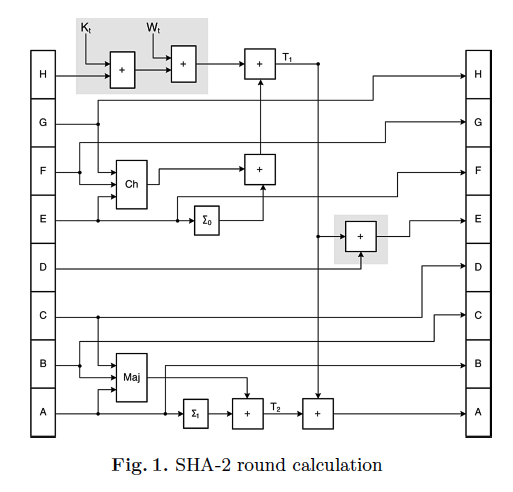

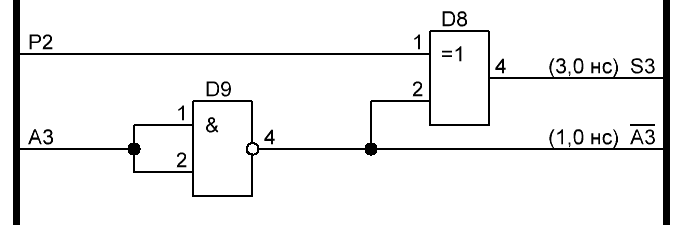

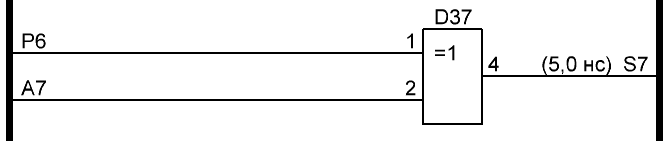

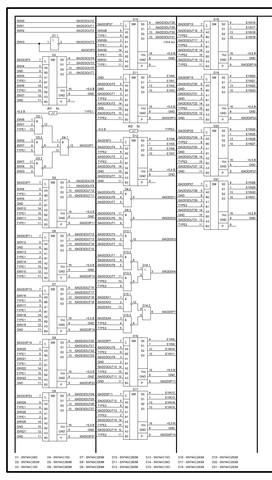

____Функция хеширования SHA256: Функция хеширования SHA256 создает окончательное дайджест-сообщение из 256 битов, которое зависит от входного сообщения и состоит из нескольких блоков по 512 бит в каждом. Этот входной блок расширяется и подается на 64 цикла функции SHA256 в словах по 32 бита каждый (обозначается Wt). В каждом цикле или цикле алгоритма SHA-2 введенные данные смешиваются с текущим состоянием. Это скремблирование данных выполняется с помощью сложений и логических операций, таких как побитовые логические операции и побитовые вращения. Вычислительная структура каждого раунда этого алгоритма изображена на рисунке 1. Несколько функций, представленных на этом рисунке, описаны в Приложении I. Значение Wt является 32-разрядным словом данных для раунда t, а значение Kt представляет 32-битная константа, которая также зависит от раунда.

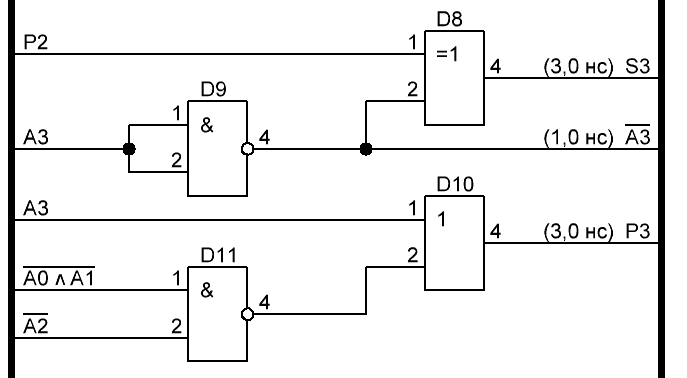

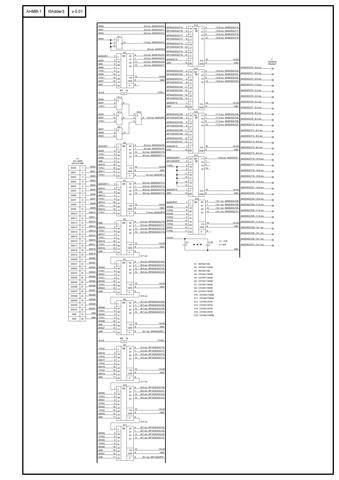

____32-битные значения переменных от A до H обновляются в каждом раунде, а новые значения используются в следующем раунде. Начальные значения этих переменных задаются 256-битным постоянным значением, указанным в [10], это значение устанавливается только для первого блока данных. В последовательных блоках данных используется промежуточное хеш-значение, вычисленное для предыдущего блока данных. Каждый блок 512 данных обрабатывается в течение 64 циклов, после чего значения переменных от A до H добавляются в предыдущее дайджест-сообщение для получения частичного Дайджест сообщения. Чтобы лучше проиллюстрировать этот алгоритм, представление псевдокода изображено на рисунке 2. Окончательное дайджест-сообщение (DM) для данного потока данных дается результатом последнего блока данных.

____В некоторых приложениях более высокого уровня, таких как эффективная реализация кода аутентификации хеш-сообщения с ключом (HMAC) [11] или когда сообщение фрагментировано, начальное значение хеш-функции (IV) может отличаться от константы, указанной в [10]. В этих случаях переменные от A до H инициализируются переменным вектором инициализации (IV).

____Хеш-функция SHA512: вычисление хеш-функции SHA512 идентично вычислению хеш-функции SHA256, отличающейся размером операндов, которые имеют 64 бита, а не 32 бита, как для SHA256, размера дайджест-сообщения, которое имеет удвоенный размер, составляющий 512 бит, и в функциях, описанных в Приложении I. В этом Приложении также описаны функции, используемые в расписании сообщений. Значения Wt и Kt имеют 64 бита, и каждый блок данных состоит из 16 64-битных слов, имеющих в общей сложности 1024 бита.

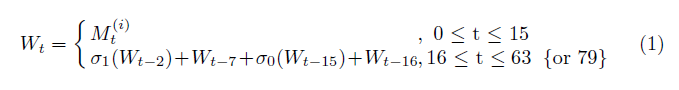

____Расписание сообщений: В алгоритме SHA-2 вычисления, описанные на рисунке 1, выполняются для 64 раундов для SHA256 (80 раундов для SHA512), в каждом раунде 32-битное слово (или 64 бита для SHA512), полученное из промежуточного слова. используется хэш-значение Однако каждый блок данных имеет только 16 32-битных слов для SHA256 или 16 64-битных слов для SHA512, что приводит к необходимости расширения исходного блока данных для получения оставшихся слов. Это расширение выполняется вычислением, описанным в (1), где M(i)t обозначает первые 16 слов i-го блока данных.

____Заполнение сообщения: чтобы гарантировать, что входное сообщение кратно 512 битам, как того требует хеш-функция SHA256, или 1024 для хеш-функции SHA512, необходимо дополнить исходное сообщение. Дополненное сообщение состоит из сообщения, с ничего не значащими данными, и присоединённым к нему оригинальным сообщением. Эта операция может быть эффективно реализована в программном обеспечении с минимальными затратами.

Proposed Design.

____В алгоритме SHA-2 операции, которые должны быть выполнены, просты, однако зависимость этого алгоритма от данных не допускает большого распараллеливания. Каждый раунд алгоритма может быть вычислен только после того, как были вычислены значения от A до H предыдущего раунда (см. Рисунок 2), что накладывает последовательность на вычисление. Следует отметить, что в каждом раунде вычисление требуется только для вычисления значений A и E, поскольку остальные значения получаются непосредственно из значений предыдущего раунда, как показано в псевдокоде на рис.2.

____Перепланирование операций: в нашем предложении мы определили часть вычисления данного раунда t, которая может быть вычислена заранее в предыдущем раунде t − 1. Только значения, которые не зависят от значений, вычисленных в предыдущем раунде, могут быть вычислены заранее. В отличие от метода перепланирования, предложенного в [12] для алгоритма SHA1, где взаимная зависимость данных является низкой, в алгоритме SHA-2 зависимость данных является более сложной, как показано на рисунке 1. Хотя переменные B, C, D , F, G и H получены непосредственно из значений раунда, не требующих каких-либо вычислений, значения A и E требуют вычислений и зависят от всех значений. Другими словами, значения A и E для раунда t не могут быть вычислены до тех пор, пока значения для тех же переменных не будут вычислены в предыдущем раунде, как показано в (2).

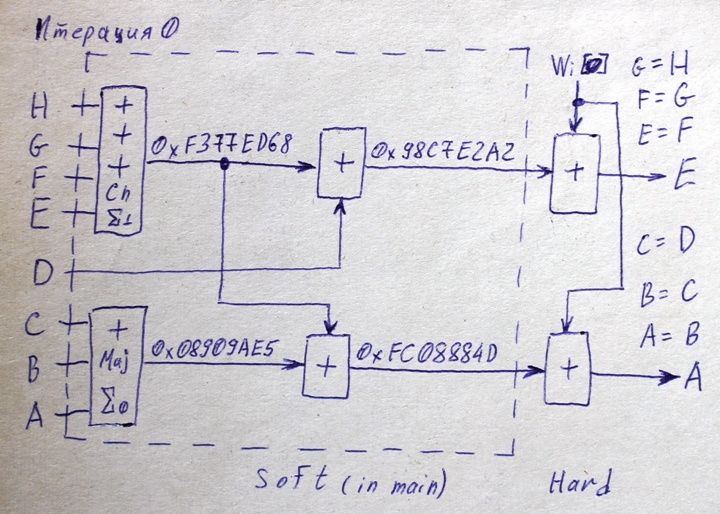

____Принимая во внимание, что значение Ht + 1 задается непосредственно через Gt, которое, в свою очередь, задается посредством Ft-1, предварительный расчет H, таким образом, может быть задан как Ht + 1 = Ft-1. Поскольку значения Kt и Wt можно предварительно рассчитать и просто использовать в каждом раунде, (2) можно переписать как:

где значение δt рассчитывается в предыдущем раунде. Значение δt + 1 может быть результатом полного сложения или векторов переноса и сохранения из сложения переноса. С этим вычислительным разделением вычисление алгоритма SHA-2 может быть разделено на две части, что позволяет переназначить вычисление δ на предыдущий тактовый цикл, изображенный серой областью на рисунке 3. Таким образом, критический путь результирующего оборудования реализация может быть уменьшена. Поскольку вычисление теперь разделено на этап конвейера, вычисление SHA-2 требует дополнительного тактового цикла для выполнения всех циклов. В случае хэш-функции SHA256 необходимо 65 тактов для расчета 64 раундов. Как указано в алгоритме SHA-2 и изображено на рисунке 2, после вычисления всех циклов внутренние переменные (от A до H) должны быть добавлены к предыдущему дайджест-сообщению.

Пометки:

1. # Майнер отправляет пулу nonce и хеш заданной сложности, пул подставляет этот nonce в заголовки блока и хеширует их, получил в результате тот же хеш - валидный, получил другой хеш - невалидный.

(если я как майнер состоящий в пуле, отсылаю пулу к примеру 100 nonce и соответствующих хешей, то пулл, будет пересчитывать все 100 хешей, что бы провалидировать? Тогда какой от меня смысл, если пул сам может считать эти хеши?)

# Майнер перебирает nonce, чтобы получить "красивый" хеш. Для этого нужно проделать МНОГО операций хеширования.

Пул проверяет, что присланные майнером nonce и хеш соответствуют друг другу. Это ОДНА операция хеширования.

(Как тогда майнинг пул проверит, что я реально работал и сколько работы я проделал, если я не нашел "красивый" хеш, хотя реально искал?)

# Например, сложность выставленная пулом равна 10 000, следовательно майнер будет находить соответствующий хеш в среднем за 10 000 итераций перебора nonce. Ключевое слово - в среднем. Сколько реально было итераций в конкретном случае - сугубо половые пробемы майнера и пулу на это положить, потому что в среднем будет 10 000, не смотря на то, что иной раз его можно найти с первой же итерации, а иногда не найти и за 20 000+ итераций. Как только майнер нашёл соответствующий хеш, он отправляет его и nonce пулу, а пул хеширует у себя и засчитывает майнеру 10 000 итераций. Проще говоря, пулу не нужно проверять сколько майнер сделал работы в каждом конкретном случае, потому что в среднем майнеру придётся перебирать столько, сколько требует заданная сложность, иначе он не найдёт требуемые хеши и отправлять будет нечего.

*задание содержит номер блока, ID задания, хэш предыдущего блока, минимальный и максимальный nonce для тебя

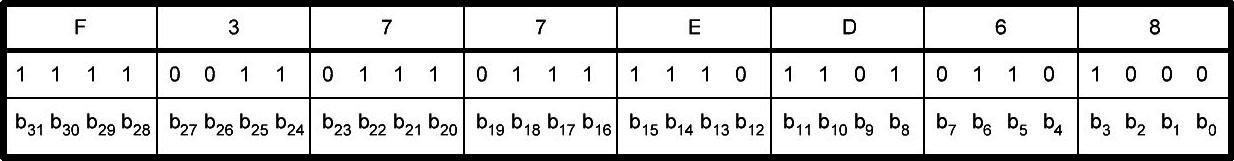

Начальные значения:

h0 := 0x6A09E667 (0110 1010 0000 1001 1110 0110 0110 0111)

h1 := 0xBB67AE85 (1011 1011 0110 0111 1010 1110 1000 0101)

h2 := 0x3C6EF372 (0011 0011 0110 1110 1111 0011 0111 0010)

h3 := 0xA54FF53A (1010 0101 0100 1111 1111 0101 0011 1010)

h4 := 0x510E527F (0101 0001 0000 1110 0101 0010 0111 1111)

h5 := 0x9B05688C (1001 1011 0000 0101 0110 1000 1000 1100)

h6 := 0x1F83D9AB (0001 1111 1000 0011 1101 1001 1010 1011)

h7 := 0x5BE0CD19 (0101 1011 1110 0000 1100 1101 0001 1001)

k0 := 0x428A2F98 (0100 0010 1000 1010 0010 1111 1001 1000)

k1 := 0x71374491 (0111 0001 0011 0111 0100 0100 1001 0001)

k2 := 0xB5C0FBCF (1011 0101 1100 0000 1111 1011 1100 1111)

k3 := 0xE9B5DBA5 (1110 1001 1011 0101 1101 1011 1010 0101)

k4 := 0x3956C25B (0011 1001 0101 0110 1100 0010 0101 1011)

k5 := 0x59F111F1 (0101 1001 1111 0001 0001 0001 1111 0001)

k6 := 0x923F82A4 (1001 0010 0011 1111 1000 0010 1010 0100)

k7 := 0xAB1C5ED5 (1010 1011 0001 1100 0101 1110 1101 0101)

k8 := 0xD807AA98 (1101 1000 0000 0111 1010 1010 1001 1000)

k9 := 0x12835B01 (0001 0010 1000 0011 0101 1011 0000 0001)

k10 := 0x243185BE (0010 0100 0011 0001 1000 0101 1011 1110)

k11 := 0x550C7DC3 (0101 0101 0000 1100 0111 1101 1100 0011)

k12 := 0x72BE5D74 (0111 0010 1011 1110 0101 1101 0111 0111)

k13 := 0x80DEB1FE (1000 0000 1101 1110 1011 0001 1111 1110)

k14 := 0x9BDC06A7 (1001 1011 1101 1100 0000 0110 1010 0111)

k15 := 0xC19BF174 (1100 0001 1001 1011 1111 0001 0111 0100)

Закон дистрибутивности. Дистрибутивность конъюнкции и суммы по модулю два.

(a and b) xor (a and c) = a and (b xor c) !!!

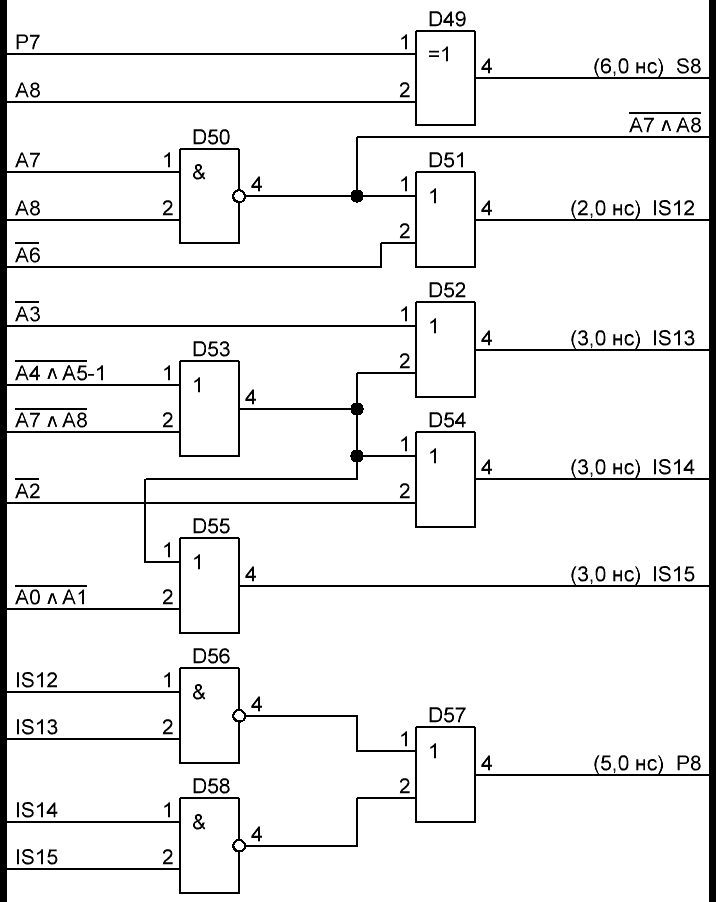

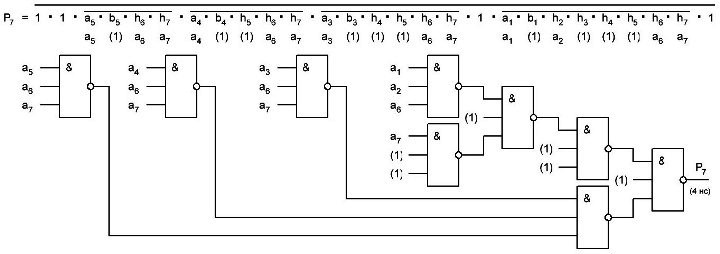

Функция большинства (Ma блок) побитово работает со словами A, B и C. Для каждой битовой позиции она возвращает 0, если большинство входных битов в этой позиции — нули, иначе вернёт 1 (См. Мажоритарный клапан - КР1533ЛП3).

Блок Σ0 циклически сдвигает A на 2 бита, затем исходное слово A циклически сдвигается на 13 бит, и, аналогично, на 22 бита. Получившиеся три сдвинутые версии A побитово складываются по модулю 2 (обычный xor, (A rotr 2) xor (A rotr 13) xor (A rotr 22)).

Ch реализует функцию выбора. На каждой битовой позиции проверяется бит из E, если он равен единице, то на выход идёт бит из F с этой позиции, иначе бит из G. Таким образом, биты из F и G перемешиваются, исходя из значения E.

Σ1 по структуре аналогичен Σ0, но работает со словом E, а соответствующие сдвиговые константы — 6, 11 и 25.

.

SHA-2 хеш алгоритм.

____В 1993 году NIST впервые опубликовал Стандарт Безопасного Хеша (SHA). В 1995 году этот алгоритм был пересмотрен с целью устранения некоторых начальных недостатков, а в 2001 году были предложены новые алгоритмы хеширования. Это новое семейство алгоритмов хеширования, известное как SHA-2, использует большие дайджест-сообщения, делая их более устойчивыми к возможным атакам и позволяя использовать их с большими блоками данных, вплоть до 2128 бит, например, в случае SHA512. Алгоритм хеширования SHA-2 одинаков для хэш-функций SHA256, SHA224, SHA384 и SHA512, различаясь только размером операндов, векторами инициализации и размером окончательного дайджест-сообщения.

____Далее описывается алгоритм SHA-2, применяемый к хеш-функции SHA256, после чего следует описание хеш-функции SHA512, которая отличается в основном размером операндов, используя 64-битные слова вместо 32-битных. Обратите внимание, что SHA224 и SHA384 вычисляются как SHA256 и SHA512, соответственно, с окончательным значением хеш-функции, усеченным до соответствующего размера, вектор инициализации также отличается.

____Функция хеширования SHA256: Функция хеширования SHA256 создает окончательное дайджест-сообщение из 256 битов, которое зависит от входного сообщения и состоит из нескольких блоков по 512 бит в каждом. Этот входной блок расширяется и подается на 64 цикла функции SHA256 в словах по 32 бита каждый (обозначается Wt). В каждом цикле или цикле алгоритма SHA-2 введенные данные смешиваются с текущим состоянием. Это скремблирование данных выполняется с помощью сложений и логических операций, таких как побитовые логические операции и побитовые вращения. Вычислительная структура каждого раунда этого алгоритма изображена на рисунке 1. Несколько функций, представленных на этом рисунке, описаны в Приложении I. Значение Wt является 32-разрядным словом данных для раунда t, а значение Kt представляет 32-битная константа, которая также зависит от раунда.

____32-битные значения переменных от A до H обновляются в каждом раунде, а новые значения используются в следующем раунде. Начальные значения этих переменных задаются 256-битным постоянным значением, указанным в [10], это значение устанавливается только для первого блока данных. В последовательных блоках данных используется промежуточное хеш-значение, вычисленное для предыдущего блока данных. Каждый блок 512 данных обрабатывается в течение 64 циклов, после чего значения переменных от A до H добавляются в предыдущее дайджест-сообщение для получения частичного Дайджест сообщения. Чтобы лучше проиллюстрировать этот алгоритм, представление псевдокода изображено на рисунке 2. Окончательное дайджест-сообщение (DM) для данного потока данных дается результатом последнего блока данных.

____В некоторых приложениях более высокого уровня, таких как эффективная реализация кода аутентификации хеш-сообщения с ключом (HMAC) [11] или когда сообщение фрагментировано, начальное значение хеш-функции (IV) может отличаться от константы, указанной в [10]. В этих случаях переменные от A до H инициализируются переменным вектором инициализации (IV).

____Хеш-функция SHA512: вычисление хеш-функции SHA512 идентично вычислению хеш-функции SHA256, отличающейся размером операндов, которые имеют 64 бита, а не 32 бита, как для SHA256, размера дайджест-сообщения, которое имеет удвоенный размер, составляющий 512 бит, и в функциях, описанных в Приложении I. В этом Приложении также описаны функции, используемые в расписании сообщений. Значения Wt и Kt имеют 64 бита, и каждый блок данных состоит из 16 64-битных слов, имеющих в общей сложности 1024 бита.

____Расписание сообщений: В алгоритме SHA-2 вычисления, описанные на рисунке 1, выполняются для 64 раундов для SHA256 (80 раундов для SHA512), в каждом раунде 32-битное слово (или 64 бита для SHA512), полученное из промежуточного слова. используется хэш-значение Однако каждый блок данных имеет только 16 32-битных слов для SHA256 или 16 64-битных слов для SHA512, что приводит к необходимости расширения исходного блока данных для получения оставшихся слов. Это расширение выполняется вычислением, описанным в (1), где M(i)t обозначает первые 16 слов i-го блока данных.

____Заполнение сообщения: чтобы гарантировать, что входное сообщение кратно 512 битам, как того требует хеш-функция SHA256, или 1024 для хеш-функции SHA512, необходимо дополнить исходное сообщение. Дополненное сообщение состоит из сообщения, с ничего не значащими данными, и присоединённым к нему оригинальным сообщением. Эта операция может быть эффективно реализована в программном обеспечении с минимальными затратами.

Proposed Design.

____В алгоритме SHA-2 операции, которые должны быть выполнены, просты, однако зависимость этого алгоритма от данных не допускает большого распараллеливания. Каждый раунд алгоритма может быть вычислен только после того, как были вычислены значения от A до H предыдущего раунда (см. Рисунок 2), что накладывает последовательность на вычисление. Следует отметить, что в каждом раунде вычисление требуется только для вычисления значений A и E, поскольку остальные значения получаются непосредственно из значений предыдущего раунда, как показано в псевдокоде на рис.2.

____Перепланирование операций: в нашем предложении мы определили часть вычисления данного раунда t, которая может быть вычислена заранее в предыдущем раунде t − 1. Только значения, которые не зависят от значений, вычисленных в предыдущем раунде, могут быть вычислены заранее. В отличие от метода перепланирования, предложенного в [12] для алгоритма SHA1, где взаимная зависимость данных является низкой, в алгоритме SHA-2 зависимость данных является более сложной, как показано на рисунке 1. Хотя переменные B, C, D , F, G и H получены непосредственно из значений раунда, не требующих каких-либо вычислений, значения A и E требуют вычислений и зависят от всех значений. Другими словами, значения A и E для раунда t не могут быть вычислены до тех пор, пока значения для тех же переменных не будут вычислены в предыдущем раунде, как показано в (2).

____Принимая во внимание, что значение Ht + 1 задается непосредственно через Gt, которое, в свою очередь, задается посредством Ft-1, предварительный расчет H, таким образом, может быть задан как Ht + 1 = Ft-1. Поскольку значения Kt и Wt можно предварительно рассчитать и просто использовать в каждом раунде, (2) можно переписать как:

где значение δt рассчитывается в предыдущем раунде. Значение δt + 1 может быть результатом полного сложения или векторов переноса и сохранения из сложения переноса. С этим вычислительным разделением вычисление алгоритма SHA-2 может быть разделено на две части, что позволяет переназначить вычисление δ на предыдущий тактовый цикл, изображенный серой областью на рисунке 3. Таким образом, критический путь результирующего оборудования реализация может быть уменьшена. Поскольку вычисление теперь разделено на этап конвейера, вычисление SHA-2 требует дополнительного тактового цикла для выполнения всех циклов. В случае хэш-функции SHA256 необходимо 65 тактов для расчета 64 раундов. Как указано в алгоритме SHA-2 и изображено на рисунке 2, после вычисления всех циклов внутренние переменные (от A до H) должны быть добавлены к предыдущему дайджест-сообщению.

Пометки:

1. # Майнер отправляет пулу nonce и хеш заданной сложности, пул подставляет этот nonce в заголовки блока и хеширует их, получил в результате тот же хеш - валидный, получил другой хеш - невалидный.

(если я как майнер состоящий в пуле, отсылаю пулу к примеру 100 nonce и соответствующих хешей, то пулл, будет пересчитывать все 100 хешей, что бы провалидировать? Тогда какой от меня смысл, если пул сам может считать эти хеши?)

# Майнер перебирает nonce, чтобы получить "красивый" хеш. Для этого нужно проделать МНОГО операций хеширования.

Пул проверяет, что присланные майнером nonce и хеш соответствуют друг другу. Это ОДНА операция хеширования.

(Как тогда майнинг пул проверит, что я реально работал и сколько работы я проделал, если я не нашел "красивый" хеш, хотя реально искал?)

# Например, сложность выставленная пулом равна 10 000, следовательно майнер будет находить соответствующий хеш в среднем за 10 000 итераций перебора nonce. Ключевое слово - в среднем. Сколько реально было итераций в конкретном случае - сугубо половые пробемы майнера и пулу на это положить, потому что в среднем будет 10 000, не смотря на то, что иной раз его можно найти с первой же итерации, а иногда не найти и за 20 000+ итераций. Как только майнер нашёл соответствующий хеш, он отправляет его и nonce пулу, а пул хеширует у себя и засчитывает майнеру 10 000 итераций. Проще говоря, пулу не нужно проверять сколько майнер сделал работы в каждом конкретном случае, потому что в среднем майнеру придётся перебирать столько, сколько требует заданная сложность, иначе он не найдёт требуемые хеши и отправлять будет нечего.

*задание содержит номер блока, ID задания, хэш предыдущего блока, минимальный и максимальный nonce для тебя

***

Начальные значения:

h0 := 0x6A09E667 (0110 1010 0000 1001 1110 0110 0110 0111)

h1 := 0xBB67AE85 (1011 1011 0110 0111 1010 1110 1000 0101)

h2 := 0x3C6EF372 (0011 0011 0110 1110 1111 0011 0111 0010)

h3 := 0xA54FF53A (1010 0101 0100 1111 1111 0101 0011 1010)

h4 := 0x510E527F (0101 0001 0000 1110 0101 0010 0111 1111)

h5 := 0x9B05688C (1001 1011 0000 0101 0110 1000 1000 1100)

h6 := 0x1F83D9AB (0001 1111 1000 0011 1101 1001 1010 1011)

h7 := 0x5BE0CD19 (0101 1011 1110 0000 1100 1101 0001 1001)

k0 := 0x428A2F98 (0100 0010 1000 1010 0010 1111 1001 1000)

k1 := 0x71374491 (0111 0001 0011 0111 0100 0100 1001 0001)

k2 := 0xB5C0FBCF (1011 0101 1100 0000 1111 1011 1100 1111)

k3 := 0xE9B5DBA5 (1110 1001 1011 0101 1101 1011 1010 0101)

k4 := 0x3956C25B (0011 1001 0101 0110 1100 0010 0101 1011)

k5 := 0x59F111F1 (0101 1001 1111 0001 0001 0001 1111 0001)

k6 := 0x923F82A4 (1001 0010 0011 1111 1000 0010 1010 0100)

k7 := 0xAB1C5ED5 (1010 1011 0001 1100 0101 1110 1101 0101)

k8 := 0xD807AA98 (1101 1000 0000 0111 1010 1010 1001 1000)

k9 := 0x12835B01 (0001 0010 1000 0011 0101 1011 0000 0001)

k10 := 0x243185BE (0010 0100 0011 0001 1000 0101 1011 1110)

k11 := 0x550C7DC3 (0101 0101 0000 1100 0111 1101 1100 0011)

k12 := 0x72BE5D74 (0111 0010 1011 1110 0101 1101 0111 0111)

k13 := 0x80DEB1FE (1000 0000 1101 1110 1011 0001 1111 1110)

k14 := 0x9BDC06A7 (1001 1011 1101 1100 0000 0110 1010 0111)

k15 := 0xC19BF174 (1100 0001 1001 1011 1111 0001 0111 0100)

***

Закон дистрибутивности. Дистрибутивность конъюнкции и суммы по модулю два.

(a and b) xor (a and c) = a and (b xor c) !!!

***

Функция большинства (Ma блок) побитово работает со словами A, B и C. Для каждой битовой позиции она возвращает 0, если большинство входных битов в этой позиции — нули, иначе вернёт 1 (См. Мажоритарный клапан - КР1533ЛП3).

Блок Σ0 циклически сдвигает A на 2 бита, затем исходное слово A циклически сдвигается на 13 бит, и, аналогично, на 22 бита. Получившиеся три сдвинутые версии A побитово складываются по модулю 2 (обычный xor, (A rotr 2) xor (A rotr 13) xor (A rotr 22)).

Ch реализует функцию выбора. На каждой битовой позиции проверяется бит из E, если он равен единице, то на выход идёт бит из F с этой позиции, иначе бит из G. Таким образом, биты из F и G перемешиваются, исходя из значения E.

Σ1 по структуре аналогичен Σ0, но работает со словом E, а соответствующие сдвиговые константы — 6, 11 и 25.

***

.

Последний раз редактировалось: Viktor2312 (Вс Июл 25 2021, 16:58), всего редактировалось 11 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

3

.

Пометки, отрывки, разное:

.

Пометки, отрывки, разное:

- Спойлер:

- По поводу первых 32 бит, которые должны быть нулями.

.

Последний раз редактировалось: Viktor2312 (Чт Июн 03 2021, 23:53), всего редактировалось 6 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

4

.

для i от 16 до 63

s0 := (w[i-15] rotr 7) xor (w[i-15] rotr 18) xor (w[i-15] shr 3)

s1 := (w[i-2] rotr 17) xor (w[i-2] rotr 19) xor (w[i-2] shr 10)

w[i] := w[i-16] + s0 + w[i-7] + s1

i = 16

s0 = (w[16-15] rotr 7) xor (w[16-15] rotr 18) xor (w[16-15] shr 3)

s0 = (w[1] rotr 7) xor (w[1] rotr 18) xor (w[1] shr 3)

s1 = (w[16-2] rotr 17) xor (w[16-2] rotr 19) xor (w[16-2] shr 10)

s1 = (w[14] rotr 17) xor (w[14] rotr 19) xor (w[14] shr 10)

w[16] = w[16-16] + s0 + w[16-7] + s1

w[16] = w[0] + s0 + w[9] +s1

Входные слова: w[0], w[1], w[9], w[14]

Выходное слово: w[16]

.

для i от 16 до 63

s0 := (w[i-15] rotr 7) xor (w[i-15] rotr 18) xor (w[i-15] shr 3)

s1 := (w[i-2] rotr 17) xor (w[i-2] rotr 19) xor (w[i-2] shr 10)

w[i] := w[i-16] + s0 + w[i-7] + s1

i = 16

s0 = (w[16-15] rotr 7) xor (w[16-15] rotr 18) xor (w[16-15] shr 3)

s0 = (w[1] rotr 7) xor (w[1] rotr 18) xor (w[1] shr 3)

s1 = (w[16-2] rotr 17) xor (w[16-2] rotr 19) xor (w[16-2] shr 10)

s1 = (w[14] rotr 17) xor (w[14] rotr 19) xor (w[14] shr 10)

w[16] = w[16-16] + s0 + w[16-7] + s1

w[16] = w[0] + s0 + w[9] +s1

Входные слова: w[0], w[1], w[9], w[14]

Выходное слово: w[16]

.

Последний раз редактировалось: Viktor2312 (Чт Май 28 2020, 09:50), всего редактировалось 4 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

5

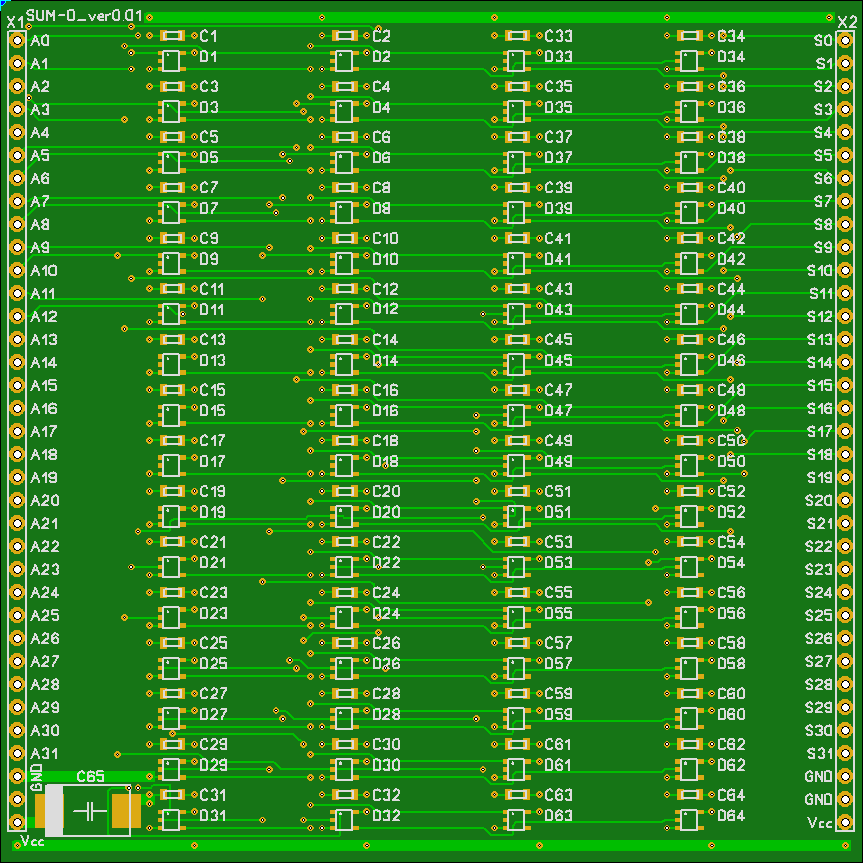

Подводим некую черту, этим сообщением. Пора начинать сначала и ближе к практике, хоть всё до конца и не понятно, но многое понятно, те же 64 итерации, их можно уже реализовывать, а всё остальное будет на отдельных, стандартных, платах. Продумав всё, в плане расположения плат, их соединения между собой, частичного параллелизма и асинхронного принципа, опять получается какой-то монстр, так как решено реализовывать на серии 74AC у которой как вроде максимальная тактовая частота в районе 170 МГц, точно нигде не прочитал, но судя по datasheet время задержки распространения находится в районе 1...10 нс, а как оно получится на практике, время покажет. Для того, чтобы передавать на нужную плату 16 слов, это w[0]...w[15] необходимо 16 шлейфов, они будут располагаться сзади и спереди. А так как каждый шлейф занимает 55 мм, то на плате умещается 4 разъёма, с каждой стороны, итого выходит потребуется 4 платы с размерами не менее этих четырёх разъёмов плюс место для разъёма питания и крепления 10 мм, в каждом углу платы. Входные и выходные слова будут находиться слева и справа, чередуясь от платы к плате. Что же выходит, с запада на восток, 4 разъёма (55 * 4 = 220 мм) + крепления (10 *2 = 20 мм), на разъём питания оставим 20 мм и между разъёмами 5 мм промежутки (5 *4 = 20 мм). Итого: 220 + 20 + 20 +20 = 280 мм (28 см). А с юга на север 4 разъёма (55 * 4 = 220 мм) + крепления (10 *2 = 20 мм) и между разъёмами 5 мм промежутки (5 *4 = 20 мм). Итого: 220 + 20 + 20 = 260 мм (26 см). Плат всего 4 шт. на одну итерацию, соответственно 28 + 28 = 56 см и по 10 см расстояние на шлейфы и вентиляцию, 76 см будет ширина, и 26 + 26 = 52 см и по 10 см расстояние на шлейфы и вентиляцию, 72 см это глубина, и минимум 65 слоёв плат, по 2 см на каждую и по 10 см расстояние на вентиляцию и крепления. 65 * 2 = 130 см и + 20 см, итого 150 см.

Вот такие примерные размеры шкафчика 76 х 72 х 150 см. Жуть... Но будет интересно...

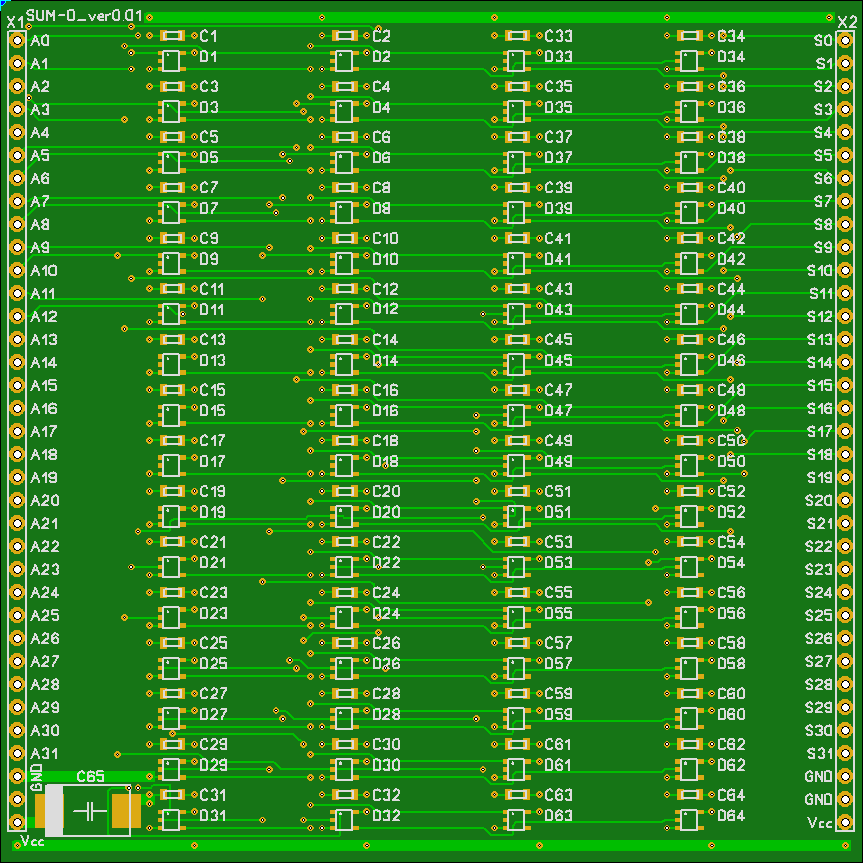

Плата A0-0. Условно показаны все разъёмы, но останутся только те, которые действительно нужны будут.

Изменённая ссылка, так как пока по предыдущей у меня ничего не отображается из-за действий преступной организации РКН (роскомпозор).

Ага, преступная организация не спит, и ссылки с http уже тоже не работают, придётся со временем всё дублировать троекратно, как минимум, задали работки на 5 лет вперёд, ну ничего, вечная борьба народа и дорвавшихся, продолжается, та же фотка, но выложенная на Яндексе:

Посмотреть

Твари всё пофигачили, как же они достали, ну ничего, мы с этим идиотизмом ещё поборемся...

Ура ! получилось, спасибо barsik за ссылку, но вот опять же вопрос, вот потрачу год или два и восстановлю, все изображения на форуме, в ручном режиме, добавив под каждым изображением копию на этом ресурсе, и где гарантия, что эта преступная организация не доберётся и до этого ресурса, никакой...

.

Вот такие примерные размеры шкафчика 76 х 72 х 150 см. Жуть... Но будет интересно...

Плата A0-0. Условно показаны все разъёмы, но останутся только те, которые действительно нужны будут.

Изменённая ссылка, так как пока по предыдущей у меня ничего не отображается из-за действий преступной организации РКН (роскомпозор).

Ага, преступная организация не спит, и ссылки с http уже тоже не работают, придётся со временем всё дублировать троекратно, как минимум, задали работки на 5 лет вперёд, ну ничего, вечная борьба народа и дорвавшихся, продолжается, та же фотка, но выложенная на Яндексе:

Посмотреть

Твари всё пофигачили, как же они достали, ну ничего, мы с этим идиотизмом ещё поборемся...

Ура ! получилось, спасибо barsik за ссылку, но вот опять же вопрос, вот потрачу год или два и восстановлю, все изображения на форуме, в ручном режиме, добавив под каждым изображением копию на этом ресурсе, и где гарантия, что эта преступная организация не доберётся и до этого ресурса, никакой...

.

Последний раз редактировалось: Viktor2312 (Чт Май 28 2020, 09:44), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

НАЧАЛО.

НАЧАЛО.

6

.

____Итак, всё что выше, это либо описание теории самой, по крайней мере самого основного, либо просто предварительное обдумывание. Предварительные наброски, для оценки габаритов, различных затрат и т. д. В результате их стало понятно, что делать майнер по классической схеме, когда делается "в железе" одна итерация, и потом данные гоняются через неё, нет смысла. Для этого нужно брать крутейшую микросхему ПЛИС с техпроцессом 7 нм и на ней всё делать и не факт, что будет круче микросхемы выполненной по технологии ASIC. Да и не готов я это реализовать в полной мере на данный момент, задача немного другая.

____А задача состоит в том, чтобы понять всё, что необходимо для реализации майнера в железе, и на данный момент не всё понятно. А так же обойти различные подводные камни и сделать его супер быстрым. А для этого необходимо реализовать, как минимум все 64 итерации в виде схемы с единым потоком данных, не готов пока на пальцах описать, что имею в виду, но по ходу реализации это станет понятно.

____И на данный момент задачу нашу можно разбить на некоторое количество частей. Первая часть и мы ею будем заниматься потом, это получение данных от пула и отправка ему результатов, пока это всё просто в тумане. Вторая задача, это разбиение полученного message и дополнение. Третья задача, это получение дополнительных слов. И четвёртая создание непосредственно 64-x итераций с подсчётом результатов в первых, начальных, итерациях. И реализовывать это всё будем с конца, так сказать от простого к сложному, по крайней мере по тому, что я уже понял. Хотя уверенности что я всё понял правильно нет вообще никакой, так как информации катастрофически мало, проконсультироваться так же практически не с кем, а те разработчики майнеров, с которыми я общался, например майнера z-enemy, в основном занимаются soft майнерами для GPU, и мало предоставляют полезной информации, по крайней мере понятной для меня на данном итапе развития...

____Дальше, ниже, постепенно будет отображаться процесс разработки, от теории, просчёта, и проектирования, вплоть до железа, в качестве которого пока рассматиривается серия микросхем 74ACxxx. Ну и из предварительных раздумий, стало понятно, что только применение SMD компонентов, абсолютно всех, возможно позволит создать относительно компактное устройство.

____Естественно, если кто-то захочет что-то написать, или проконсультироваться или наоборот помочь, что-то подсказать или поправить увидев явные какие-то ошибки, это очень приветствуется...

____Итак, ниже представлена структурная схема одной итерации, немного видоизменённая мной, из учёта правила, что от перемены мест слогаемых сумма не меняется, поэтому мы сначала сможем сложить h+Ki, так же сможем сложить Ch+Cy1, здесь Cy1 это вместо значка суммы от слова carry (почему мне вчера пришло на ум именно carry, а не aderr, это всё потому, что не давала покоя проблема переноса. Так как уже было понятно, что 0-я итерация сведётся к двум квантам времени. В первом будет находиться T1, а во втором A и E. И тут возникает проблема, что даже при применении микросхемы CD74ACT283M у которой время выдачи бита переноса занимает 2,7 нс при самых идеальных условиях. А именно, качественный монтаж, питание +5,5 В и исполнение выдерживающее +125 градусов, а так же выдача результата 3,3 нс. И так как этих микросхем для 32-разрядов требуется 8 шт., то имеем, что задержка в первых семи микросхемах будет 2,7 нс, что в сумме составит 18,9 нс и в последней, восьмой, 3,3 нс. А общая минимальная задержка будет 18,9 + 3,3 = 22,2 нс. Что очень медленно, если учесть, что у нас два кванта времени и общая задержка выполнения 0-й итерации будет 44,4 нс. А поэтому нужен полностью параллельный суматор с параллельным переносом на все 32-разряда, либо применение другой, ещё более быстродействующей логики, что не жалательно, либо скорее всего переход от позиционной арифметики к модулярной системе счисления). И сложить полученные значения между собой. В результате потребуется только один сумматор для сложения полученного результата с словом Wi, чтобы получить Т1.

____Хотя, нужно будет проверить идентичность результата, взять любое случайное число Wi и подсчитать результат по старой схеме и по новой, будет ли он совпадать...

Итак, в виду того, что:

Инициализация переменных

(первые 32 бита дробных частей квадратных корней первых восьми простых чисел [от 2 до 19]):

h0 := 0x6A09E667

h1 := 0xBB67AE85

h2 := 0x3C6EF372

h3 := 0xA54FF53A

h4 := 0x510E527F

h5 := 0x9B05688C

h6 := 0x1F83D9AB

h7 := 0x5BE0CD19

Мы имеем начальные фиксированные значения для слов в первой итерации, пардон, в нулевой итерации...

a := h0

b := h1

c := h2

d := h3

e := h4

f := h5

g := h6

h := h7

Мы не будем это всё реализовывать в железе и тратить на это "железо", деньги и время, время на вычисления, каждый раз...

Cy0 = (a rotr 2) xor (a rotr 13) xor (a rotr 22)

a = 0x6A09E667

(a rotr 2) = 0xDA827999

(a rotr 13) = 0x333B504F

(a rotr 22) = 0x27999DA8

0xDA827999 xor 0x333B504F = 0xE9B929D6

Cy0 = 0xE9B929D6 xor 0x27999DA8 = 0xCE20B47E

Для 0-й итерации:

Maj = (a and b) xor (a and c) xor (b and c)

(a and b) = 0x6A09E667 and 0xBB67AE85 = 0x2A01A605

(a and c) = 0x6A09E667 and 0x3C6EF372 = 0x2808E262

(b and c) = 0xBB67AE85 and 0x3C6EF372 = 0x3866A200

0x2A01A605 xor 0x2808E262 = 0x02094467

Maj = 0x02094467 xor 0x3866A200 = 0x3A6FE667

T2 = Maj + Cy0

T2 = 0x08909AE5

____Прежде чем продолжить дальше, нужно проверить закон:

Закон дистрибутивности. Дистрибутивность конъюнкции и суммы по модулю два.

(a and b) xor (a and c) = a and (b xor c) !!!

____Он позволит нам в каждом блоке Maj избавитя от одной операции and, что сэкономит 8 микросхем. Итак преобразуем формулу:

Maj = (a and b) xor (a and c) xor (b and c), в

Maj = (a and (b xor c)) xor (b and c), и посчитаем, получится ли у нас тот же результат:

Maj = (0x6A09E667 and (0xBB67AE85 xor 0x3C6EF372)) xor (0xBB67AE85 and 0x3C6EF372) =

= (0x6A09E667 and 0x87095DF7) xor 0x3866A200 =

= 0x02094467 xor 0x3866A200 = 0x3A6FE667

Результаты совпали, ура, мы сэкономим огромное количество микросхем, а точнее в 126 итерациях по 8 микросхем, то есть 1008 шт. Ну или кучу логических ячеек, при реализации в ПЛИС. То есть не нужно тратить 4032 логических элемента 2И.

Далее вычисляем:

Cy1 = (e rotr 6) xor (e rotr 11) xor (e rotr 25)

h4 := 0x510E527F

e := h4

(0x510E527F rotr 6) = 0xFD443949

(0x510E527F rotr 11) = 0x4FEA21CA

(0x510E527F rotr 25) = 0x87293FA8

0xFD443949 xor 0x4FEA21CA = 0xB2AE1883

0xB2AE1883 xor 0x87293FA8 = 0x3587272B

Cy1 = 0x3587272B

____Далее вычисляем значение на выходе блока Ch:

Ch = (e and f) xor ((not e) and g)

e = 0x510E527F

f = 0x9B05688C

g = 0x1F83D9AB

(not e) = 0xAEF1AD80

Ch = (0x510E527F and 0x9B05688C) xor (0xAEF1AD80 and 0x1F83D9AB) =

= 0x1104400C xor 0x0E818980 = 0x1F85C98C

Ch = 0x1F85C98C

____Находим сумму Adder4:

Adder4 = Ch + Cy1

Adder4 = 0x1F85C98C + 0x3587272B

Adder4 = 0x550CF0B7

____Находим сумму Adder1:

K0 = 0x428A2F98

Adder1 = h + k0

Adder1 = 0x5BE0CD19 + 0x428A2F98

Adder1 = 0x9E6AFCB1

____Находим сумму Adder2:

Adder2 = Adder1 + Adder4

Adder2 = 0x9E6AFCB1 + 0x550CF0B7

Adder2 = 0xF377ED68

____И в итоге, мы имеем полностью просчитанную нулевую итерацию. Остаётся в ней реализовать три "железных" сумматора, для того, чтобы находить T1, A и E. Естественно все вычисления нужно будет ещё раз проверить, и проверить с произвольным Wi внесённые изменения.

____А вот проблема сумматоров теперь максимально остро стоит, нам нужно очень высокое быстродействие, конечно как крайний вариант, это CD74AC283M в количестве 8 шт. для каждого сумматора с максимально достижимым быстродействием в 22,2 нс. в виду того, что между тетрадами у нас последовательный перенос будет. Но, по хорошему нужно рассмотреть реализацию и применение 32-разрядного сумматора не только с параллельным вводом, но и паралельным переносом, хотя бы по 16 бит, в идеале все 32 бита. Но опять же это сильно увеличивает объём "железа", в общим палка о двух концах. Ладно, будем пока потихоньку двигаться дальше и решать проблемы по мере их поступления...

____Проверил, какой результат выдаёт оригинальная схема, например при Wi = 0x3B217FE2 и преобразованная, результаты совпали T1 = 0x2E996D4A, то есть правило "от перемены мест слагаемых сумма не меняется" действует, блин ещё бы ему не действовать, это же 1 класс школы, но просто хотелось убедиться на практике. В общим замечательно, структурная схема со всеми расчётами приведённая выше верная и можно приступать к "железу", хотя бы в теоретическом плане. Модификаций сумматоров будет несколько, скорее всего. Так как наш Adder3, например, имеет константу на одном из входов, а соответственно можно избавиться от 32 контактов, если делать сумматоры в виде отдельной платки, устанавливаемой на основную. Я думаю вы уже поняли, что я хочу сделать не одну итерацию в виде платки и потом с помощью регистров защёлкивать результат и гнать его на вход, подставляя нужные Ki и Wi, а в виде единого потока данных, с одновременной подачей сразу всех Wi для всех 64 итераций, ну да ладно, это не так важно сейчас, посмотрим, что из этого получится, просто по объёму "железа" выходит очень много, ну и пофиг, будем изголяться...

____Сейчас посидел, немного подумал и выходит, что скорость сумматора на CD74AC283M получается переменной, в зависимости от того, есть переносы или нет. В итоге, при определённых числах на входе, когда все переносы равны нулю, то есть их нет, то результат будет валидным уже через 3,3 нс, и самый идеальный вариант, что и в других двух сумматорах, которые работают параллельно, будет такая же ситуация. Тогда время вычисления 0-й итерации будет 6,6 нс, но это, самое максимальное быстродействие при определённых значениях входных переменных, ну а максимальный-идеальный остаётся прежним 44,4 нс. В общим пока ковыряю параллельный сумматор, с параллельным переносом на отдельных логических элементах, просто возможно получися уменьшить количество "железа" в силу того, что у нас одна из переменных имеет определённое значение, а соответственно внутри сумматора, в случае бита слагаемого равного нулю, элемент XOR превращается в повторитель и таким образом его можно вообще убрать из схемы, задержка становится равной 0 нс, да и потребление 0.

____Ну вот, день прошёл не зря, удалось заменить в первой тетраде микросхему CD74AC283M то есть полный 4-разрядный сумматор, у которого время выдачи результата 3,3 нс, а время выдачи бита переноса 2,7 нс, на схему на логических элементах, ну точнее элементе. Потребовался всего один логический элемент НЕ (not) от микросхемы SN74AC04. А это соответственно снижение потребляемой мощности, конкретно этим участком схемы, а также увеличение быстродействия, теперь бит переноса выдаётся за 0 нс, а результат за 1 нс.

____Удалось это сделать конечно только благодаря тому, что одно из слагаемых является константой у нас это число 0x8 (1000), Ну а второе естественно может иметь 16 значений от 0000 до 1111.

____В результате разработки сумматора для следующей тетрады, для битов от I0WI4...I0WI7 задержка распространения, минимально достижимая, вышла 3 нс, а вот количество элементов больше 1...2 корпусов микросхем. Поэтому решил, что проще поставить обычный сумматор, в идеале CD74ACT283 но его нужно будет искать в исполнении на 125 градусов и питать напряжением +5,5 В. Так как в datasheet именно при этих двух параметрах можно получить максимальное быстродействие, то есть минимальные задержки, а именно выдача результата через 3,3 нс и бита переноса через 2,7 нс. В нашем же случае, мы для получения результата будем использовать сумматор, а бит переноса получать не за 2,7 нс взяв его с самой микросхемы, а получать его отдельно при помощи двух логических элементов ИЛИ (or) и И (and), что даёт нам время задержки 2 нс. Таким образом по 8 битам мы имеем, время выдачи результата, через 3,3 нс, а не 6 нс и бит переноса С2 через 2 нс, а не через 5,4 нс.

____Хе хе, а вот и не правильно, я забыл просчитать, если бит переноса из первой тетрады равен 1, то схема уже не пашет на этих двух лог. элементах. Так что во второй тетраде полностью будет задействована микросхема сумматора, и время задержек - результат через 3,3 нс, бит переноса С2 через 2,7 нс.

____Да, медленно. Выход только один, параллельный сумматор, с параллельным переносом на все 32 бита. Тут проще взять формулу в базисе логического элемента И-НЕ (nand) и преобразовать в соответствии с быстродействием конкретных микросхем, например та же ЛА3 от TI имеет минимально достижимую задержку 1,5 нс, в то время как ЛА4 - 1 нс, если судить по datasheet, да меньше на один логический элемент, но тут уже и 1 нс кажется огромной задержкой... В общим, нужно начинать просчитывать полностью с параллельным переносом сумматор. Вся проблема, что больше 8 входов как вроде нет ЛА2 а нужно и с 32 входами И-НЕ элемент, а это только при помощи наращивания и дополнительные ступени, опять же дополнительные 1...2 нс. Но, всё равно выигрыш, пусть даже 3 ступени, и каждая по 1 нс, то это 3 нс, 1 нс в сумматоре, всего 4 нс, против 22,2 нс, в общим... Нужно мучить формулу, чертить схему, с учётом что оба операнда не константы, и будет точно уже потом ясно, где константы, там понятно, всё проще и компактнее...

Где бы ещё время взять, работа, ремонт, пустой холодильник, да и спать иногда желательно...

Ладно, фигня это всё, есть над чем поработать, поразмыслить, что поковырять, больше беспокоит, не приведёт ли ёмкость и индуктивность монтажа, паразитные наводки и весь остальной гемор, к тому, что будет всё с параметрами не min, и даже не typ, а max и тогда это печально, так как это даже не уровень К531 серии будет, у которой в среднем 5...7 нс. Но думаю, коли уж К531 серия в середине 70-х позволяла 5...7 нс, то уж 74ACxxx с SMD монтажом и корпусами, да и платы покачественнее на пару порядков, должны справиться... Слишком много неизвестных...

Ладно, это так, мысли в слух, поживём посмотрим, как оно пойдёт дальше, впереди слишком много ещё работы...

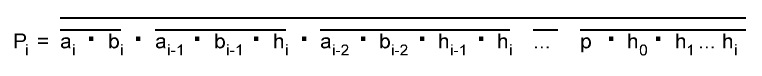

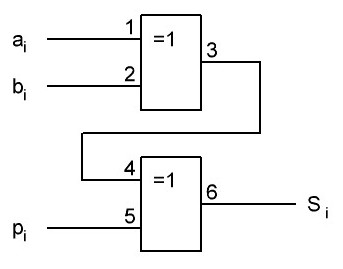

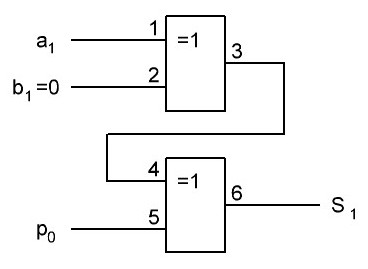

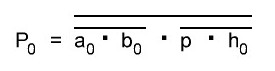

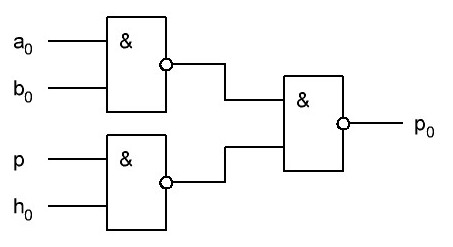

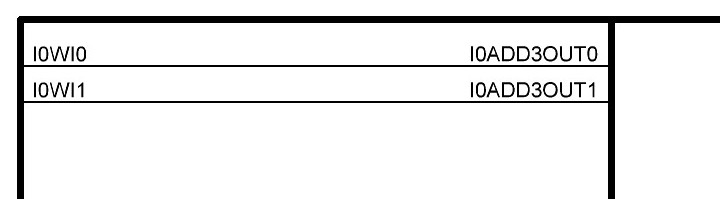

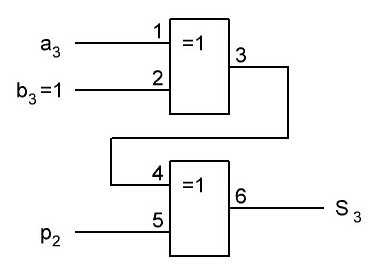

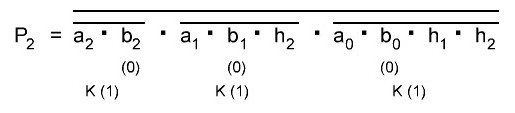

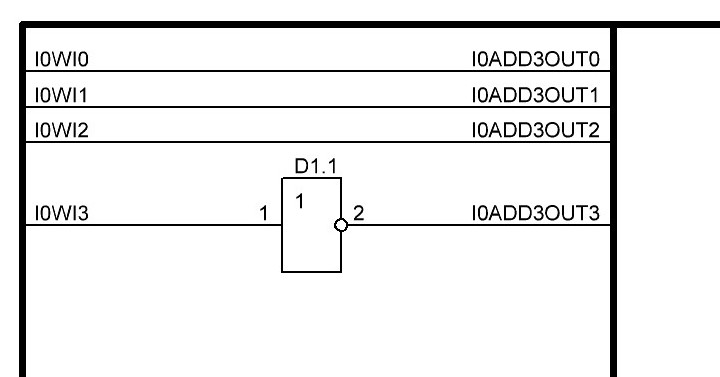

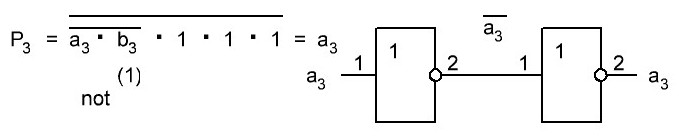

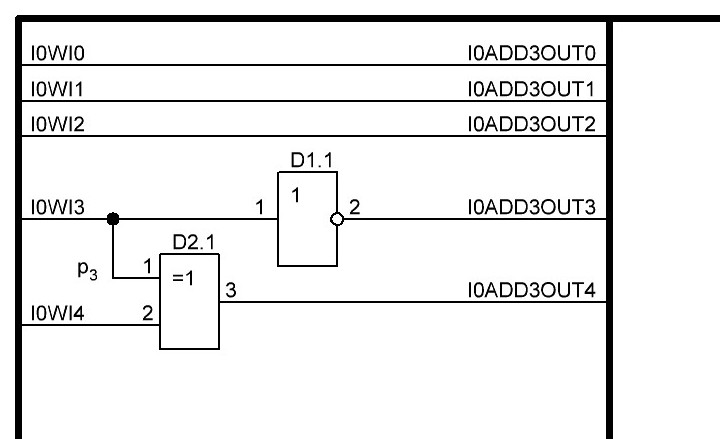

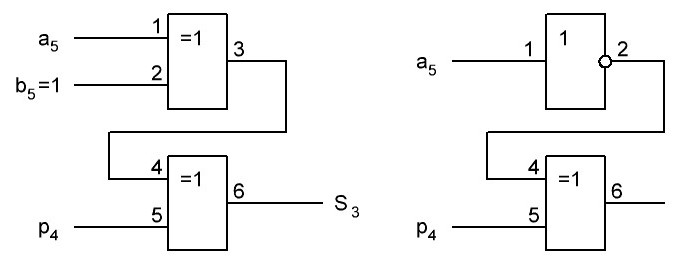

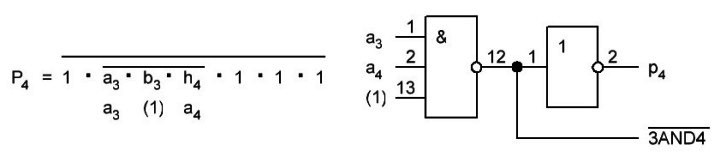

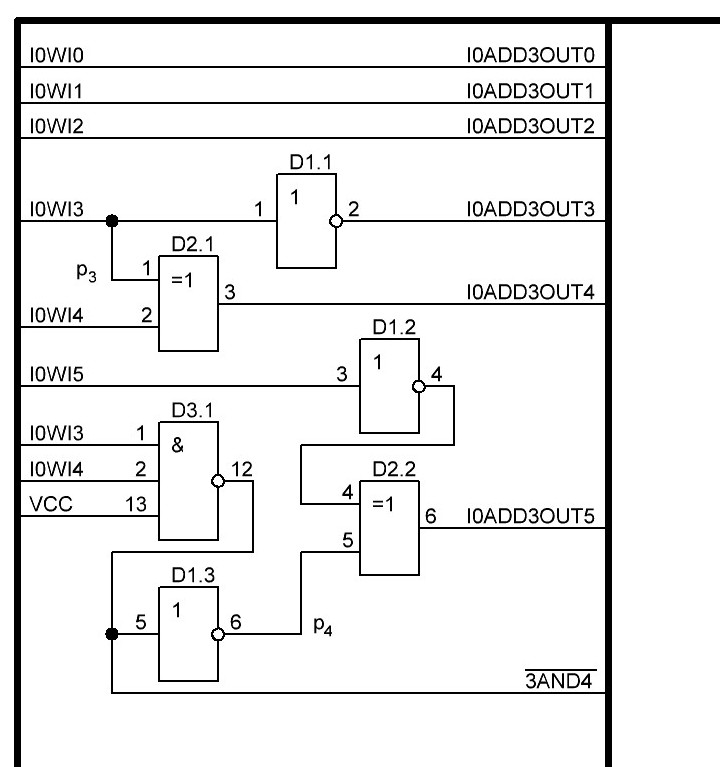

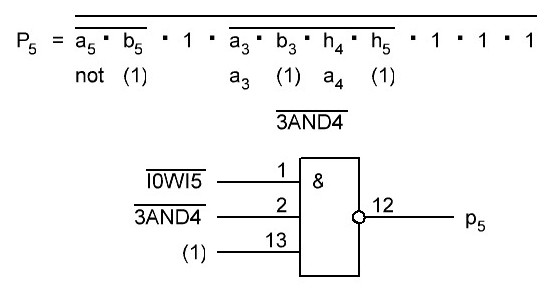

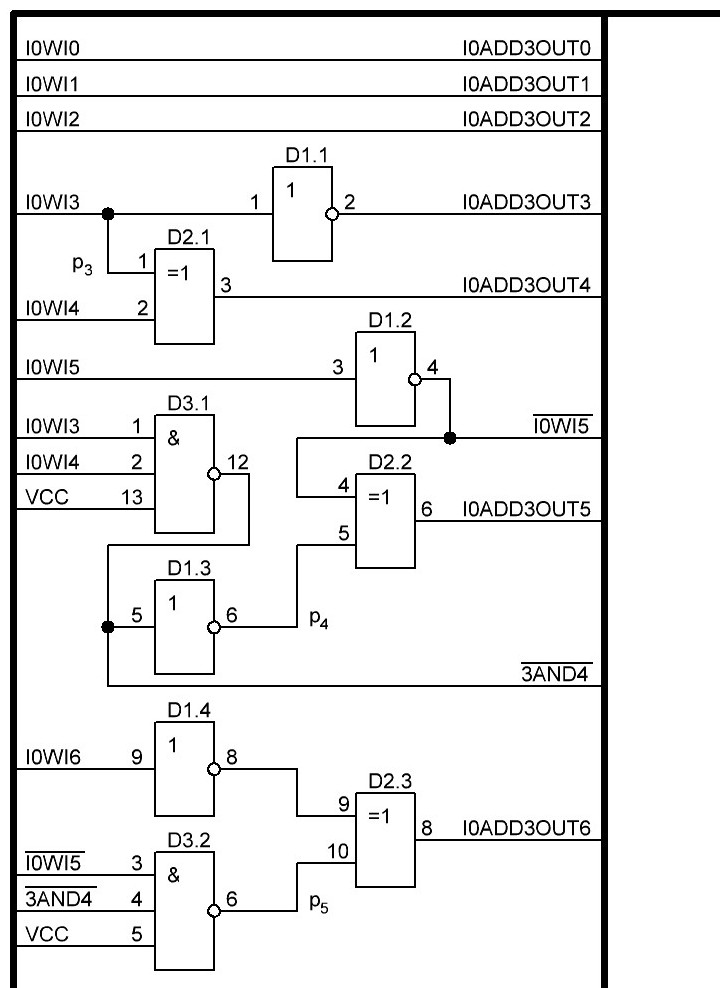

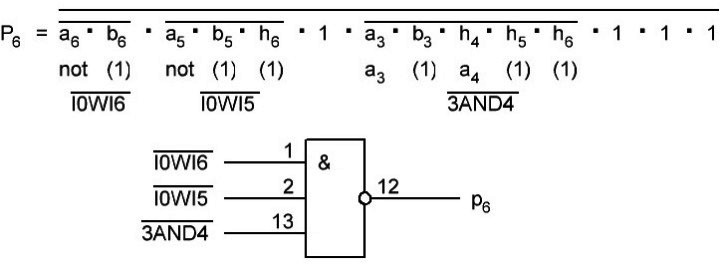

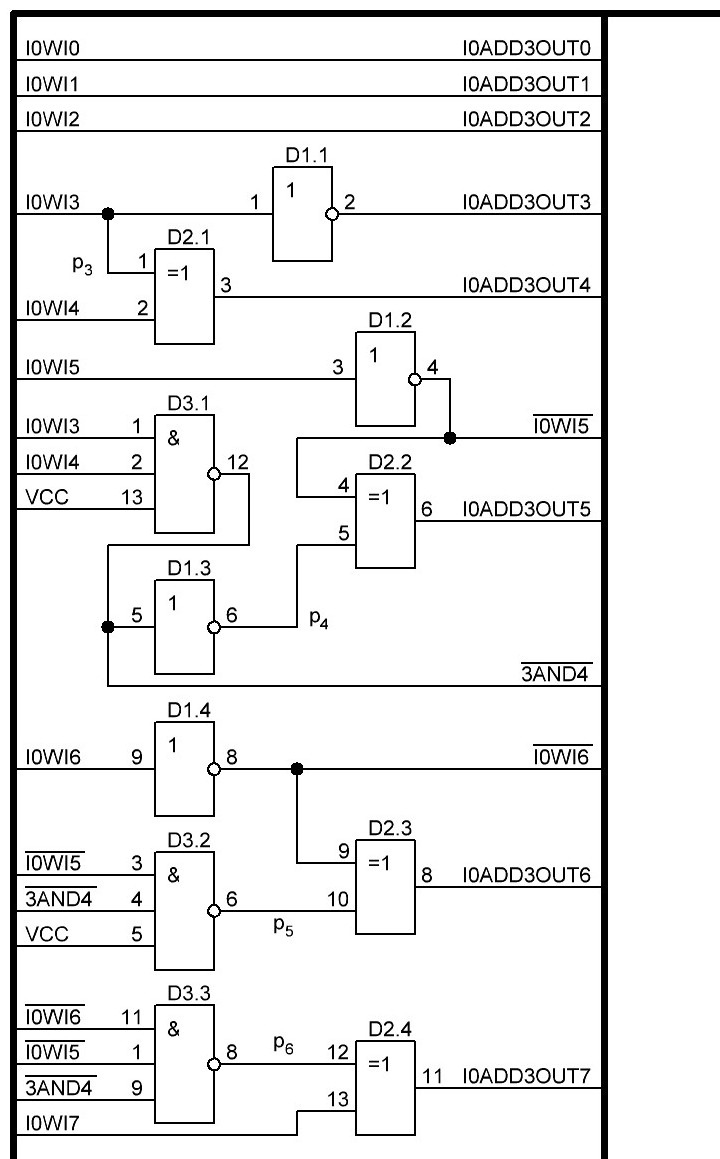

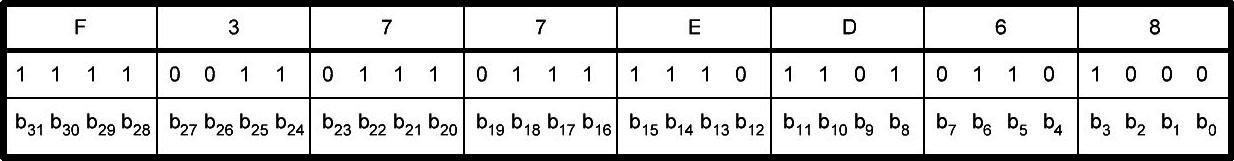

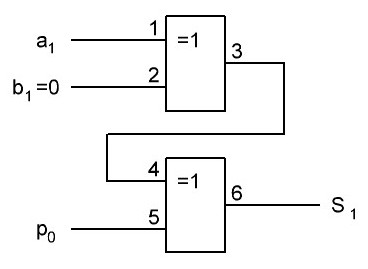

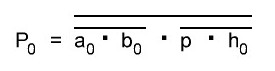

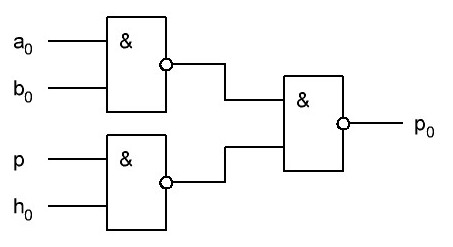

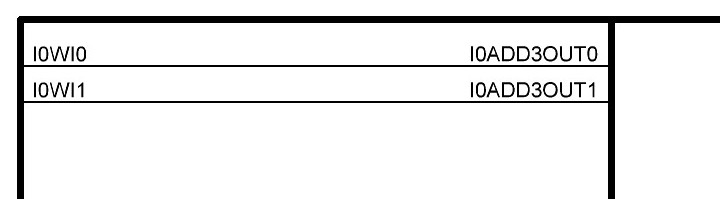

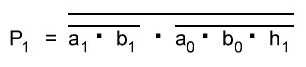

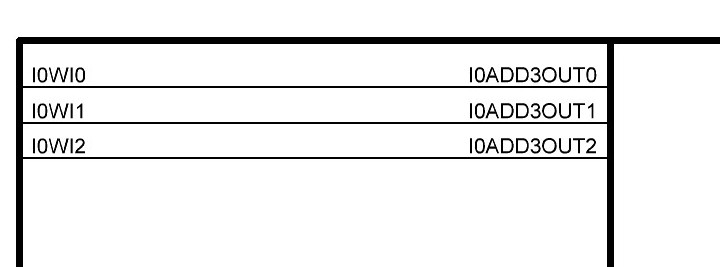

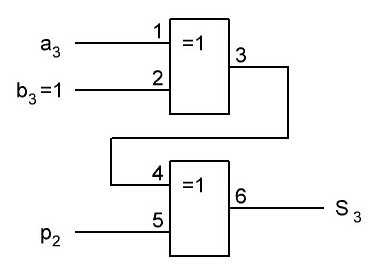

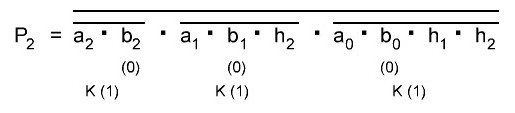

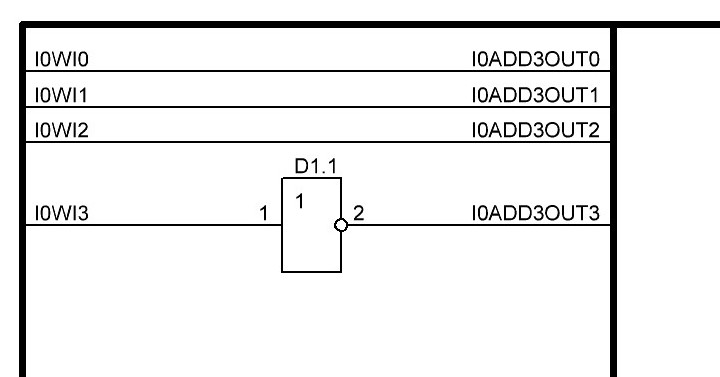

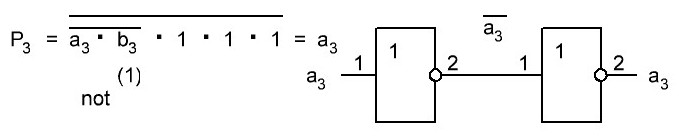

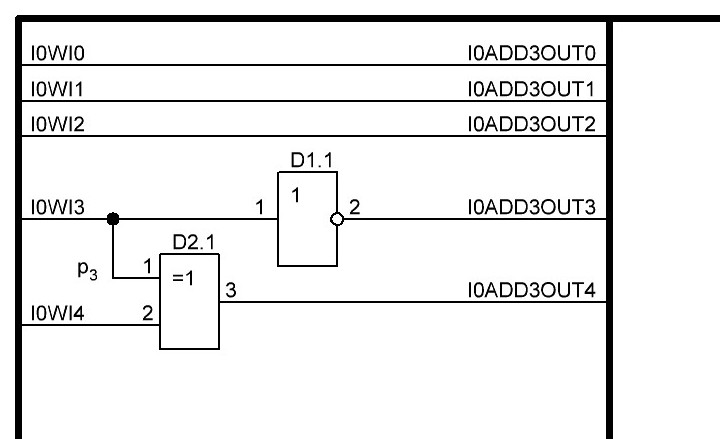

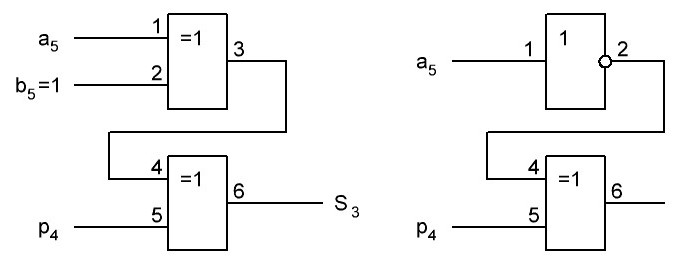

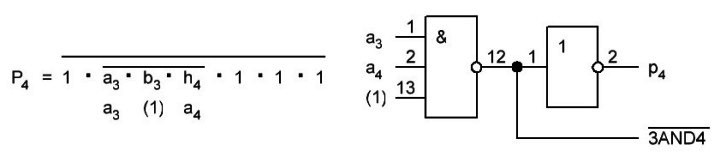

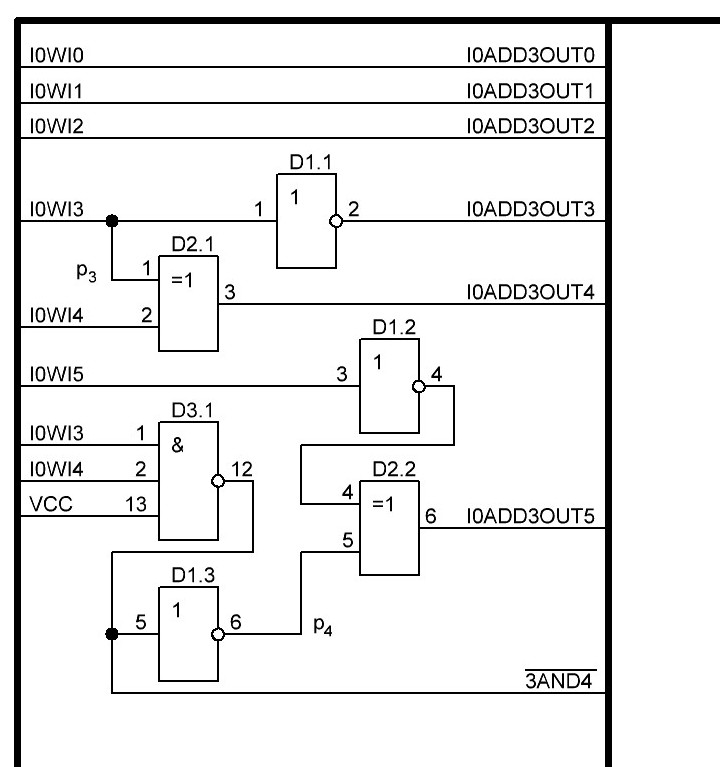

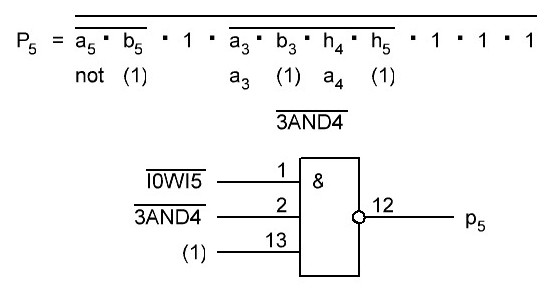

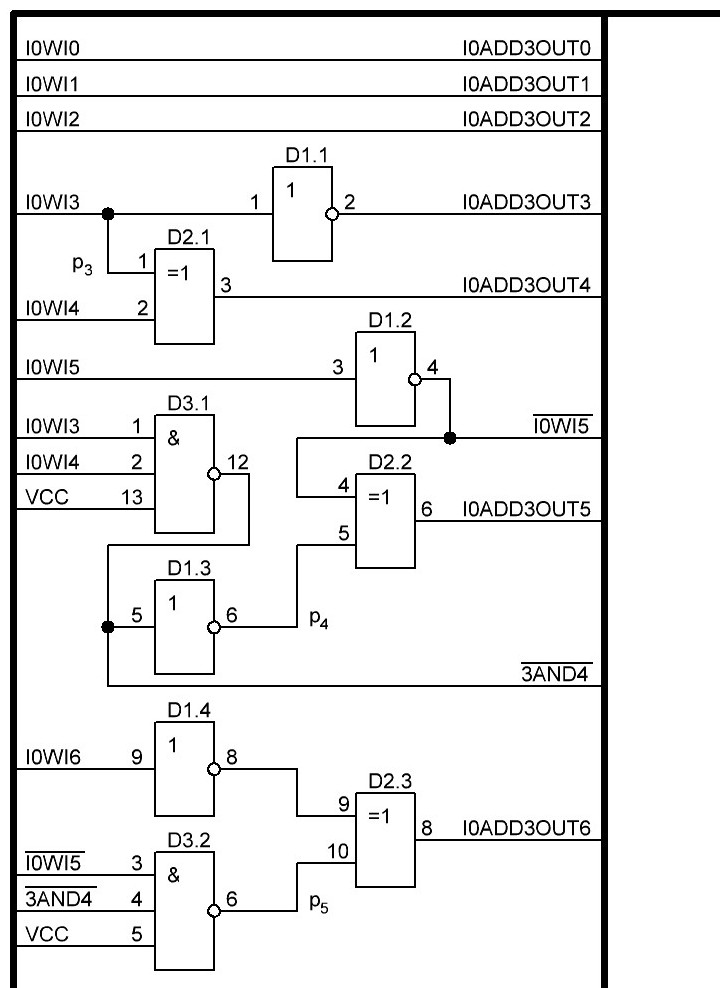

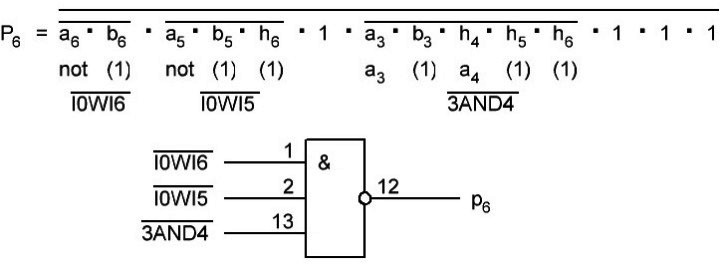

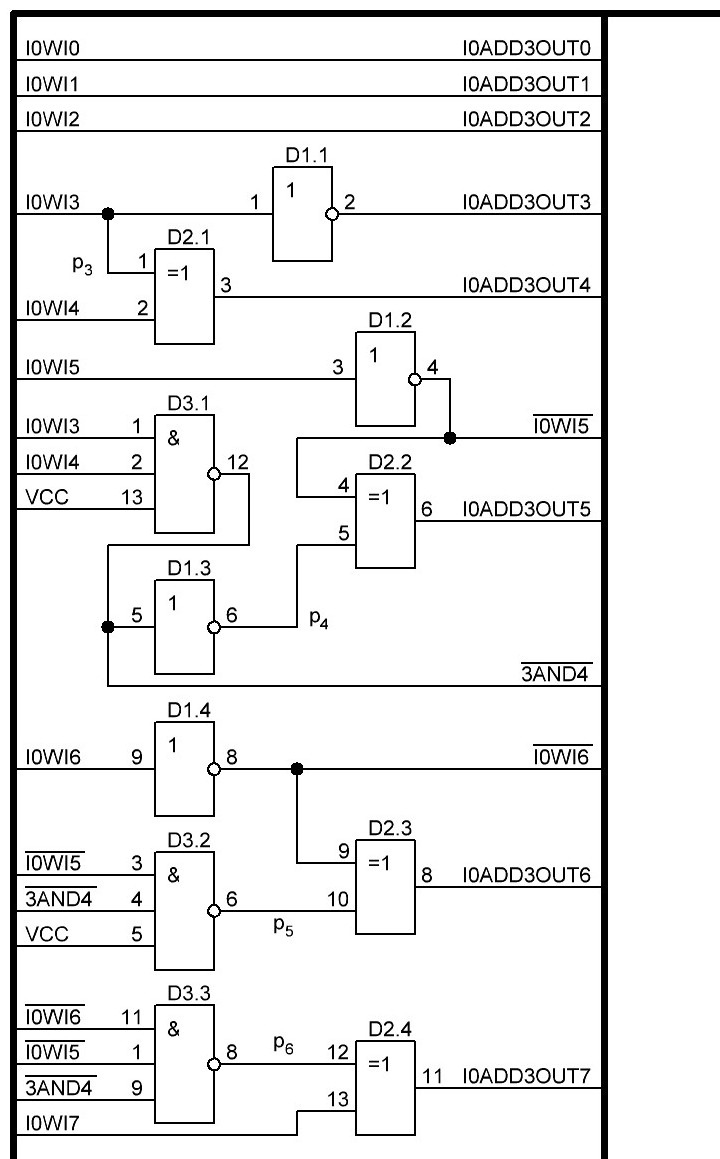

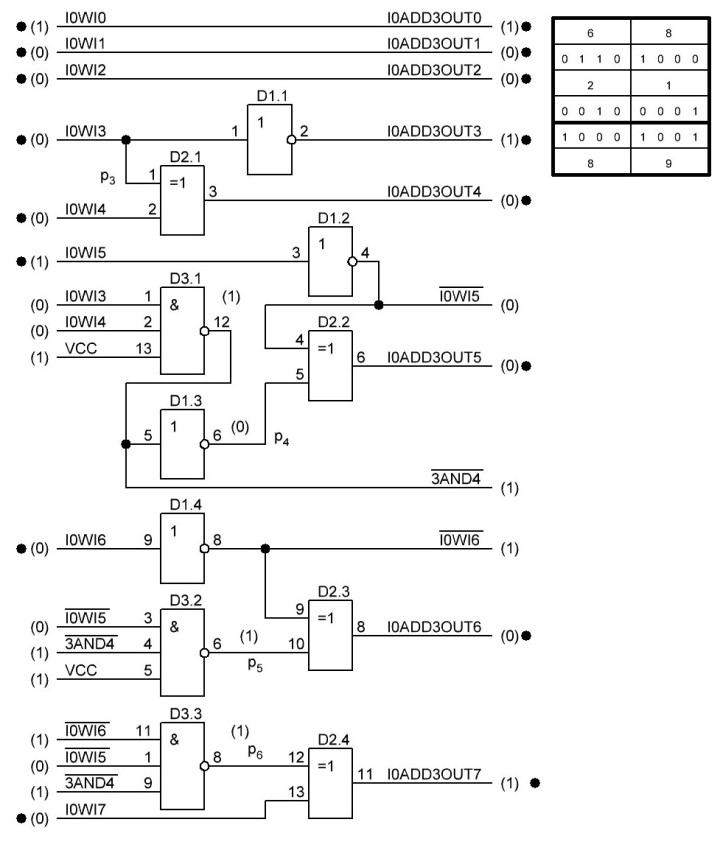

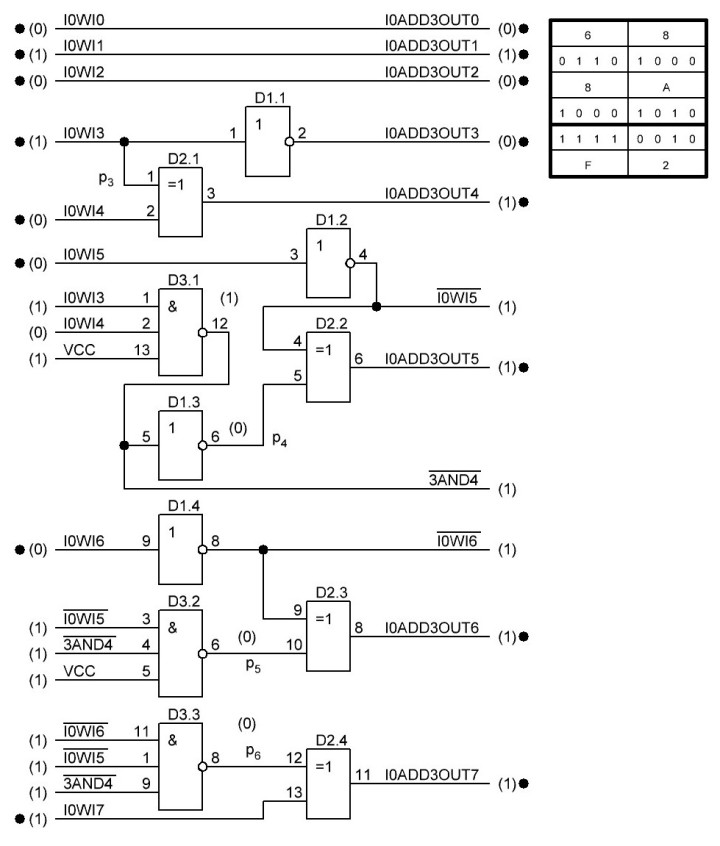

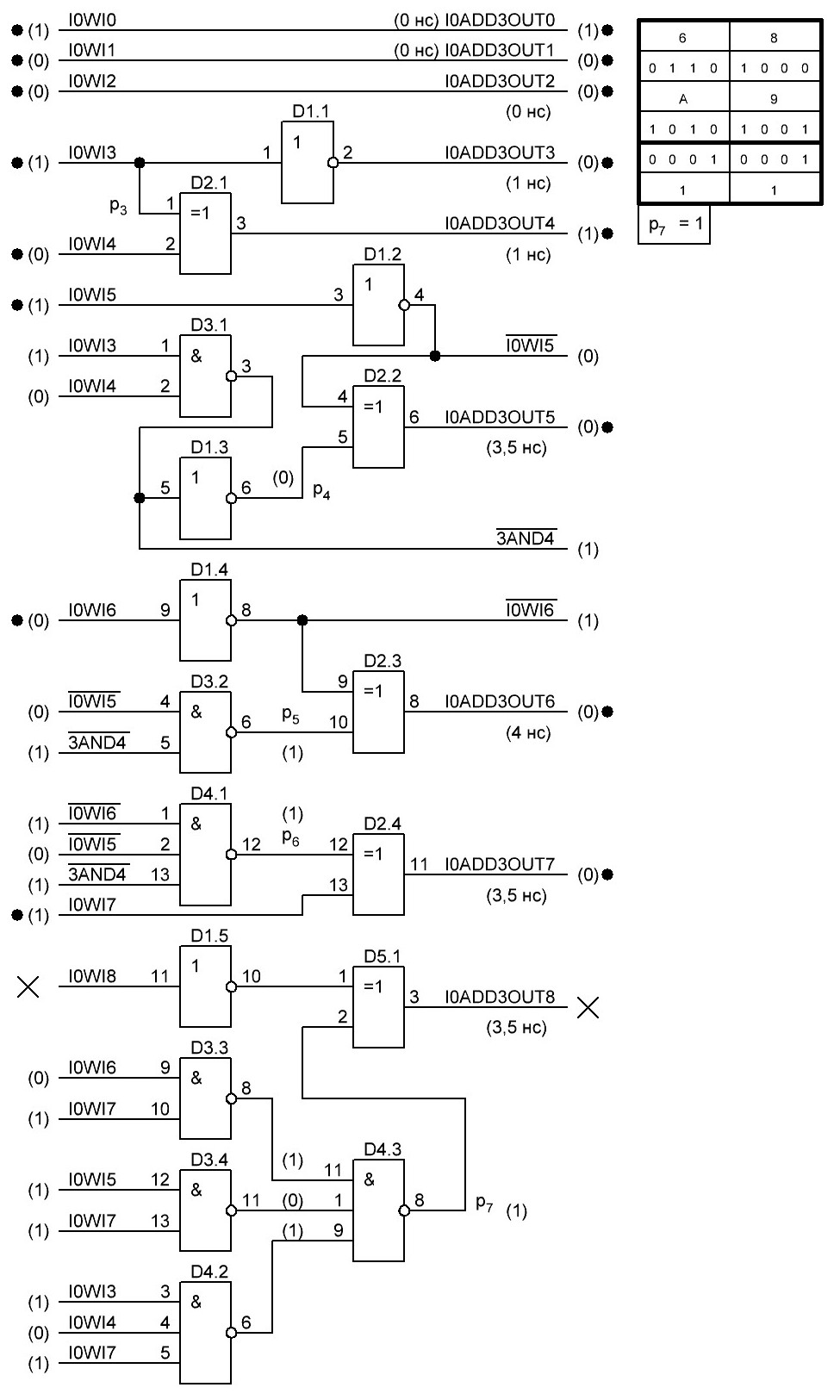

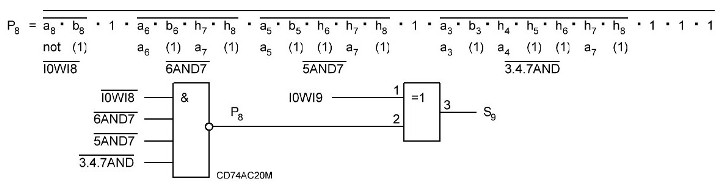

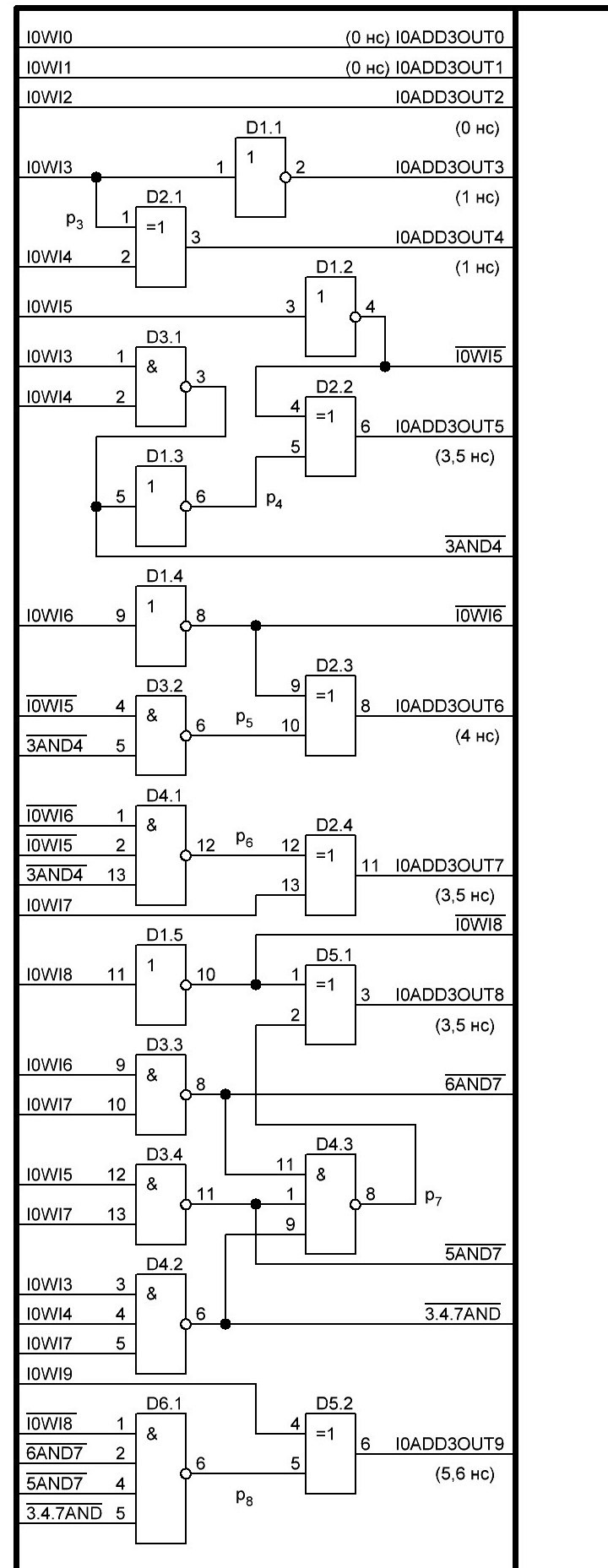

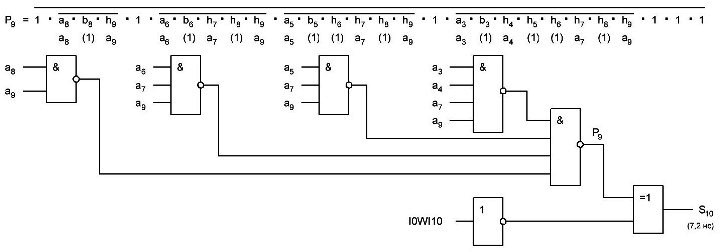

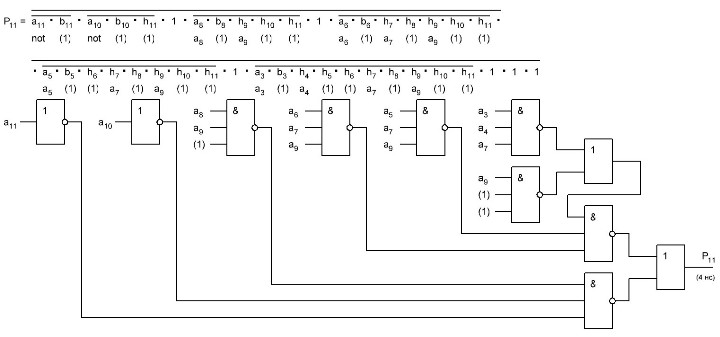

Итак, делаем параллельный сумматор с параллельным переносом для Adder3 первые 4 бита у нас готовы, следующий бит I0ADD3OUT4 требует одного элемента "исключающее ИЛИ" (XOR), на один вход подаётся четвёртый бит слова, а на второй третий бит слова, так как формула переноса полностью коллапсирует до повторителя для P3 (Пэ три):

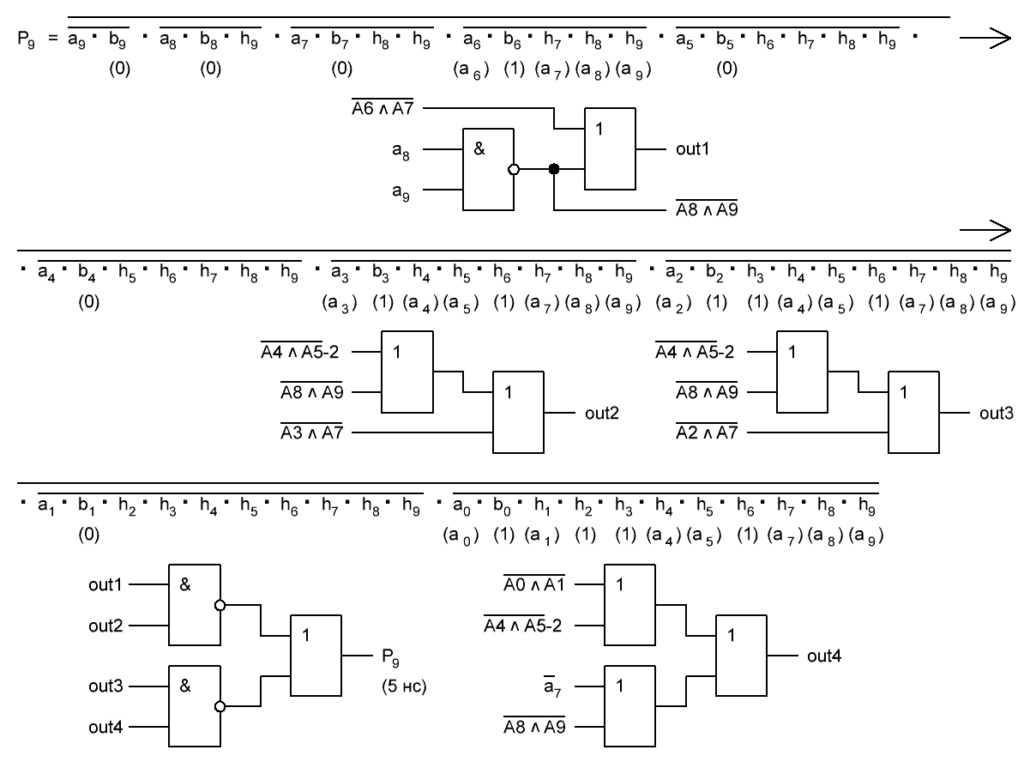

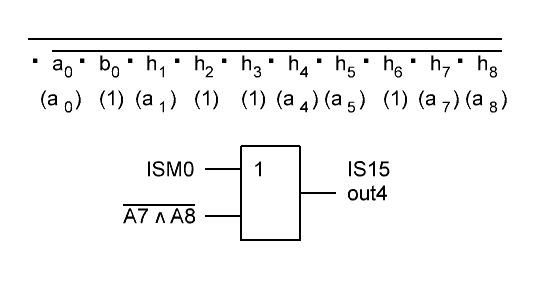

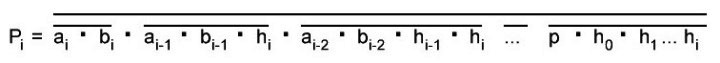

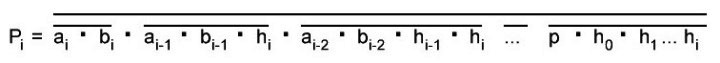

P3 = / /ai . bi . /ai-1 . bi-1 . hi-1 . /ai-2 . bi-2 . hi-1 . hi . /ai-3 . bi-3 . hi-2 . hi-1 . hi . /p . h0 . h1 . h2 . h3

Как видим /ai . bi

это для P3

/a3 . b3

а b3 = 1 соответственно наш логический элемент 2И-НЕ имеет на одном из входов константу равную всегда лог.1 и соответственно элемент становится просто инвертором. Во всех остальных частях формулы у нас присутствуют p, b0, b1, b2 которые так же константы и равны лог. 0 из-за чего каждый из этих элементов всегда на выходе имеет константу равную лог. 1, соответственно общая инверсия, то есть по сути это логический элемент 5И-НЕ, становится инвертором для /a3 . b3 и поэтому нет смысла пропускать сигнал a3 через два последовательно включённых инвертора, поэтому он у нас приходит на прямую на сумматор, который так же упрощается до одного логического элемента XOR...

Процесс потихоньку идёт, просчитал 8 бит, получилось компактненько, 4 корпуса микросхем и то есть ещё 5 свободных логических элемента и задержка пока что составляет 3 нс, естественно минимально достижимая при различных условиях, оговоренных выше, т. е. питание 5,5 В, и т. д. Продолжу просчитывать дальше на днях по мере появления свободного времени.

Итак, сегодня (18.06.2020г.) выдался свободный денёк, и можно плотно заняться сумматором Adder3. И пожалуй придётся начать всё сначала, так как во-первых, у меня образовалась приличная пачка черновиков, в которых уже сам чёрт ногу сломи, и когда я недавно накосяпорил в схеме, то восстановить её по черновикам с налёту не смог. А во-вторых в процессе восстановления пришла мысль, что можно ещё прилично сократить объём используемых логических элементов. И это всё потому, что второе слагаемое у нас константа с точно известным значением каждого бита. Да и заодно можно будет всё детально и тщательно проверить. К томуже, нужно всё же, с черновиков переносить данные в электронный вид, и удобочитаемый, чтобы можно было в любой момент вернуться назад и посмотреть, да и при проверке так будет гораздо удобнее, а точнее по сути, просто возможно. Поэтому переберусь я в пост ниже и там потихоньку начну...

.

Начало разработки.

____Итак, всё что выше, это либо описание теории самой, по крайней мере самого основного, либо просто предварительное обдумывание. Предварительные наброски, для оценки габаритов, различных затрат и т. д. В результате их стало понятно, что делать майнер по классической схеме, когда делается "в железе" одна итерация, и потом данные гоняются через неё, нет смысла. Для этого нужно брать крутейшую микросхему ПЛИС с техпроцессом 7 нм и на ней всё делать и не факт, что будет круче микросхемы выполненной по технологии ASIC. Да и не готов я это реализовать в полной мере на данный момент, задача немного другая.

____А задача состоит в том, чтобы понять всё, что необходимо для реализации майнера в железе, и на данный момент не всё понятно. А так же обойти различные подводные камни и сделать его супер быстрым. А для этого необходимо реализовать, как минимум все 64 итерации в виде схемы с единым потоком данных, не готов пока на пальцах описать, что имею в виду, но по ходу реализации это станет понятно.

____И на данный момент задачу нашу можно разбить на некоторое количество частей. Первая часть и мы ею будем заниматься потом, это получение данных от пула и отправка ему результатов, пока это всё просто в тумане. Вторая задача, это разбиение полученного message и дополнение. Третья задача, это получение дополнительных слов. И четвёртая создание непосредственно 64-x итераций с подсчётом результатов в первых, начальных, итерациях. И реализовывать это всё будем с конца, так сказать от простого к сложному, по крайней мере по тому, что я уже понял. Хотя уверенности что я всё понял правильно нет вообще никакой, так как информации катастрофически мало, проконсультироваться так же практически не с кем, а те разработчики майнеров, с которыми я общался, например майнера z-enemy, в основном занимаются soft майнерами для GPU, и мало предоставляют полезной информации, по крайней мере понятной для меня на данном итапе развития...

____Дальше, ниже, постепенно будет отображаться процесс разработки, от теории, просчёта, и проектирования, вплоть до железа, в качестве которого пока рассматиривается серия микросхем 74ACxxx. Ну и из предварительных раздумий, стало понятно, что только применение SMD компонентов, абсолютно всех, возможно позволит создать относительно компактное устройство.

____Естественно, если кто-то захочет что-то написать, или проконсультироваться или наоборот помочь, что-то подсказать или поправить увидев явные какие-то ошибки, это очень приветствуется...

____Итак, ниже представлена структурная схема одной итерации, немного видоизменённая мной, из учёта правила, что от перемены мест слогаемых сумма не меняется, поэтому мы сначала сможем сложить h+Ki, так же сможем сложить Ch+Cy1, здесь Cy1 это вместо значка суммы от слова carry (почему мне вчера пришло на ум именно carry, а не aderr, это всё потому, что не давала покоя проблема переноса. Так как уже было понятно, что 0-я итерация сведётся к двум квантам времени. В первом будет находиться T1, а во втором A и E. И тут возникает проблема, что даже при применении микросхемы CD74ACT283M у которой время выдачи бита переноса занимает 2,7 нс при самых идеальных условиях. А именно, качественный монтаж, питание +5,5 В и исполнение выдерживающее +125 градусов, а так же выдача результата 3,3 нс. И так как этих микросхем для 32-разрядов требуется 8 шт., то имеем, что задержка в первых семи микросхемах будет 2,7 нс, что в сумме составит 18,9 нс и в последней, восьмой, 3,3 нс. А общая минимальная задержка будет 18,9 + 3,3 = 22,2 нс. Что очень медленно, если учесть, что у нас два кванта времени и общая задержка выполнения 0-й итерации будет 44,4 нс. А поэтому нужен полностью параллельный суматор с параллельным переносом на все 32-разряда, либо применение другой, ещё более быстродействующей логики, что не жалательно, либо скорее всего переход от позиционной арифметики к модулярной системе счисления). И сложить полученные значения между собой. В результате потребуется только один сумматор для сложения полученного результата с словом Wi, чтобы получить Т1.

____Хотя, нужно будет проверить идентичность результата, взять любое случайное число Wi и подсчитать результат по старой схеме и по новой, будет ли он совпадать...

Итак, в виду того, что:

Инициализация переменных

(первые 32 бита дробных частей квадратных корней первых восьми простых чисел [от 2 до 19]):

h0 := 0x6A09E667

h1 := 0xBB67AE85

h2 := 0x3C6EF372

h3 := 0xA54FF53A

h4 := 0x510E527F

h5 := 0x9B05688C

h6 := 0x1F83D9AB

h7 := 0x5BE0CD19

Мы имеем начальные фиксированные значения для слов в первой итерации, пардон, в нулевой итерации...

a := h0

b := h1

c := h2

d := h3

e := h4

f := h5

g := h6

h := h7

Мы не будем это всё реализовывать в железе и тратить на это "железо", деньги и время, время на вычисления, каждый раз...

Cy0 = (a rotr 2) xor (a rotr 13) xor (a rotr 22)

a = 0x6A09E667

(a rotr 2) = 0xDA827999

(a rotr 13) = 0x333B504F

(a rotr 22) = 0x27999DA8

0xDA827999 xor 0x333B504F = 0xE9B929D6

Cy0 = 0xE9B929D6 xor 0x27999DA8 = 0xCE20B47E

Для 0-й итерации:

Maj = (a and b) xor (a and c) xor (b and c)

(a and b) = 0x6A09E667 and 0xBB67AE85 = 0x2A01A605

(a and c) = 0x6A09E667 and 0x3C6EF372 = 0x2808E262

(b and c) = 0xBB67AE85 and 0x3C6EF372 = 0x3866A200

0x2A01A605 xor 0x2808E262 = 0x02094467

Maj = 0x02094467 xor 0x3866A200 = 0x3A6FE667

T2 = Maj + Cy0

T2 = 0x08909AE5

____Прежде чем продолжить дальше, нужно проверить закон:

Закон дистрибутивности. Дистрибутивность конъюнкции и суммы по модулю два.

(a and b) xor (a and c) = a and (b xor c) !!!

____Он позволит нам в каждом блоке Maj избавитя от одной операции and, что сэкономит 8 микросхем. Итак преобразуем формулу:

Maj = (a and b) xor (a and c) xor (b and c), в

Maj = (a and (b xor c)) xor (b and c), и посчитаем, получится ли у нас тот же результат:

Maj = (0x6A09E667 and (0xBB67AE85 xor 0x3C6EF372)) xor (0xBB67AE85 and 0x3C6EF372) =

= (0x6A09E667 and 0x87095DF7) xor 0x3866A200 =

= 0x02094467 xor 0x3866A200 = 0x3A6FE667

Результаты совпали, ура, мы сэкономим огромное количество микросхем, а точнее в 126 итерациях по 8 микросхем, то есть 1008 шт. Ну или кучу логических ячеек, при реализации в ПЛИС. То есть не нужно тратить 4032 логических элемента 2И.

Далее вычисляем:

Cy1 = (e rotr 6) xor (e rotr 11) xor (e rotr 25)

h4 := 0x510E527F

e := h4

(0x510E527F rotr 6) = 0xFD443949

(0x510E527F rotr 11) = 0x4FEA21CA

(0x510E527F rotr 25) = 0x87293FA8

0xFD443949 xor 0x4FEA21CA = 0xB2AE1883

0xB2AE1883 xor 0x87293FA8 = 0x3587272B

Cy1 = 0x3587272B

____Далее вычисляем значение на выходе блока Ch:

Ch = (e and f) xor ((not e) and g)

e = 0x510E527F

f = 0x9B05688C

g = 0x1F83D9AB

(not e) = 0xAEF1AD80

Ch = (0x510E527F and 0x9B05688C) xor (0xAEF1AD80 and 0x1F83D9AB) =

= 0x1104400C xor 0x0E818980 = 0x1F85C98C

Ch = 0x1F85C98C

____Находим сумму Adder4:

Adder4 = Ch + Cy1

Adder4 = 0x1F85C98C + 0x3587272B

Adder4 = 0x550CF0B7

____Находим сумму Adder1:

K0 = 0x428A2F98

Adder1 = h + k0

Adder1 = 0x5BE0CD19 + 0x428A2F98

Adder1 = 0x9E6AFCB1

____Находим сумму Adder2:

Adder2 = Adder1 + Adder4

Adder2 = 0x9E6AFCB1 + 0x550CF0B7

Adder2 = 0xF377ED68

____И в итоге, мы имеем полностью просчитанную нулевую итерацию. Остаётся в ней реализовать три "железных" сумматора, для того, чтобы находить T1, A и E. Естественно все вычисления нужно будет ещё раз проверить, и проверить с произвольным Wi внесённые изменения.

____А вот проблема сумматоров теперь максимально остро стоит, нам нужно очень высокое быстродействие, конечно как крайний вариант, это CD74AC283M в количестве 8 шт. для каждого сумматора с максимально достижимым быстродействием в 22,2 нс. в виду того, что между тетрадами у нас последовательный перенос будет. Но, по хорошему нужно рассмотреть реализацию и применение 32-разрядного сумматора не только с параллельным вводом, но и паралельным переносом, хотя бы по 16 бит, в идеале все 32 бита. Но опять же это сильно увеличивает объём "железа", в общим палка о двух концах. Ладно, будем пока потихоньку двигаться дальше и решать проблемы по мере их поступления...

____Проверил, какой результат выдаёт оригинальная схема, например при Wi = 0x3B217FE2 и преобразованная, результаты совпали T1 = 0x2E996D4A, то есть правило "от перемены мест слагаемых сумма не меняется" действует, блин ещё бы ему не действовать, это же 1 класс школы, но просто хотелось убедиться на практике. В общим замечательно, структурная схема со всеми расчётами приведённая выше верная и можно приступать к "железу", хотя бы в теоретическом плане. Модификаций сумматоров будет несколько, скорее всего. Так как наш Adder3, например, имеет константу на одном из входов, а соответственно можно избавиться от 32 контактов, если делать сумматоры в виде отдельной платки, устанавливаемой на основную. Я думаю вы уже поняли, что я хочу сделать не одну итерацию в виде платки и потом с помощью регистров защёлкивать результат и гнать его на вход, подставляя нужные Ki и Wi, а в виде единого потока данных, с одновременной подачей сразу всех Wi для всех 64 итераций, ну да ладно, это не так важно сейчас, посмотрим, что из этого получится, просто по объёму "железа" выходит очень много, ну и пофиг, будем изголяться...

____Сейчас посидел, немного подумал и выходит, что скорость сумматора на CD74AC283M получается переменной, в зависимости от того, есть переносы или нет. В итоге, при определённых числах на входе, когда все переносы равны нулю, то есть их нет, то результат будет валидным уже через 3,3 нс, и самый идеальный вариант, что и в других двух сумматорах, которые работают параллельно, будет такая же ситуация. Тогда время вычисления 0-й итерации будет 6,6 нс, но это, самое максимальное быстродействие при определённых значениях входных переменных, ну а максимальный-идеальный остаётся прежним 44,4 нс. В общим пока ковыряю параллельный сумматор, с параллельным переносом на отдельных логических элементах, просто возможно получися уменьшить количество "железа" в силу того, что у нас одна из переменных имеет определённое значение, а соответственно внутри сумматора, в случае бита слагаемого равного нулю, элемент XOR превращается в повторитель и таким образом его можно вообще убрать из схемы, задержка становится равной 0 нс, да и потребление 0.

____Ну вот, день прошёл не зря, удалось заменить в первой тетраде микросхему CD74AC283M то есть полный 4-разрядный сумматор, у которого время выдачи результата 3,3 нс, а время выдачи бита переноса 2,7 нс, на схему на логических элементах, ну точнее элементе. Потребовался всего один логический элемент НЕ (not) от микросхемы SN74AC04. А это соответственно снижение потребляемой мощности, конкретно этим участком схемы, а также увеличение быстродействия, теперь бит переноса выдаётся за 0 нс, а результат за 1 нс.

____Удалось это сделать конечно только благодаря тому, что одно из слагаемых является константой у нас это число 0x8 (1000), Ну а второе естественно может иметь 16 значений от 0000 до 1111.

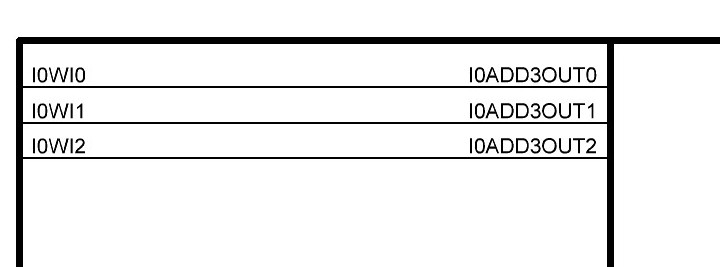

____В результате разработки сумматора для следующей тетрады, для битов от I0WI4...I0WI7 задержка распространения, минимально достижимая, вышла 3 нс, а вот количество элементов больше 1...2 корпусов микросхем. Поэтому решил, что проще поставить обычный сумматор, в идеале CD74ACT283 но его нужно будет искать в исполнении на 125 градусов и питать напряжением +5,5 В. Так как в datasheet именно при этих двух параметрах можно получить максимальное быстродействие, то есть минимальные задержки, а именно выдача результата через 3,3 нс и бита переноса через 2,7 нс. В нашем же случае, мы для получения результата будем использовать сумматор, а бит переноса получать не за 2,7 нс взяв его с самой микросхемы, а получать его отдельно при помощи двух логических элементов ИЛИ (or) и И (and), что даёт нам время задержки 2 нс. Таким образом по 8 битам мы имеем, время выдачи результата, через 3,3 нс, а не 6 нс и бит переноса С2 через 2 нс, а не через 5,4 нс.

____Хе хе, а вот и не правильно, я забыл просчитать, если бит переноса из первой тетрады равен 1, то схема уже не пашет на этих двух лог. элементах. Так что во второй тетраде полностью будет задействована микросхема сумматора, и время задержек - результат через 3,3 нс, бит переноса С2 через 2,7 нс.

____Да, медленно. Выход только один, параллельный сумматор, с параллельным переносом на все 32 бита. Тут проще взять формулу в базисе логического элемента И-НЕ (nand) и преобразовать в соответствии с быстродействием конкретных микросхем, например та же ЛА3 от TI имеет минимально достижимую задержку 1,5 нс, в то время как ЛА4 - 1 нс, если судить по datasheet, да меньше на один логический элемент, но тут уже и 1 нс кажется огромной задержкой... В общим, нужно начинать просчитывать полностью с параллельным переносом сумматор. Вся проблема, что больше 8 входов как вроде нет ЛА2 а нужно и с 32 входами И-НЕ элемент, а это только при помощи наращивания и дополнительные ступени, опять же дополнительные 1...2 нс. Но, всё равно выигрыш, пусть даже 3 ступени, и каждая по 1 нс, то это 3 нс, 1 нс в сумматоре, всего 4 нс, против 22,2 нс, в общим... Нужно мучить формулу, чертить схему, с учётом что оба операнда не константы, и будет точно уже потом ясно, где константы, там понятно, всё проще и компактнее...

Где бы ещё время взять, работа, ремонт, пустой холодильник, да и спать иногда желательно...

Ладно, фигня это всё, есть над чем поработать, поразмыслить, что поковырять, больше беспокоит, не приведёт ли ёмкость и индуктивность монтажа, паразитные наводки и весь остальной гемор, к тому, что будет всё с параметрами не min, и даже не typ, а max и тогда это печально, так как это даже не уровень К531 серии будет, у которой в среднем 5...7 нс. Но думаю, коли уж К531 серия в середине 70-х позволяла 5...7 нс, то уж 74ACxxx с SMD монтажом и корпусами, да и платы покачественнее на пару порядков, должны справиться... Слишком много неизвестных...

Ладно, это так, мысли в слух, поживём посмотрим, как оно пойдёт дальше, впереди слишком много ещё работы...

Итак, делаем параллельный сумматор с параллельным переносом для Adder3 первые 4 бита у нас готовы, следующий бит I0ADD3OUT4 требует одного элемента "исключающее ИЛИ" (XOR), на один вход подаётся четвёртый бит слова, а на второй третий бит слова, так как формула переноса полностью коллапсирует до повторителя для P3 (Пэ три):

P3 = / /ai . bi . /ai-1 . bi-1 . hi-1 . /ai-2 . bi-2 . hi-1 . hi . /ai-3 . bi-3 . hi-2 . hi-1 . hi . /p . h0 . h1 . h2 . h3

Как видим /ai . bi

это для P3

/a3 . b3

а b3 = 1 соответственно наш логический элемент 2И-НЕ имеет на одном из входов константу равную всегда лог.1 и соответственно элемент становится просто инвертором. Во всех остальных частях формулы у нас присутствуют p, b0, b1, b2 которые так же константы и равны лог. 0 из-за чего каждый из этих элементов всегда на выходе имеет константу равную лог. 1, соответственно общая инверсия, то есть по сути это логический элемент 5И-НЕ, становится инвертором для /a3 . b3 и поэтому нет смысла пропускать сигнал a3 через два последовательно включённых инвертора, поэтому он у нас приходит на прямую на сумматор, который так же упрощается до одного логического элемента XOR...

Процесс потихоньку идёт, просчитал 8 бит, получилось компактненько, 4 корпуса микросхем и то есть ещё 5 свободных логических элемента и задержка пока что составляет 3 нс, естественно минимально достижимая при различных условиях, оговоренных выше, т. е. питание 5,5 В, и т. д. Продолжу просчитывать дальше на днях по мере появления свободного времени.

Итак, сегодня (18.06.2020г.) выдался свободный денёк, и можно плотно заняться сумматором Adder3. И пожалуй придётся начать всё сначала, так как во-первых, у меня образовалась приличная пачка черновиков, в которых уже сам чёрт ногу сломи, и когда я недавно накосяпорил в схеме, то восстановить её по черновикам с налёту не смог. А во-вторых в процессе восстановления пришла мысль, что можно ещё прилично сократить объём используемых логических элементов. И это всё потому, что второе слагаемое у нас константа с точно известным значением каждого бита. Да и заодно можно будет всё детально и тщательно проверить. К томуже, нужно всё же, с черновиков переносить данные в электронный вид, и удобочитаемый, чтобы можно было в любой момент вернуться назад и посмотреть, да и при проверке так будет гораздо удобнее, а точнее по сути, просто возможно. Поэтому переберусь я в пост ниже и там потихоньку начну...

.

Последний раз редактировалось: Viktor2312 (Чт Июн 18 2020, 09:12), всего редактировалось 40 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

7

.

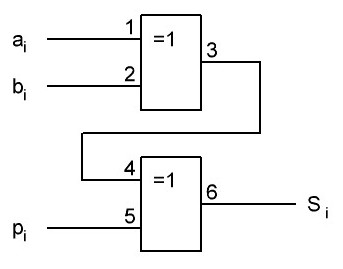

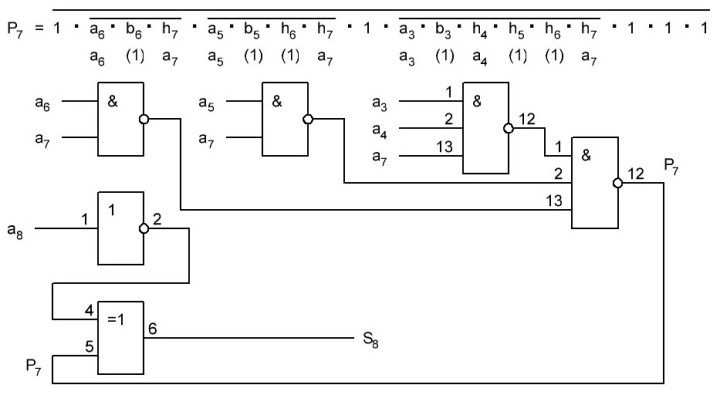

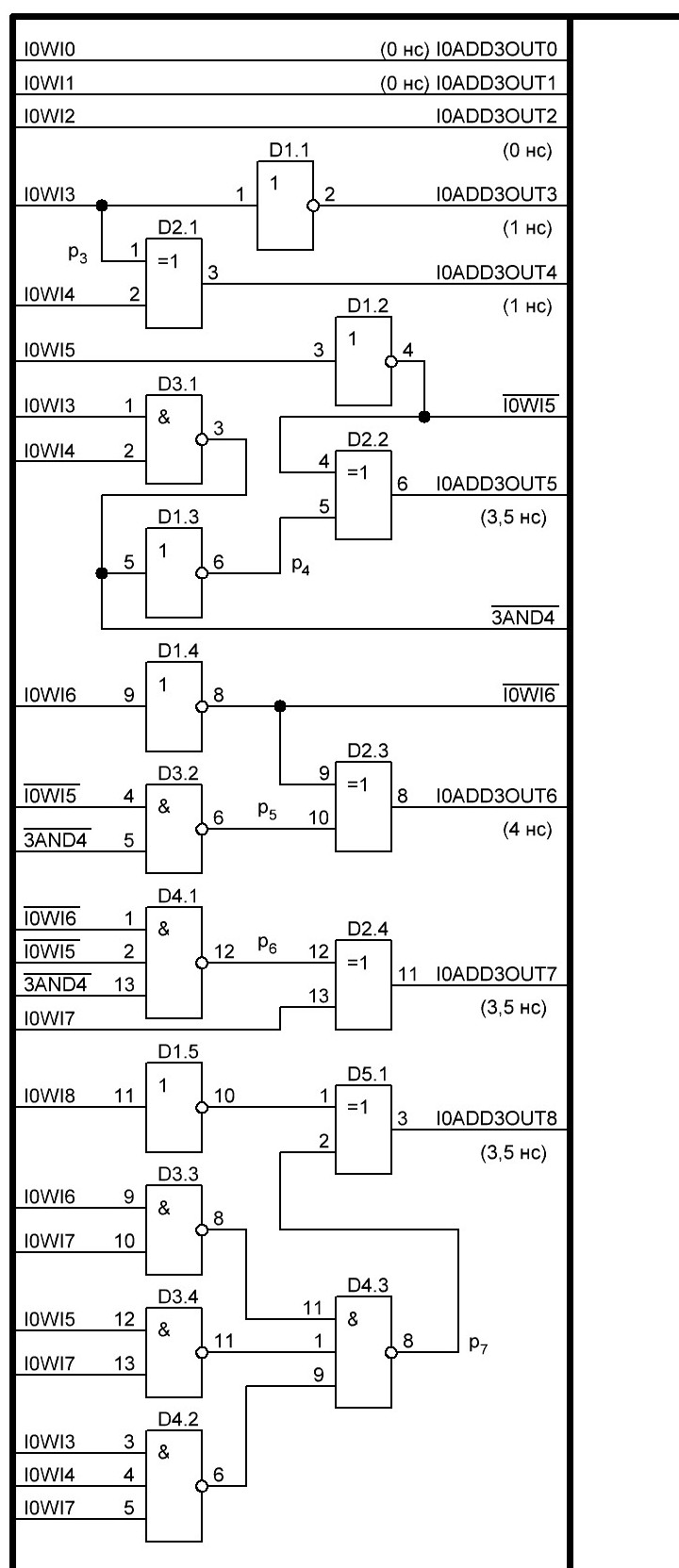

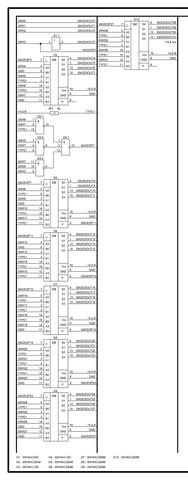

Поехали...

Итак, мы имеем сумматор, который имеет два 32-разрядных входа и один 32-разрядный выход. Первое слагаемое a, это переменная, а точнее слово w[0]. Второе слагаемое b, это константа с точно известным значением, а именно 0хF377ED68. А соответственно по сути у нас получается преобразователь данных, есть вход, на который подаётся переменная a и есть вход, на котором получается значение T1. Для начала запишем наше число в двоичной форме, пожалуй это будет лучше сделать в графическом виде, я для этого использую программу Splan в которой я черчу схемы и вообще всё, что угодно, так как более простой в освоении программы, мне потребовался 1 час, чтобы разобраться в ней, и удобной в использовании, я ещё не встречал. Ну а потом просто конвертирую в .bmp формат, для этого в ней имеется кнопочка, пойду почерчу...

Готово, загрузим, а нет не загрузим, у нас как всегда ipic.su не доступен Error 521 Web server is down, как же это за..бало, но мы пойдём другим путём...

Все нервы измотали, но как вроде нашёл, куда грузится и работает vfl.ru

Итак, хух, на рисунке выше наше входное слово b, теперь оно представлено наглядно и всегда можно посмотреть какой бит чему равен. Для нас максимально выгодно, чтобы в нём, да и в любом другом было как можно больше нулей, это кардинально сокращает количество "железа", но что имеем, то имеем, с этим и будем работать. Так же нам здесь очень везёт, что входной бит переноса из младшего разряда p не используется и по сути всегда равен нулю, это вообще отрезает огромный кусок схемы и не только тут, но и в дальнейшем, где оба слагаемых будут переменными. Далее представим нашу формулу, опять чертить...

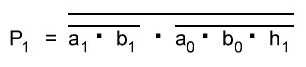

Как видим в последней части формулы у нас присутствует бит переноса из младшего разряда p, а он у нас всегда равен нулю, соответственно присутствуя на входе логического элемента И-НЕ он создаёт условие, что у нас на выходе этого логического элемента всегда будет лог. 1 и таким образом, нет смысла реализовывать данный логический элемент в "железе", достаточно просто подать лог. 1 на вход следующего элемента И-НЕ, но и это не нужно делать, так как лог. 1 на многовходовом логическом элементе И-НЕ, если она константа и всегда равна лог. 1, просто убирает данный вход. Например, если у нас логический элемент 4И-НЕ и на один из входов постоянно подаётся лог. 1, то он просто превращается в логический элемент 3И-НЕ. Таким образом последняя часть формулы отпадает во всех случаях, вне зависимости от того, обе переменные у нас на входе сумматора или одна из них равна константе, так как входной бит переноса из младшего разряда у нас всегда равен лог.0. Далее перейдём к реализации, а точнее проверки 0-го бита нашего сумматора. Итак, мы имеем вход a значение которого мы не знаем и вход b значение которого мы знаем. Так как мы расчитываем 0-й бит, то и входные слагаемые у нас a0 и b0, входной бит переноса равен нулю. Для этого нам нужно вычертить схему одного разряда сумматора, и она будет идентичная для всех разрядов, и самое главное, что в ней нам не требуется реализовывать выходной бит переноса, так как у нас параллельный сумматор с параллельным переносом, пойду почерчу, не я конечно пойду кофе пить и курить, а потом...