Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Spartan-6 (XC6SLX9-2TQG144C)

Страница 1 из 1 • Поделиться

Spartan-6 (XC6SLX9-2TQG144C)

Spartan-6 (XC6SLX9-2TQG144C)

1

Микросхема ПЛИС, FPGA (XC6SLX9-2TQG144C) фирмы Xilinx, семейства Spartan-6.

Микросхема ПЛИС (XC6SLX9-2TQG144C), с архитектурой FPGA, семейства Spartan-6 предназначена, прежде всего, для всестороннего использования в составе серийно выпускаемой аппаратуры различного назначения. В частности, данную микросхему можно использовать для реализации контроллеров высокоскоростных интерфейсов, высокопроизводительных устройств цифровой обработки сигналов (ЦОС), встраиваемых микропроцессорных систем, выполняемых на базе конфигурируемых 32-разрядных ядер семейства MicroBlaze, устройств автомобильной электроники, систем видеонаблюдения и многих других. Оптимальное соотношение стоимости и функциональных возможностей данной микросхемы позволяет применять её в качестве эффективной замены специализированных интегральных схем ASIC.

Здесь, мы постараемся рассмотреть особенности архитектуры, микросхемы (XC6SLX9-2TQG144C), основные её характеристики, способы применения, программирования и создания проектов на её основе.

Микросхема (XC6SLX9-2TQG144C) выполнена по КМОП-технологии 45 нм с девятью слоями металлизации. Архитектура данной микросхемы ПЛИС отличается от микросхем предыдущего поколения серии Spartan, выпускавшихся ранее, использованием логических и специализированных ресурсов применявшихся в более совершенных семействах Virtex предыдущего поколения. То есть она вобрала в себя многие наработки применявшиеся в сериях Virtex-5 LX, Virtex-5 LXT, Virtex-5 SXT, Virtex-5 FXT, Virtex-5 TXT и Virtex-6 LXT, Virtex-6 SXT.

Микросхема (XC6SLX9-2TQG144C) характеризуется следующими особенностями:

* Практически двукратное снижение уровня общей потребляемой мощности по сравнению с кристаллами предыдущего поколения серии Spartan за счет внедрения новых технологических решений, включающих в себя, в частности, использование новых транзисторов различных типов, сокращение их размеров, применение диэлектрика с низким значением диэлектрической постоянной (Low-K), снижение напряжения питания ядра кристалла до 1,2 В, а также поддержки энергосберегающих режимов работы.

* Использование в составе архитектуры кристалла конфигурируемых логических блоков (Configurable Logic Block, CLB) нового поколения, выполненных на основе реальных 6-входовых таблиц преобразования Look-Up Table (LUT) с применением дополнительных триггеров, позволяющих реализовать функции большого числа переменных без применения дополнительных логических ресурсов и существенно расширить возможности реализации конвейерной организации обработки данных в проектируемых устройствах, и тем самым добиться повышения производительности разрабатываемых систем.

* Новая инфраструктура распределения тактовых сигналов, обеспечивающая минимизацию задержек и расхождения фронтов тактовых сигналов, возникающих при распространении этих сигналов внутри кристалла.

* Внедрение блоков управления синхронизацией Clock Management Tile (CMT), сочетающих в себе преимущества цифровых модулей Digital Clock Manager (DCM) и аналоговых модулей фазовой автоподстройки частоты Phase-Locked-Loop (PLL). Микросхема содержит два блока управления синхронизацией Clock Management Tiles (CMT), четыре модуля управления синхронизацией Digital Clock Manager (DCM) и два аналоговых модуля фазовой автоподстройки частоты Phase-Locked-Loop (PLL).

И многими другими, которые мы постепенно рассмотрим в процессе изучения данной микросхемы ПЛИС.

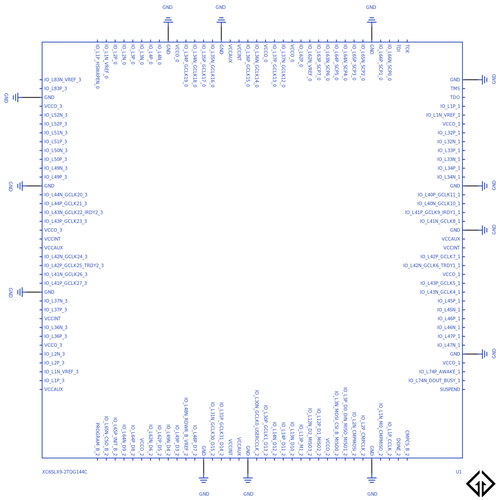

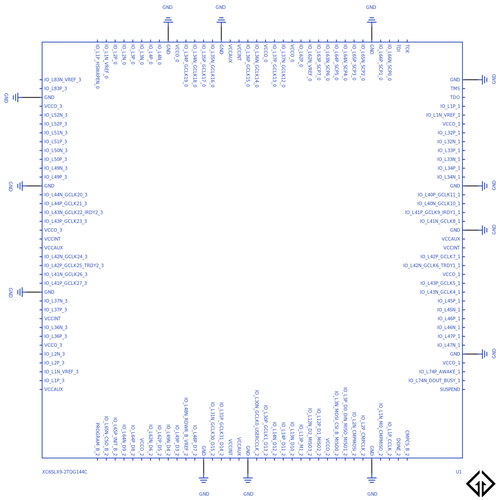

Расположение выводов и их названия у микросхемы ПЛИС (XC6SLX9-2TQG144C):

Spartan_XC6SLX9-2TQG144C

Микросхема ПЛИС (XC6SLX9-2TQG144C), с архитектурой FPGA, семейства Spartan-6 предназначена, прежде всего, для всестороннего использования в составе серийно выпускаемой аппаратуры различного назначения. В частности, данную микросхему можно использовать для реализации контроллеров высокоскоростных интерфейсов, высокопроизводительных устройств цифровой обработки сигналов (ЦОС), встраиваемых микропроцессорных систем, выполняемых на базе конфигурируемых 32-разрядных ядер семейства MicroBlaze, устройств автомобильной электроники, систем видеонаблюдения и многих других. Оптимальное соотношение стоимости и функциональных возможностей данной микросхемы позволяет применять её в качестве эффективной замены специализированных интегральных схем ASIC.

Здесь, мы постараемся рассмотреть особенности архитектуры, микросхемы (XC6SLX9-2TQG144C), основные её характеристики, способы применения, программирования и создания проектов на её основе.

Общая характеристика и особенности.

Микросхема (XC6SLX9-2TQG144C) выполнена по КМОП-технологии 45 нм с девятью слоями металлизации. Архитектура данной микросхемы ПЛИС отличается от микросхем предыдущего поколения серии Spartan, выпускавшихся ранее, использованием логических и специализированных ресурсов применявшихся в более совершенных семействах Virtex предыдущего поколения. То есть она вобрала в себя многие наработки применявшиеся в сериях Virtex-5 LX, Virtex-5 LXT, Virtex-5 SXT, Virtex-5 FXT, Virtex-5 TXT и Virtex-6 LXT, Virtex-6 SXT.

Микросхема (XC6SLX9-2TQG144C) характеризуется следующими особенностями:

* Практически двукратное снижение уровня общей потребляемой мощности по сравнению с кристаллами предыдущего поколения серии Spartan за счет внедрения новых технологических решений, включающих в себя, в частности, использование новых транзисторов различных типов, сокращение их размеров, применение диэлектрика с низким значением диэлектрической постоянной (Low-K), снижение напряжения питания ядра кристалла до 1,2 В, а также поддержки энергосберегающих режимов работы.

* Использование в составе архитектуры кристалла конфигурируемых логических блоков (Configurable Logic Block, CLB) нового поколения, выполненных на основе реальных 6-входовых таблиц преобразования Look-Up Table (LUT) с применением дополнительных триггеров, позволяющих реализовать функции большого числа переменных без применения дополнительных логических ресурсов и существенно расширить возможности реализации конвейерной организации обработки данных в проектируемых устройствах, и тем самым добиться повышения производительности разрабатываемых систем.

* Новая инфраструктура распределения тактовых сигналов, обеспечивающая минимизацию задержек и расхождения фронтов тактовых сигналов, возникающих при распространении этих сигналов внутри кристалла.

* Внедрение блоков управления синхронизацией Clock Management Tile (CMT), сочетающих в себе преимущества цифровых модулей Digital Clock Manager (DCM) и аналоговых модулей фазовой автоподстройки частоты Phase-Locked-Loop (PLL). Микросхема содержит два блока управления синхронизацией Clock Management Tiles (CMT), четыре модуля управления синхронизацией Digital Clock Manager (DCM) и два аналоговых модуля фазовой автоподстройки частоты Phase-Locked-Loop (PLL).

И многими другими, которые мы постепенно рассмотрим в процессе изучения данной микросхемы ПЛИС.

Расположение выводов и их названия у микросхемы ПЛИС (XC6SLX9-2TQG144C):

Spartan_XC6SLX9-2TQG144C

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Spartan-6 (XC6SLX9-2TQG144C)

Re: Spartan-6 (XC6SLX9-2TQG144C)

2

.

____Архитектура конфигурируемых логических блоков CLB, применяемых в составе микросхем ПЛИС семейств Spartan-6 LX и Spartan-6 LXT, принципиально отличается от структуры логических ресурсов, используемых в кристаллах семейств предыдущего поколения.

____В новых семействах, в том числе и в Spartan-6, в очередной раз изменена сама структура логической ячейки: вместо конфигурации «LUT6 + триггер» (которая впервые появилась в Virtex-5) введена конфигурация «LUT6 + 2 триггера».

____Структурно, любую микросхему FPGA можно представить совокупностью блоков, содержащих логику переключателей, осуществляющих коммутацию этих блоков и макроблоков, представляющих собой некоторые законченные элементы, жёстко реализованные в FPGA на физическом уровне. При этом, самые большие блоки, содержащие логику, называются CLB (Configurable Logical Block).

____CLB — это своеобразная «молекула» в FPGA, состоящая из «атомов»-ячеек (logic cells). Возможности самих ячеек, несомненно, являются весьма важными для достижения высоких показателей проекта, однако дополнительные ресурсы, служащие для объединения ячеек в конфигурируемый логический блок, также могут привнести полезные свойства.

____Каждый CLB подключён к трассировочной матрице, а также имеет цепь переноса от соседнего CLB. Любой CLB содержит 2 меньших блока, называемых Slice. Вместе с тем оба типа секций

располагаются в рамках каждого CLB, то есть секции, способные реализовать память и сдвиговые регистры, равномерно распределяются по всей матрице CLB. В Spartan-6 появился третий тип — SliceX. Что интересно, это менее мощная разновидность секции, поскольку в ней отсутствует цепь ускоренного переноса, то есть она не может служить для организации сложения или вычитания.

____Таким образом существует, 3 вида Slice:

____Виды Slice различаются по предоставляемым возможностям и ресурсам. CLB может содержать один SliceX и один SliceM или SliceL. Символы M и L означают Memory и Logic соответственно, то есть ряд ячеек может реализовывать функцию памяти, а остальные — только логику). Исключением является кристалл XC6SLX4, в котором отсутствуют секции типа SliceL.

____Из двух CLB один содержит пару секций SliceL + SliceX, а другой — SliceM + SliceX.

Блоки, соответственно, называются CLB_LX и CLB_MX.

____Такое нововведение следует трактовать как формальное ухудшение функциональности. С другой стороны, можно указать и на позитивные факторы — упрощение ячеек, а следовательно, повышение производительности и уменьшение стоимости. В практических проектах можно рассчитывать на то, что цепи ускоренного переноса будут требоваться не в 100% цифровых узлов, так что САПР будет иметь возможность поместить имеющиеся в проекте арифметические блоки в те секции, где имеются цепи ускоренного переноса.

____В микросхемах ПЛИС предшествующего поколения серии Spartan использовались секции, построенные на базе 4-входовых таблиц преобразования, каждая из которых сопряжена с одним триггером. В кристаллах семейств Spartan-6 LX и Spartan-6 LXT основу секций всех типов образуют четыре реальные 6-входовые таблицы преобразования LUT и восемь триггеров, подключенных попарно к выходам таблиц преобразования. Таким образом, архитектура секций, образующих конфигурируемые логические блоки кристаллов серии Spartan-6, в значительной степени подобна структуре секций, применяемых в микросхемах ПЛИС новых семейств Virtex-6 LXT и Virtex-6 SXT.

____Как и в кристаллах этих семейств, 6-входовые таблицы преобразования LUT в микросхемах ПЛИС Spartan-6 LX и Spartan-6 LXT могут конфигурироваться в виде двойных 5-входовых функциональных генераторов с общими входами и раздельными выходами.

____На рисунке ниже представлена принципиальная структура FPGA Spartan-6.

____Рассмотрим теперь кратко принципиальную структуру и типы Slice.

____На упрощённом рисунке ниже, представлена архитектура ячеек Slice всех типов для FPGA Spartan-6.

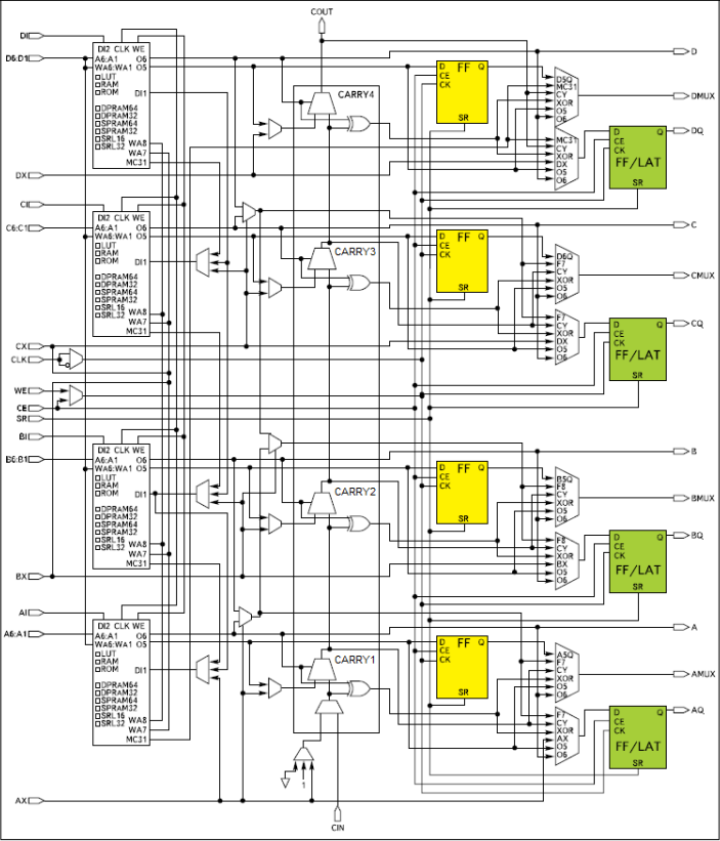

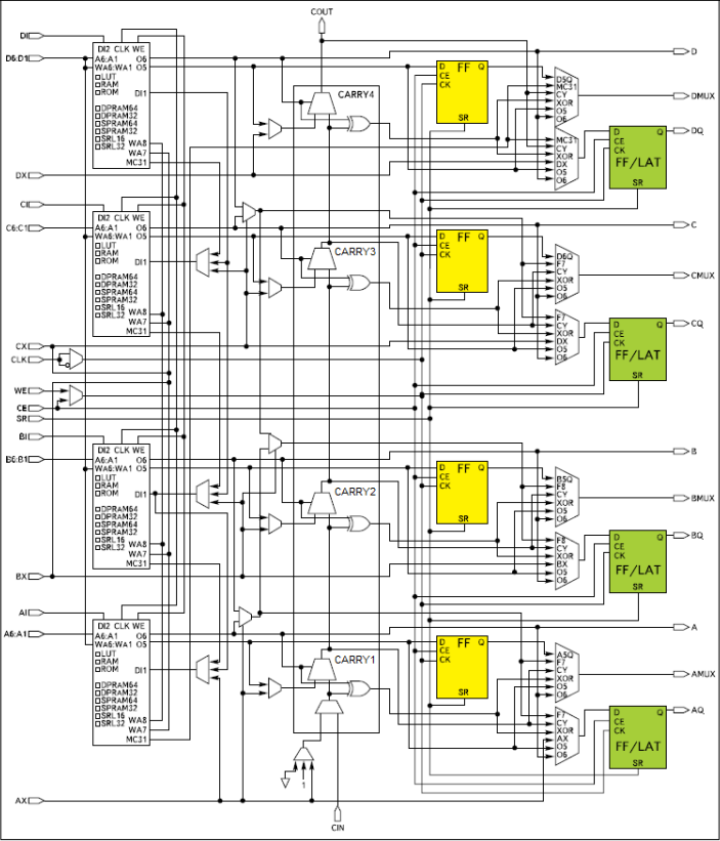

____Подробная функциональная схема секции SliceX конфигурируемых логических блоков

CLB ПЛИС серии Spartan-6 показана на рисунке ниже:

SliceX

____В отличие от секций типа SliceX, в состав секций SliceL дополнительно входит логика ускоренного переноса и мультиплексоры, предназначенные для расширения функциональных возможностей конфигурируемых логических блоков CLB. Эти мультиплексоры применяются для увеличения числа булевых переменных в выполняемых функциях. Детализированная функциональная схема секции SliceL, применяемой в составе конфигурируемых логических блоков CLB кристаллов семейств Spartan-6 LX и Spartan-6 LXT, изображена на рисунке ниже:

SliceL

____В секциях типа SliceM, кроме логики ускоренного переноса и мультиплексоров расширения количества аргументов выполняемых функций, применяются таблицы преобразования, которые могут конфигурироваться как элементы 64-разрядной распределенной памяти или как сдвиговые регистры различной разрядности (до 32 разрядов). Полная функциональная схема секций данного типа представлена на рисунке ниже:

SliceM

____В состав конфигурируемых логических блоков CLB микросхем ПЛИС серии Spartan-6 входят попарно секции типов SliceX и SliceL или SliceX и SliceM. Таким образом, в кристаллах семейств Spartan-6 LX и Spartan-6 LXT 50% логических ресурсов составляют секции типа SliceX и по 25% — секции типов SliceL и SliceM.

____Из восьми триггеров, входящих в состав секций всех типов, четыре элемента могут

конфигурироваться как триггеры с динамическим управлением (D-триггеры, flip-flop) или потенциальным управлением (триггеры защелки, latch). Условные графические образы этих триггеров на рисунках выше имеют обозначения FF/LAT. Остальные четыре триггера, обозначенные как FF, могут применяться в реализуемых устройствах только как триггеры с динамическим управлением т. е. триггеров, переключающихся по уровню тактового сигнала. Не смотря на это Xilinx настоятельно не рекомендует использовать latch в проектах для FPGA и применять технику полностью синхронного проекта. Также следует упомянуть, что все триггеры тактируются по переднему фронту тактового сигнала. Кроме этого, в рамках любого проекта можно задать любым триггерам значение по умолчанию.

____Любой Slice содержит в своем составе 6-ти входовые LUT. 6-ти входовые LUT могут реализовать любую булеву функцию 6-ти переменных. Мультиплексоры-расширители MUX позволяют объединять выходы таблиц LUT для получения функций 7 и 8 переменных. Это осуществляется объединением нескольких LUT для построения более сложных логических функций.

.

Структура логической ячейки FPGA.

____Архитектура конфигурируемых логических блоков CLB, применяемых в составе микросхем ПЛИС семейств Spartan-6 LX и Spartan-6 LXT, принципиально отличается от структуры логических ресурсов, используемых в кристаллах семейств предыдущего поколения.

____В новых семействах, в том числе и в Spartan-6, в очередной раз изменена сама структура логической ячейки: вместо конфигурации «LUT6 + триггер» (которая впервые появилась в Virtex-5) введена конфигурация «LUT6 + 2 триггера».

____Структурно, любую микросхему FPGA можно представить совокупностью блоков, содержащих логику переключателей, осуществляющих коммутацию этих блоков и макроблоков, представляющих собой некоторые законченные элементы, жёстко реализованные в FPGA на физическом уровне. При этом, самые большие блоки, содержащие логику, называются CLB (Configurable Logical Block).

____CLB — это своеобразная «молекула» в FPGA, состоящая из «атомов»-ячеек (logic cells). Возможности самих ячеек, несомненно, являются весьма важными для достижения высоких показателей проекта, однако дополнительные ресурсы, служащие для объединения ячеек в конфигурируемый логический блок, также могут привнести полезные свойства.

____Каждый CLB подключён к трассировочной матрице, а также имеет цепь переноса от соседнего CLB. Любой CLB содержит 2 меньших блока, называемых Slice. Вместе с тем оба типа секций

располагаются в рамках каждого CLB, то есть секции, способные реализовать память и сдвиговые регистры, равномерно распределяются по всей матрице CLB. В Spartan-6 появился третий тип — SliceX. Что интересно, это менее мощная разновидность секции, поскольку в ней отсутствует цепь ускоренного переноса, то есть она не может служить для организации сложения или вычитания.

____Таким образом существует, 3 вида Slice:

- SliceX;

- SliceM;

- SliceL.

____Виды Slice различаются по предоставляемым возможностям и ресурсам. CLB может содержать один SliceX и один SliceM или SliceL. Символы M и L означают Memory и Logic соответственно, то есть ряд ячеек может реализовывать функцию памяти, а остальные — только логику). Исключением является кристалл XC6SLX4, в котором отсутствуют секции типа SliceL.

____Из двух CLB один содержит пару секций SliceL + SliceX, а другой — SliceM + SliceX.

Блоки, соответственно, называются CLB_LX и CLB_MX.

____Такое нововведение следует трактовать как формальное ухудшение функциональности. С другой стороны, можно указать и на позитивные факторы — упрощение ячеек, а следовательно, повышение производительности и уменьшение стоимости. В практических проектах можно рассчитывать на то, что цепи ускоренного переноса будут требоваться не в 100% цифровых узлов, так что САПР будет иметь возможность поместить имеющиеся в проекте арифметические блоки в те секции, где имеются цепи ускоренного переноса.

____В микросхемах ПЛИС предшествующего поколения серии Spartan использовались секции, построенные на базе 4-входовых таблиц преобразования, каждая из которых сопряжена с одним триггером. В кристаллах семейств Spartan-6 LX и Spartan-6 LXT основу секций всех типов образуют четыре реальные 6-входовые таблицы преобразования LUT и восемь триггеров, подключенных попарно к выходам таблиц преобразования. Таким образом, архитектура секций, образующих конфигурируемые логические блоки кристаллов серии Spartan-6, в значительной степени подобна структуре секций, применяемых в микросхемах ПЛИС новых семейств Virtex-6 LXT и Virtex-6 SXT.

____Как и в кристаллах этих семейств, 6-входовые таблицы преобразования LUT в микросхемах ПЛИС Spartan-6 LX и Spartan-6 LXT могут конфигурироваться в виде двойных 5-входовых функциональных генераторов с общими входами и раздельными выходами.

____На рисунке ниже представлена принципиальная структура FPGA Spartan-6.

____Рассмотрим теперь кратко принципиальную структуру и типы Slice.

- SliceM - универсальная секция с LUT, конфигурируемыми во всех режимах, а также линиями ускоренного переноса. Содержит 4 таблицы преобразования LUT-6, каждая из которых имеет 6 входов и может использоваться для реализации логических функций, реализации сдвиговых регистров или реализации блока распределенной памяти (distributed RAM), ёмкостью 64 бит. Также этот блок содержит цепи быстрого переноса, расширяемые мультиплексоры и 8 регистров для хранения результата;

- SliceL - LUT конфигурируется только как логический генератор, есть цепи ускоренного переноса. Содержит те же ресурсы, что и SliceM, за исключением сдвиговых регистров и блоков распределенной памяти;

- SliceX - LUT конфигурируется только как логический генератор, нет цепей ускоренного переноса. Содержит исключительно ресурсы для реализации логических функций, что уменьшает логическую нагрузку на ячейку, и приводит к уменьшению числа цепей трассировки, а также к уменьшению времени распространения сигнала. То есть не может служить для организации сложения или вычитания.

____На упрощённом рисунке ниже, представлена архитектура ячеек Slice всех типов для FPGA Spartan-6.

____Подробная функциональная схема секции SliceX конфигурируемых логических блоков

CLB ПЛИС серии Spartan-6 показана на рисунке ниже:

SliceX

____В отличие от секций типа SliceX, в состав секций SliceL дополнительно входит логика ускоренного переноса и мультиплексоры, предназначенные для расширения функциональных возможностей конфигурируемых логических блоков CLB. Эти мультиплексоры применяются для увеличения числа булевых переменных в выполняемых функциях. Детализированная функциональная схема секции SliceL, применяемой в составе конфигурируемых логических блоков CLB кристаллов семейств Spartan-6 LX и Spartan-6 LXT, изображена на рисунке ниже:

SliceL

____В секциях типа SliceM, кроме логики ускоренного переноса и мультиплексоров расширения количества аргументов выполняемых функций, применяются таблицы преобразования, которые могут конфигурироваться как элементы 64-разрядной распределенной памяти или как сдвиговые регистры различной разрядности (до 32 разрядов). Полная функциональная схема секций данного типа представлена на рисунке ниже:

SliceM

____В состав конфигурируемых логических блоков CLB микросхем ПЛИС серии Spartan-6 входят попарно секции типов SliceX и SliceL или SliceX и SliceM. Таким образом, в кристаллах семейств Spartan-6 LX и Spartan-6 LXT 50% логических ресурсов составляют секции типа SliceX и по 25% — секции типов SliceL и SliceM.

____Из восьми триггеров, входящих в состав секций всех типов, четыре элемента могут

конфигурироваться как триггеры с динамическим управлением (D-триггеры, flip-flop) или потенциальным управлением (триггеры защелки, latch). Условные графические образы этих триггеров на рисунках выше имеют обозначения FF/LAT. Остальные четыре триггера, обозначенные как FF, могут применяться в реализуемых устройствах только как триггеры с динамическим управлением т. е. триггеров, переключающихся по уровню тактового сигнала. Не смотря на это Xilinx настоятельно не рекомендует использовать latch в проектах для FPGA и применять технику полностью синхронного проекта. Также следует упомянуть, что все триггеры тактируются по переднему фронту тактового сигнала. Кроме этого, в рамках любого проекта можно задать любым триггерам значение по умолчанию.

____Любой Slice содержит в своем составе 6-ти входовые LUT. 6-ти входовые LUT могут реализовать любую булеву функцию 6-ти переменных. Мультиплексоры-расширители MUX позволяют объединять выходы таблиц LUT для получения функций 7 и 8 переменных. Это осуществляется объединением нескольких LUT для построения более сложных логических функций.

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» Микросхемы ПЛИС семейства Spartan-3

» Микросхемы ПЛИС семейства Spartan-3A

» Микросхемы ПЛИС семейства Spartan-7 28нм

» Микросхемы ПЛИС семейства Spartan-6 45нм

» Изучаем ПЛИС с нуля. /Spartan-3A/VHDL/ISE 14.7/

» Микросхемы ПЛИС семейства Spartan-3A

» Микросхемы ПЛИС семейства Spartan-7 28нм

» Микросхемы ПЛИС семейства Spartan-6 45нм

» Изучаем ПЛИС с нуля. /Spartan-3A/VHDL/ISE 14.7/

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|