Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Основы языка VHDL

RUЭВМ :: ПЛИС, CPLD, FPGA, VHDL, Verilog. COWIN, AMD/Xilinx, Intel/Altera :: Язык описания аппаратуры VHDL

Страница 1 из 1 • Поделиться

Основы языка VHDL

Основы языка VHDL

1

Так как после долгих мытарств сформировалось более менее понятная картина, того, что изучать и в какой последовательности и появилась эта тема.

Основной первый этап в освоении ПЛИС (xilinx) и языка VHDL, это основы языка VHDL. Тут будет такой, своего рода, небольшой конспект с основными выдержками из различной литературы, чтобы отсеять всё лишнее и оставить саму суть. Которую и нужно понять и сохранить в своих мозгах. Если что-то будет повторяться, ничего страшного, "Повторение мать учения" (С).

Опущу часть касающуюся, когда появился и где, данный язык описания аппаратуры, так как это можно прочитать в предисловии любой книги по VHDL имеющейся на русском языке, у нас другая задача, освоить основы данного языка, что я и буду делать.

Цифровая система может быть описана на уровне поведения посредством описания функций, реализуемых системой, и на структурном уровне.

Пока понятно, где-то на подсознательном уровне, описание на структурном уровне, то есть систему можно описать в виде подробного описания всех блоков из которых состоит данная система, а описание на уровне поведения, это когда мы описываем, что будет на выходе системы в зависимости от информации на входе, не вдаваясь в подробности её внутреннего устройства, мне это так видится.

А вот и более точные определения этих двух методов описания цифровой системы:

Как вроде всё мы правильно поняли, будем дальше разбираться...

Что же у нас пишут дальше в умной книжке:

Цифровая система может быть сложной, как, например, микропроцессор или весьма простой, как логическая схема, состоящая из логических элементов (вентилей).

Чтож вполне логично, если мы делаем Микро-ЭВМ, хотя бы с одним микропроцессором, то система у нас будет довольно таки сложной, а если мы хотим просто помигать двумя или одним светодиодом, то относительно простой.

Далее пишут:

Естественно, некоторые компоненты системы в структурном описании могут состоять из нескольких частей - компонент более низкого уровня иерархии описания. Представляя отношение вхождения подсхем в схемы в виде графа, можно получить дерево (граф) иерархии описания всей системы.

Вот жеж любят всё усложнять, ну первое предложение, как бы сразу понятно, зачем второе предложение так замудрённо писать, ну да ладно авторам виднее, а нам главное понять. Смысл до меня дошёл следующий, когда мы описываем на структурном уровне нашу системы, представив её в виде чёрного ящика с определённым количеством входов и выходов, мы должны понимать или допетривать, хрен знает как правильнее написать, что этот чёрный ящик наш может состоять из других более простых чёрных ящичков, это как, например наша система состоит из двух или трёх логических элементов, вся система, это наш чёрный ящик, а логические элементы, это те чёрные ящички из которых состоит система, на более низком уровне иерархии. Во как замутил.

Ладно, суть понятна, далее будем разгребать пример из книги, цифровая система S, нужно же детально разобраться во всех этих премудростях...

Основной первый этап в освоении ПЛИС (xilinx) и языка VHDL, это основы языка VHDL. Тут будет такой, своего рода, небольшой конспект с основными выдержками из различной литературы, чтобы отсеять всё лишнее и оставить саму суть. Которую и нужно понять и сохранить в своих мозгах. Если что-то будет повторяться, ничего страшного, "Повторение мать учения" (С).

Основные элементы языка VHDL.

Опущу часть касающуюся, когда появился и где, данный язык описания аппаратуры, так как это можно прочитать в предисловии любой книги по VHDL имеющейся на русском языке, у нас другая задача, освоить основы данного языка, что я и буду делать.

Структурное и поведенческое описание цифровой системы.

Цифровая система может быть описана на уровне поведения посредством описания функций, реализуемых системой, и на структурном уровне.

Пока понятно, где-то на подсознательном уровне, описание на структурном уровне, то есть систему можно описать в виде подробного описания всех блоков из которых состоит данная система, а описание на уровне поведения, это когда мы описываем, что будет на выходе системы в зависимости от информации на входе, не вдаваясь в подробности её внутреннего устройства, мне это так видится.

А вот и более точные определения этих двух методов описания цифровой системы:

Структурное описание - это описание системы в виде совокупности компонент (подсхем, элементов) и связей между компонентами.

Поведенческое описание - это описание системы при помощи некоторых процедур на уровне зависимостей выходов от входов. Иначе говоря, поведенческое описание задаёт алгоритм, реализуемый системой.

Как вроде всё мы правильно поняли, будем дальше разбираться...

Что же у нас пишут дальше в умной книжке:

Цифровая система может быть сложной, как, например, микропроцессор или весьма простой, как логическая схема, состоящая из логических элементов (вентилей).

Чтож вполне логично, если мы делаем Микро-ЭВМ, хотя бы с одним микропроцессором, то система у нас будет довольно таки сложной, а если мы хотим просто помигать двумя или одним светодиодом, то относительно простой.

Далее пишут:

Естественно, некоторые компоненты системы в структурном описании могут состоять из нескольких частей - компонент более низкого уровня иерархии описания. Представляя отношение вхождения подсхем в схемы в виде графа, можно получить дерево (граф) иерархии описания всей системы.

Вот жеж любят всё усложнять, ну первое предложение, как бы сразу понятно, зачем второе предложение так замудрённо писать, ну да ладно авторам виднее, а нам главное понять. Смысл до меня дошёл следующий, когда мы описываем на структурном уровне нашу системы, представив её в виде чёрного ящика с определённым количеством входов и выходов, мы должны понимать или допетривать, хрен знает как правильнее написать, что этот чёрный ящик наш может состоять из других более простых чёрных ящичков, это как, например наша система состоит из двух или трёх логических элементов, вся система, это наш чёрный ящик, а логические элементы, это те чёрные ящички из которых состоит система, на более низком уровне иерархии. Во как замутил.

Ладно, суть понятна, далее будем разгребать пример из книги, цифровая система S, нужно же детально разобраться во всех этих премудростях...

Последний раз редактировалось: Viktor2312 (Пт Янв 02 2015, 18:12), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Основы языка VHDL

Re: Основы языка VHDL

2

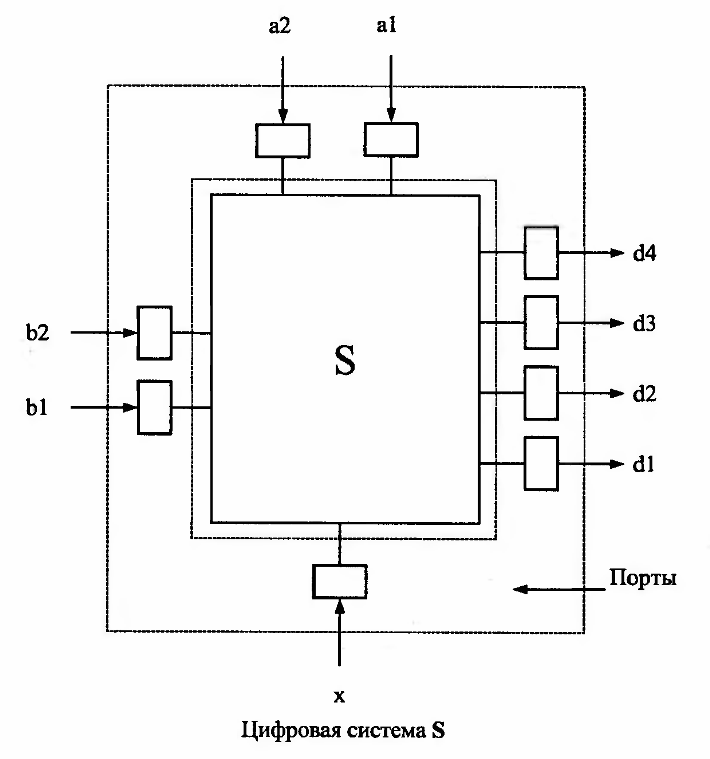

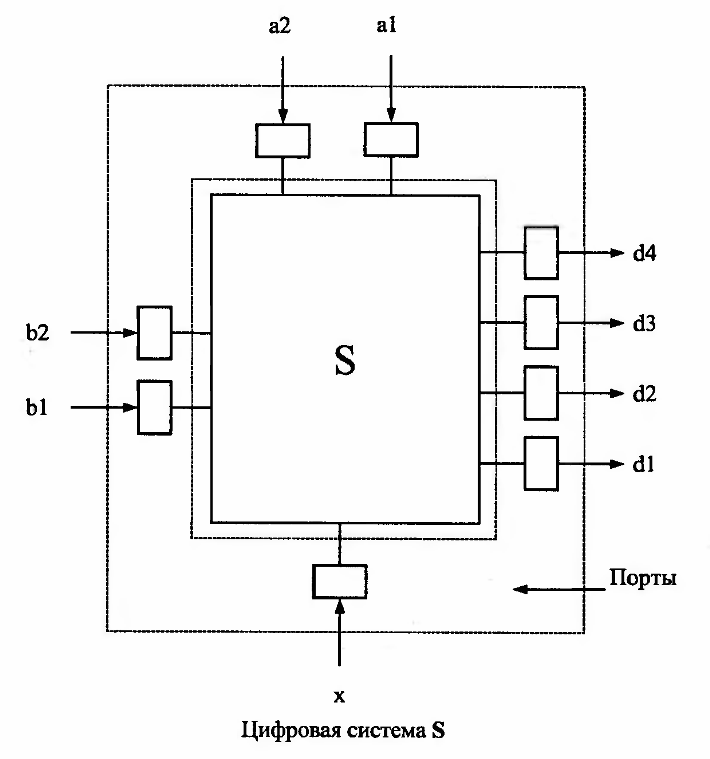

Итак движемся дальше, есть вот такой рисунок, с ним и будем дальше разбираться:

По тексту:

Пусть цифровая система S реализует следующий алгоритм. На входные полюсы системы S подаются два двухразрядных числа a=(a2, a1), b=(b2, b2), где a2, b2 - старшие разряды числа a, b соответственно и x - управляющий сигнал.

Если x=1, система S должна перемножить числа a, b и выдать четырёхразрядное число d=(d4, d3, d2, d1), где d=a x b (d равно a умножить на b).

Если x=0, то числа a, b должны быть сложены, при этом в разряде d4 всегда должен быть ноль, в разряде d3 - перенос с2, в разряде d2 - старший разряд суммы s2, в разряде d1 - младший разряд суммы s1.

Предполагается, что

Мы описали алгоритм, который должна реализовать система S, на русском языке. Однако для автоматизированного (на ЭВМ) проектирования требуется формальная спецификация.

Думаю тут всем понятен смысл данной системы, видать дальше будет углубление в то как правильно это всё описать на VHDL, чтож, почитаем, поразбираемся далее.

Формальные спецификации должны быть записаны на соответствующем формальном языке. Позже будет показано, что алгоритм, реализуемый системой S, может быть очень коротко описан на языке VHDL. Если же рассматривать структурный уровень описания системы S, то можно легко увидеть, что в систему S входит двухразрядный сумматор и двухразрядный умножитель.

Двухразрядный сумматор - это устройство для сложения двухразрядных чисел, двухразрядный умножитель - устройство для перемножения двух чисел, каждое из которых имеет только два разряда. В систему S также должно входить простейшее устройство управления и схема дизъюнктивного объединения выходных сигналов. Структура системы S изображена ниже:

На рисунке adder_2 - двухразрядный сумматор, mult_2 - двухразрядный умножитель, YY - устройство управления, dd - схема дизъюнктивного формирования выходных сигналов. Схему dd образуют три дизъюнктора. Устройство управления YY является весьма простым и функционирует следующим образом:

если x=0, то

т. е. числа a, b подаются на вход сумматора adder_2.

Если же, x=1, то

т. е. числа a, b подаются на вход умножителя mult_2.

Ну, как вроде логика работы данной схемы более менее понятна, пока ничего конкретного и сложного нет, будем двигаться дальше по тексту.

По тексту:

Пусть цифровая система S реализует следующий алгоритм. На входные полюсы системы S подаются два двухразрядных числа a=(a2, a1), b=(b2, b2), где a2, b2 - старшие разряды числа a, b соответственно и x - управляющий сигнал.

Если x=1, система S должна перемножить числа a, b и выдать четырёхразрядное число d=(d4, d3, d2, d1), где d=a x b (d равно a умножить на b).

Если x=0, то числа a, b должны быть сложены, при этом в разряде d4 всегда должен быть ноль, в разряде d3 - перенос с2, в разряде d2 - старший разряд суммы s2, в разряде d1 - младший разряд суммы s1.

Предполагается, что

(a2, a1) + (b2, b1) = (c2, s2, s1).

Мы описали алгоритм, который должна реализовать система S, на русском языке. Однако для автоматизированного (на ЭВМ) проектирования требуется формальная спецификация.

Думаю тут всем понятен смысл данной системы, видать дальше будет углубление в то как правильно это всё описать на VHDL, чтож, почитаем, поразбираемся далее.

Формальные спецификации должны быть записаны на соответствующем формальном языке. Позже будет показано, что алгоритм, реализуемый системой S, может быть очень коротко описан на языке VHDL. Если же рассматривать структурный уровень описания системы S, то можно легко увидеть, что в систему S входит двухразрядный сумматор и двухразрядный умножитель.

Двухразрядный сумматор - это устройство для сложения двухразрядных чисел, двухразрядный умножитель - устройство для перемножения двух чисел, каждое из которых имеет только два разряда. В систему S также должно входить простейшее устройство управления и схема дизъюнктивного объединения выходных сигналов. Структура системы S изображена ниже:

На рисунке adder_2 - двухразрядный сумматор, mult_2 - двухразрядный умножитель, YY - устройство управления, dd - схема дизъюнктивного формирования выходных сигналов. Схему dd образуют три дизъюнктора. Устройство управления YY является весьма простым и функционирует следующим образом:

если x=0, то

(a2, a1) = (f4, f3),

(b2, b1) = (f6, f5),

(f2, f1) = (0, 0),

(b2, b1) = (f6, f5),

(f2, f1) = (0, 0),

т. е. числа a, b подаются на вход сумматора adder_2.

Если же, x=1, то

(f4, f3) = (0, 0),

(f6, f5) = (0, 0),

(a2, a1) = (f2, f1),

(f6, f5) = (0, 0),

(a2, a1) = (f2, f1),

т. е. числа a, b подаются на вход умножителя mult_2.

Ну, как вроде логика работы данной схемы более менее понятна, пока ничего конкретного и сложного нет, будем двигаться дальше по тексту.

Последний раз редактировалось: Viktor2312 (Сб Янв 03 2015, 14:37), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Основы языка VHDL

Re: Основы языка VHDL

3

В этом посте буду делать различные пометки, сносить сюда правила, определения, особые символы и т. д.

В языке VHDL знак & употребляется не для обозначения логической операции "И" (конъюнкции), (and), а для операции конкатенации векторов.

<= Оператор назначения сигнала

Оператор and используется для выполнения логической операции И

Оператор or используется для выполнения логической операции ИЛИ

Оператор not используется для выполнения логической операции НЕ

Последний раз редактировалось: Viktor2312 (Вс Янв 04 2015, 11:32), всего редактировалось 4 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Основы языка VHDL

Re: Основы языка VHDL

4

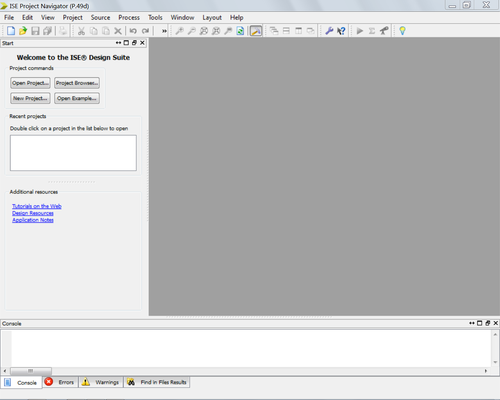

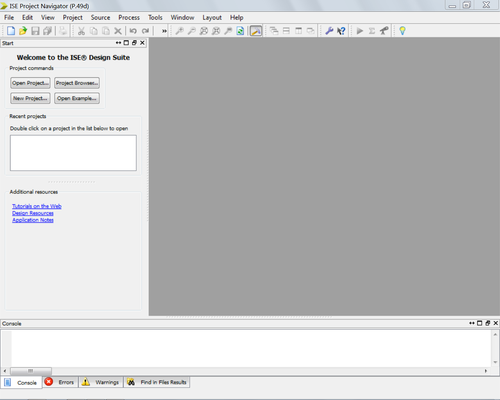

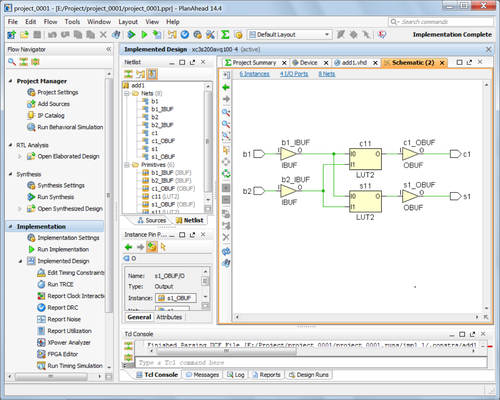

Для дальнейшего освоения требуется среда разработки САПР, для этого можно скачать, например Xilinx ISE Design Suite 14.4 которую скачал я себе, как основную для дальнейшего освоения ПЛИС.

Лучше это сделать сейчас и заранее, скачать её можно здесь:

http://rutracker.org/forum/viewtopic.php?t=4310556

или на официальном сайте:

http://www.xilinx.com/support...

После её запуска появляется основное окно, которое выглядит следующим образом:

0003

Лучше это сделать сейчас и заранее, скачать её можно здесь:

http://rutracker.org/forum/viewtopic.php?t=4310556

или на официальном сайте:

http://www.xilinx.com/support...

После её запуска появляется основное окно, которое выглядит следующим образом:

0003

Последний раз редактировалось: Viktor2312 (Сб Янв 03 2015, 15:31), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Основы языка VHDL

Re: Основы языка VHDL

5

Пока САПР качается или устанавливается или это уже сделано, можно двигаться дальше изучая предоставленную информацию в тексте книжечки.

Пусть описание системы S имеет имя VLSI_1. Тогда иерархия структурного описания системы S будет иметь вид:

Тут как бы тоже всё понятно, система S под именем VLSI_1 имеет четыре блока, сумматор, умножитель, блок управления и блок формирования выходного сигнала, если кратко.

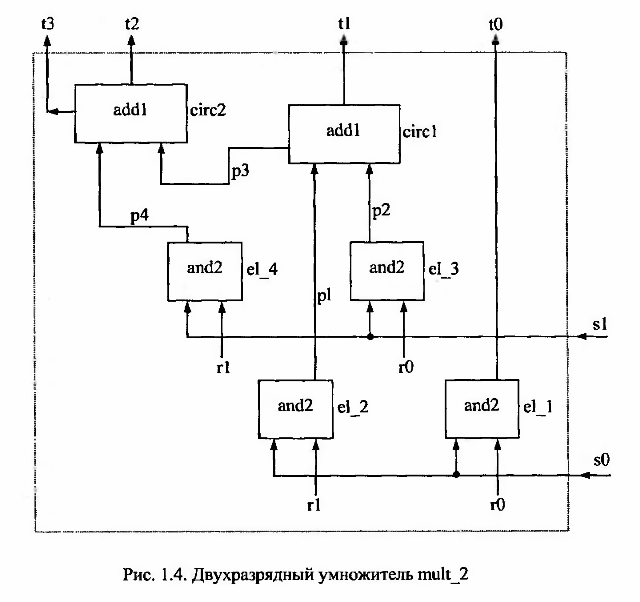

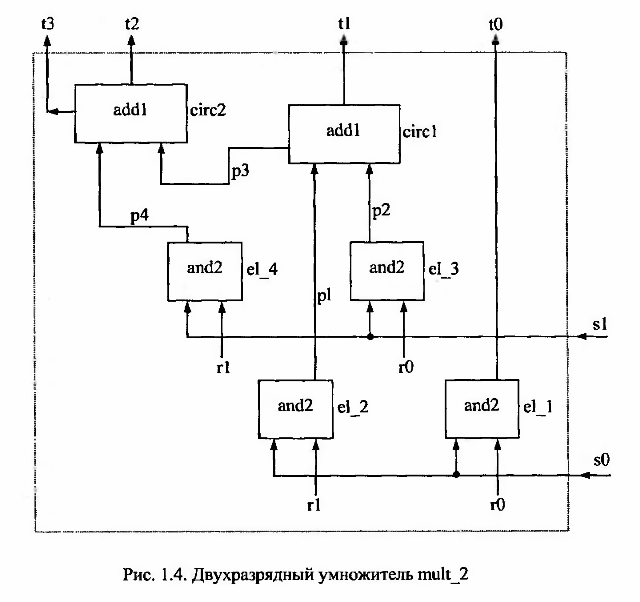

Рассмотрим двухразрядный умножитель mult_2. Его устройство представлено ниже на рисунке:

На вход данной схемы поступают сигналы r1, r0, s1, s0. Сигналы r1, r0 интерпретируются как двухразрядное целое число r = (r1, r0), сигналы s1, s0 - как двухразрядное целое число s = (s1, s0).

Выходные сигналы t3, t2, t1, t0 представляют разряды числа t = (t3, t2, t1, t0) - произведения чисел r, s:

В схему входят элементы двух типов - add1 и and2.

Элемент and2 представляет собой логический элемент И - двухвходовый конъюнктор.

Оператором логической конъюнкции служит оператор and, поэтому описание функции элемента and2 на языке VHDL выглядит следующим образом:

где x1, x2 - имена входных сигналов, y - имя выходного сигнала, <= - оператор назначения сигнала.

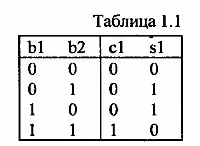

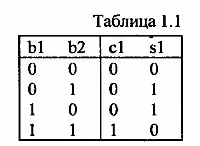

Элемент add1 представляет собой одноразрядный полусумматор, функционирование которого описывается таблицей истинности (Табл. 1.1):

В данном случае b1, b2 интерпретируются как одноразрядные числа, s1 - сумма, c1 - перенос в следующий разряд.

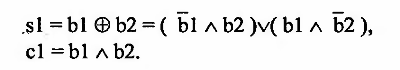

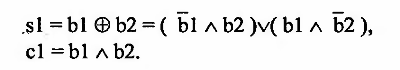

В привычной математической записи булевы функции s1, c1 могут быть представлены следующим образом:

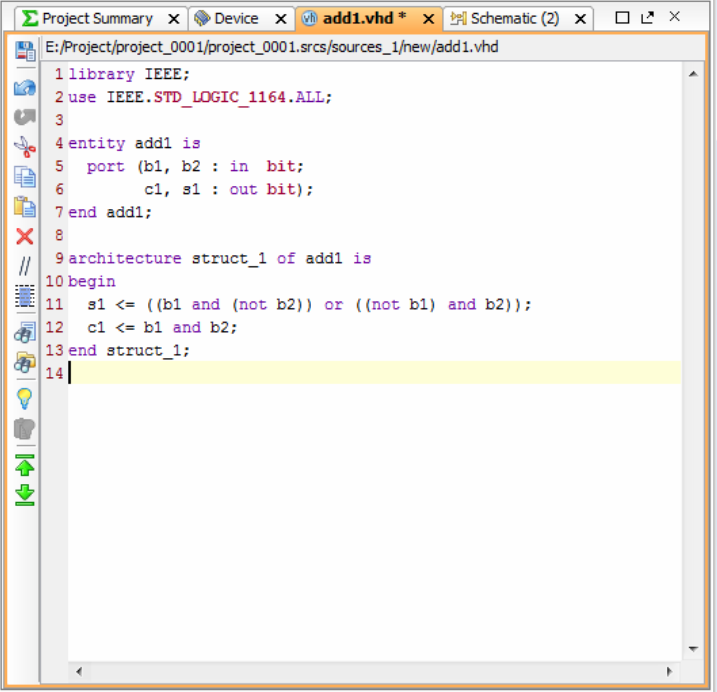

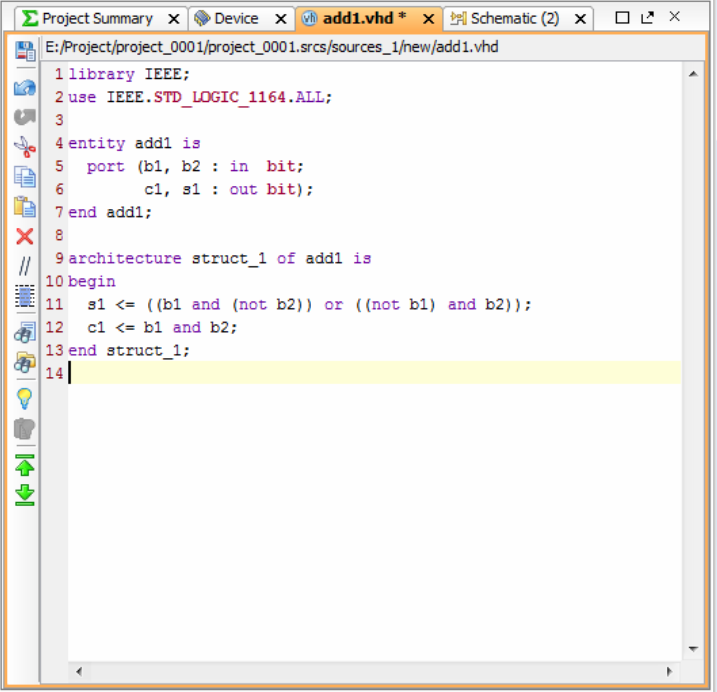

В языке VHDL функционирование элемента add1 записывается следующим образом:

Вот тут честно говоря я не въехал, как-то не особо совпадает с формулой выше или возможно скобка пропущена, я бы это записал так:

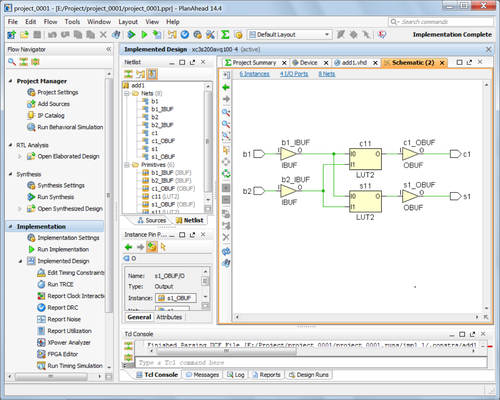

Попробовал синтезировать этот код в Xilinx PlanAhead 14.4

Нормально синтезировался

...

Пусть описание системы S имеет имя VLSI_1. Тогда иерархия структурного описания системы S будет иметь вид:

Тут как бы тоже всё понятно, система S под именем VLSI_1 имеет четыре блока, сумматор, умножитель, блок управления и блок формирования выходного сигнала, если кратко.

Рассмотрим двухразрядный умножитель mult_2. Его устройство представлено ниже на рисунке:

На вход данной схемы поступают сигналы r1, r0, s1, s0. Сигналы r1, r0 интерпретируются как двухразрядное целое число r = (r1, r0), сигналы s1, s0 - как двухразрядное целое число s = (s1, s0).

Выходные сигналы t3, t2, t1, t0 представляют разряды числа t = (t3, t2, t1, t0) - произведения чисел r, s:

(t3, t2, t1, t0) = (r1, r0) x (s1, s0).

В схему входят элементы двух типов - add1 и and2.

Элемент and2 представляет собой логический элемент И - двухвходовый конъюнктор.

Оператором логической конъюнкции служит оператор and, поэтому описание функции элемента and2 на языке VHDL выглядит следующим образом:

y <= x1 and x2;

где x1, x2 - имена входных сигналов, y - имя выходного сигнала, <= - оператор назначения сигнала.

Элемент add1 представляет собой одноразрядный полусумматор, функционирование которого описывается таблицей истинности (Табл. 1.1):

В данном случае b1, b2 интерпретируются как одноразрядные числа, s1 - сумма, c1 - перенос в следующий разряд.

В привычной математической записи булевы функции s1, c1 могут быть представлены следующим образом:

В языке VHDL функционирование элемента add1 записывается следующим образом:

s1 <= ((b1 and (not b2)) or (not b1) and b2));

с1 <= b1 and b2;

с1 <= b1 and b2;

Вот тут честно говоря я не въехал, как-то не особо совпадает с формулой выше или возможно скобка пропущена, я бы это записал так:

s1 <= ((not b1) and b2) or (b1 and (not b2));

с1 <= b1 and b2;

с1 <= b1 and b2;

Попробовал синтезировать этот код в Xilinx PlanAhead 14.4

- Код:

entity add1 is

port (b1, b2 : in bit;

c1, s1 : out bit);

end add1;

architecture struct_1 of add1 is

begin

s1 <= ((b1 and (not b2)) or ((not b1) and b2));

c1 <= b1 and b2;

end struct_1;

Нормально синтезировался

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» Стандартная библиотека языка Си.

» Изучаем Java. Основы.

» Литература о ИИ и ИР

» Изучаем основы VHDL, ISE, ПЛИС Xilinx.

» Изучаем основы VHDL, ISE, ПЛИС Xilinx. Старые семейства.

» Изучаем Java. Основы.

» Литература о ИИ и ИР

» Изучаем основы VHDL, ISE, ПЛИС Xilinx.

» Изучаем основы VHDL, ISE, ПЛИС Xilinx. Старые семейства.

RUЭВМ :: ПЛИС, CPLD, FPGA, VHDL, Verilog. COWIN, AMD/Xilinx, Intel/Altera :: Язык описания аппаратуры VHDL

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|