Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

HM-SHA256-FPGA_v001. R0_I0_B0.

RUЭВМ :: Отечественные ЭВМ, ПЭВМ и МВК :: _______вход :: HM-SHA256-FPGA_v001 :: HM-SHA256-FPGA_v001. R0_I0...63_B0+ADDER

Страница 1 из 1 • Поделиться

HM-SHA256-FPGA_v001. R0_I0_B0.

HM-SHA256-FPGA_v001. R0_I0_B0.

1

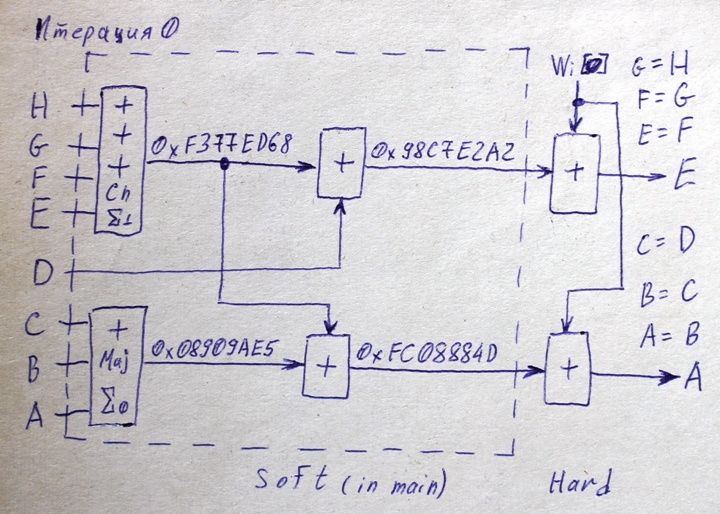

Раунд0_Итерация0_Ветвь0.

Итак, в виду того, что:

Инициализация переменных

(первые 32 бита дробных частей квадратных корней первых восьми простых чисел [от 2 до 19]):

h0 := 0x6A09E667

h1 := 0xBB67AE85

h2 := 0x3C6EF372

h3 := 0xA54FF53A

h4 := 0x510E527F

h5 := 0x9B05688C

h6 := 0x1F83D9AB

h7 := 0x5BE0CD19

Мы имеем начальные фиксированные значения для слов в первой итерации, пардон, в нулевой итерации...

a := h0

b := h1

c := h2

d := h3

e := h4

f := h5

g := h6

h := h7

Мы не будем это всё реализовывать в железе и тратить на это "железо", деньги и время, время на вычисления, каждый раз...

Cy0 = (a rotr 2) xor (a rotr 13) xor (a rotr 22)

a = 0x6A09E667

(a rotr 2) = 0xDA827999

(a rotr 13) = 0x333B504F

(a rotr 22) = 0x27999DA8

0xDA827999 xor 0x333B504F = 0xE9B929D6

Cy0 = 0xE9B929D6 xor 0x27999DA8 = 0xCE20B47E

Для 0-й итерации:

Maj = (a and b) xor (a and c) xor (b and c)

(a and b) = 0x6A09E667 and 0xBB67AE85 = 0x2A01A605

(a and c) = 0x6A09E667 and 0x3C6EF372 = 0x2808E262

(b and c) = 0xBB67AE85 and 0x3C6EF372 = 0x3866A200

0x2A01A605 xor 0x2808E262 = 0x02094467

Maj = 0x02094467 xor 0x3866A200 = 0x3A6FE667

T2 = Maj + Cy0

T2 = 0x08909AE5

____Прежде чем продолжить дальше, нужно проверить закон:

Закон дистрибутивности. Дистрибутивность конъюнкции и суммы по модулю два.

(a and b) xor (a and c) = a and (b xor c) !!!

____Он позволит нам в каждом блоке Maj избавиться от одной операции and, что сэкономит LUT -ы. Итак преобразуем формулу:

Maj = (a and b) xor (a and c) xor (b and c), в

Maj = (a and (b xor c)) xor (b and c), и посчитаем, получится ли у нас тот же результат:

Maj = (0x6A09E667 and (0xBB67AE85 xor 0x3C6EF372)) xor (0xBB67AE85 and 0x3C6EF372) =

= (0x6A09E667 and 0x87095DF7) xor 0x3866A200 =

= 0x02094467 xor 0x3866A200 = 0x3A6FE667

Результаты совпали, ура, мы сэкономим огромное количество LUT -ов.

Далее вычисляем:

Cy1 = (e rotr 6) xor (e rotr 11) xor (e rotr 25)

h4 := 0x510E527F

e := h4

(0x510E527F rotr 6) = 0xFD443949

(0x510E527F rotr 11) = 0x4FEA21CA

(0x510E527F rotr 25) = 0x87293FA8

0xFD443949 xor 0x4FEA21CA = 0xB2AE1883

0xB2AE1883 xor 0x87293FA8 = 0x3587272B

Cy1 = 0x3587272B

____Далее вычисляем значение на выходе блока Ch:

Ch = (e and f) xor ((not e) and g)

e = 0x510E527F

f = 0x9B05688C

g = 0x1F83D9AB

(not e) = 0xAEF1AD80

Ch = (0x510E527F and 0x9B05688C) xor (0xAEF1AD80 and 0x1F83D9AB) =

= 0x1104400C xor 0x0E818980 = 0x1F85C98C

Ch = 0x1F85C98C

____Находим сумму Adder4:

Adder4 = Ch + Cy1

Adder4 = 0x1F85C98C + 0x3587272B

Adder4 = 0x550CF0B7

____Находим сумму Adder1:

K0 = 0x428A2F98

Adder1 = h + k0

Adder1 = 0x5BE0CD19 + 0x428A2F98

Adder1 = 0x9E6AFCB1

____Находим сумму Adder2:

Adder2 = Adder1 + Adder4

Adder2 = 0x9E6AFCB1 + 0x550CF0B7

Adder2 = 0xF377ED68

____И в итоге, мы имеем полностью просчитанную нулевую итерацию. Остаётся в ней реализовать три "железных" сумматора, на самом деле, как будет видно далее, только два упрощённых сумматора, для того, чтобы находить T1, A и E. Естественно все вычисления нужно будет ещё раз проверить, и проверить с произвольным Wi внесённые изменения.

И вот посмотрев на Итерацию 0, где мне требуется пусть и упрощённых, но 3 сумматора, я решил подумать и до меня дошло, что там закралось ещё одно сложение с двумя известными константами, это значение после Adder2 и значение входного D.

В результате сложив их, нам для получения выходного A, потребуется к результату просто прибавить W[0]. Так же и со вторым сумматором, для E.

А именно:

A = 0xF377ED68 + W[0] + 0x08909AE5

От перемены мест слагаемых сумма не меняется!

A = 0xF377ED68 + 0x08909AE5 + W[0] = 0xFC08884D + W[0] - 1-й упрощённый сумматор.

Аналогично и с E.

E = 0xF377ED68 + W[0] + 0xA54FF53A

От перемены мест слагаемых сумма не меняется!

E = 0xF377ED68 + 0xA54FF53A + W[0] = 0x98C7E2A2 + W[0] - 2-й упрощённый сумматор.

В итоге в итерации 0 потребуется всего два упрощённых сумматора, упрощённых, потому, что один из операндов нам известен, как собственно и отдельные биты второго операнда. Я думаю понятно же, что если мы знаем, например, что бит 0 первого операнда равен лог. 0 и нулевой бит второго операнда равен лог. 0, то сумма даст лог. 0 и бит переноса будет равен лог.0, а так как это константы, которые не меняются, думаю понятно, что не нужно реализовывать сумматор для этого бита в "железе", так как результат будет всё равно равен лог.0, так же и в ситуации если в первом операнде лог. 0, а во втором лог. 1, это будет просто повторитель, то есть можно подать значение этого бита второго операнда на выход, и бит переноса всегда будет равен лог. 0.

В итоге придётся всё переразрабатывать, учитывая это, зато убирается ещё куча "железа" и экономия в потреблении.

И в итоге имеем материал для работы над оставшимися двумя упрощёнными сумматорами, которые и будут уже реализованы в железе.

.

Последний раз редактировалось: Viktor2312 (Вт Фев 01 2022, 11:51), всего редактировалось 10 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

R0_I0_B0_ADDER_A

R0_I0_B0_ADDER_A

3

W[0]

H - Версия. Константа 001, на данный момент времени, использовать как константу нельзя. Со временем может измениться. Требуется вычислять.

X - Поле поиска 16 бит, 65536 вариантов (0...65535, от 0x0000 до 0xFFFF). Распараллеливание на 65536 ветвей. Внутри каждой ветви, вычислять не требуется, константа.

G - Поле голосования 13 бит, использовать как константу нельзя, требуется вычислять.

|*|HHHX|XXXX|*|XXXX|XXXX|*|XXXG|GGGG|*|GGGG|GGGG|*|

|*|H,H,H,15|14,13,12,11|*|10,9,8,7|6,5,4,3|*|2,1,0,12|11,10,9,8|*|7,6,5,4|3,2,1,0|*|

Изменение порядка байт:

|*|GGGG|GGGG|*|XXXG|GGGG|*|XXXX|XXXX|*|HHHX|XXXX|*|

|*|7,6,5,4|3,2,1,0|*|2,1,0,12|11,10,9,8|*|10,9,8,7|6,5,4,3|*|H,H,H,15|14,13,12,11|*|

Входные данные итерации0

a = h0 := 0x6A09E667

b = h1 := 0xBB67AE85

c = h2 := 0x3C6EF372

d = h3 := 0xA54FF53A

e = h4 := 0x510E527F

f = h5 := 0x9B05688C

g = h6 := 0x1F83D9AB

h = h7 := 0x5BE0CD19

k[0] := 0x428A2F98

Поле поиска имеет значение: 0x0000

Выходные данные итерации0

H = 0x1F83D9AB

G = 0x9B05688C

F = 0x510E527F

E = 0x98C7E2A2 + W[0]

D = 0x3C6EF372

C = 0xBB67AE85

B = 0x6A09E667

A = 0xFC08884D + W[0]

R0_I0_B0 A, Ветвь 0 Выходные данные.

Раунд0 (Round0) - R0

Итерация0 (Iteration0) - I0

Ветвь0 (Branch0) - B0

П - повторитель.

P - бит переноса.

| 1111 1100 | 0000 1000 | 1000 1000 | 0100 1101 | = A

+

| GGGG GGGG | 000G GGGG |0000 0000 | HHH0 0000 | = W[0]

=

|++++ ++ПП | 00P+ +ППП | 1000 100P |++П0 1101|

Требуется три упрощённых сумматора.

Разряды 7, 6, 5 требуют простейшего сумматора, но из-за того, что разряды 7, 6, 5 числа А нам известны, то сумматор вырождается в три логических элемента: инвертор НЕ (not), исключающее ИЛИ (xor) и логического умножения И (and).

0 1 0

+

H2 H1 H0

=

8 разряд = H1 and H2

7 разряд = H1 xor H2

6 разряд = not H1

5 разряд = H0

Входной бит переноса в 5-й разряд отсутствует и всегда равен лог. 0. Бит переноса из 5-ого разряда в 6-ой, всегда равен лог.0 и не требуется. Бит переноса из 6-ого разряда в 7-ой равен H1. Бит переноса из 7-ого в 8-й разряд равен H1 and H2 и этому равен сам восьмой разряд.

Картинка: https://cloud.mail.ru/public/Quah/F2FgEPc4k

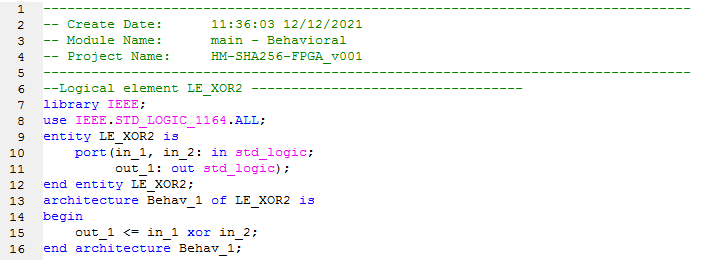

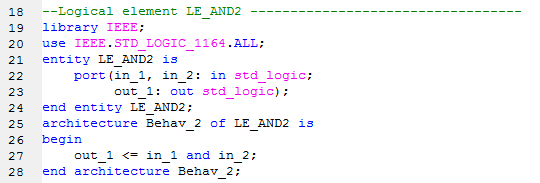

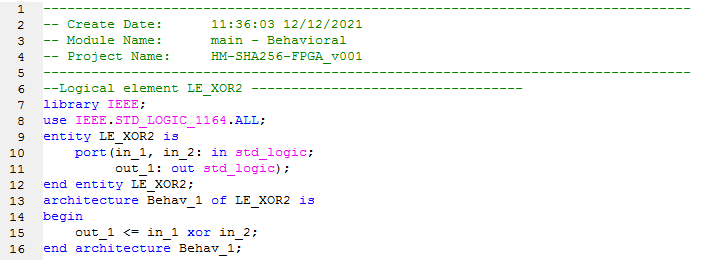

LE - Логический элемент (Logical element), например, LE_XOR2, двухвходовый логический элемент исключающее ИЛИ (xor).

Прежде всего, в начале проекта необходимо создать простейшие логические элементы, чтобы потом можно было их многократно использовать. Для начала создадим необходимые, а потом можно будет добавить и другие, по мере надобности.

Дальнейший расчёт и схемное решение для разрядов 21, 20, 19.

Картинка: https://cloud.mail.ru/public/vZMh/Ybrq19jfD

Дальнейший расчёт и схемное решение для разрядов 31, 30, 29, 28, 27, 26.

Картинка 1: https://cloud.mail.ru/public/ptRy/mKzKWomn3

Картинка 2: https://cloud.mail.ru/public/ku8K/BTod9PM4d

Картинка 3: https://cloud.mail.ru/public/j8XR/L5SqV2Qaj

Для реализации нашего компонента, реализующего функции сумматора, в соответствии с схемой, представленной выше, нам потребуются три новых логических элемента: 3ИЛИ (LE_OR3), 4ИЛИ (LE_OR4) и 5ИЛИ (LE_OR5), которых у нас ещё нет в проекте. Поэтому создадим их.

Картинка. Жопа вся в том, что РКП и их приспешники, что-то похерили и мелкие картинки грузятся, а вот на 260 Кб, уже нах посылает, поэтому в виде ссылки:

https://cloud.mail.ru/public/1F6C/uNGuWuKSQ

А хотя я затупил и в формате BMP попытался загнать, а в PNG она уже 8+ Кб весит и вуаля:

Ну и по аналогии, создаём и добавляем в проект ещё два логических элемента:

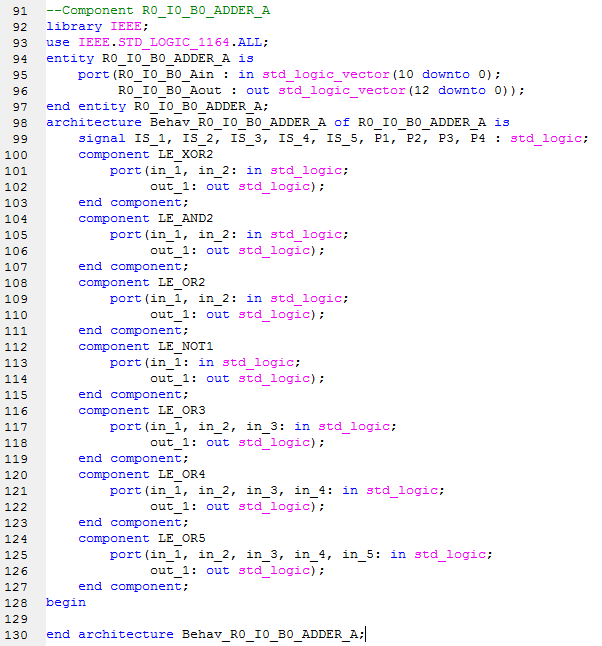

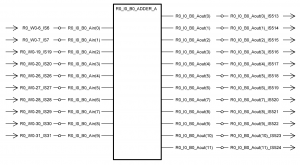

Итак, в нашем компоненте имеется одиннадцать входов (11) и тринадцать выходов (13). Потребуются логические элементы 2И, 2ИЛИ, 3ИЛИ, 4ИЛИ, 5ИЛИ, НЕ, исключающее ИЛИ, которые у нас уже созданы. Осталось написать код.

Название компонента: R0_I0_B0_ADDER_A

R0_I0_B0_Ain : in std_logic_vector(10 downto 0); - Входные 11 сигналов компонента.

R0_I0_B0_Aout : out std_logic_vector(12 downto 0); - Выходные 13 сигналов компонента.

IS_1, IS_2, IS_3, IS_4, IS_5, P1, P2, P3, P4 : std_logic; - Внутренние сигналы.

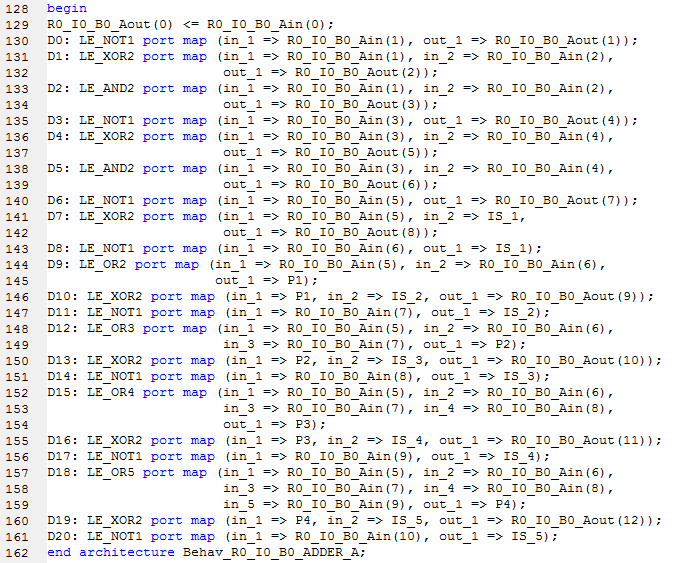

Основная часть кода компонента готова:

Сама же суть будет находиться после слова begin, а именно, следующее:

Вот такой у нас получился элемент, ну или точнее компонент:

Внутренняя же структура нашего компонента выглядит так:

Как видно из кода R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0); входной сигнал R0_I0_B0_Ain(0) напрямую проходит на выход, то есть на выходной сигнал R0_I0_B0_Aout(0), но внутри микросхемы ПЛИС напрямую ничего не проходит, только через входные и выходные буферы, что мы и можем наблюдать на внутренней схеме компонента, а именно:

И проанализировав, приходим к выводу, что от этой строчки в коде:

R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0);

нам нужно избавиться, так как мы просто тратим два буфера, входной и выходной и ничего более, а подавать сразу на выход 5-й разряд числа W[0], то есть W0-5. И даже не на выход, а на вход первой итерации.

Что же мы имеем в результате на выходе (R0_I0_B0):

|++++ ++ПП | 00P+ +ППП | 1000 100P |+++0 1101|

Разряд 0: 1

Разряд 1: 0

Разряд 2: 1

Разряд 3: 1

Разряд 4: 0

Разряд 5: S5 (R0_I0_B0_Aout(0))

Разряд 6: S6 (R0_I0_B0_Aout(1))

Разряд 7: S7 (R0_I0_B0_Aout(2))

Разряд 8: S8 (R0_I0_B0_Aout(3))

Разряд 9: 0

Разряд 10: 0

Разряд 11: 1

Разряд 12: 0

Разряд 13: 0

Разряд 14: 0

Разряд 15: 1

Разряд 16: П W0-16

Разряд 17: П W0-17

Разряд 18: П W0-18

Разряд 19: S19 (R0_I0_B0_Aout(4))

Разряд 20: S20 (R0_I0_B0_Aout(5))

Разряд 21: S21 (R0_I0_B0_Aout(6))

Разряд 22: 0

Разряд 23: 0

Разряд 24: П W0-24

Разряд 25: П W0-25

Разряд 26: S26 (R0_I0_B0_Aout(7))

Разряд 27: S27 (R0_I0_B0_Aout(8 ))

Разряд 28: S28 (R0_I0_B0_Aout(9))

Разряд 29: S29 (R0_I0_B0_Aout(10))

Разряд 30: S30 (R0_I0_B0_Aout(11))

Разряд 31: S31 (R0_I0_B0_Aout(12))

Итак, подправим код и избавимся от строчки: R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0);

Естественно станет меньше на один входной и выходной сигнал:

R0_I0_B0_Ain : in std_logic_vector(9 downto 0); - Входные 10 сигналов компонента.

R0_I0_B0_Aout : out std_logic_vector(11 downto 0); - Выходные 12 сигналов компонента.

|++++ ++ПП | 00P+ +ППП | 1000 100P |++П0 1101|

Разряд 0: 1

Разряд 1: 0

Разряд 2: 1

Разряд 3: 1

Разряд 4: 0

Разряд 5: W0-5

Разряд 6: S6 (R0_I0_B0_Aout(0))

Разряд 7: S7 (R0_I0_B0_Aout(1))

Разряд 8: S8 (R0_I0_B0_Aout(2))

Разряд 9: 0

Разряд 10: 0

Разряд 11: 1

Разряд 12: 0

Разряд 13: 0

Разряд 14: 0

Разряд 15: 1

Разряд 16: П W0-16

Разряд 17: П W0-17

Разряд 18: П W0-18

Разряд 19: S19 (R0_I0_B0_Aout(3))

Разряд 20: S20 (R0_I0_B0_Aout(4))

Разряд 21: S21 (R0_I0_B0_Aout(5))

Разряд 22: 0

Разряд 23: 0

Разряд 24: П W0-24

Разряд 25: П W0-25

Разряд 26: S26 (R0_I0_B0_Aout(6))

Разряд 27: S27 (R0_I0_B0_Aout(7))

Разряд 28: S28 (R0_I0_B0_Aout(8 ))

Разряд 29: S29 (R0_I0_B0_Aout(9))

Разряд 30: S30 (R0_I0_B0_Aout(10))

Разряд 31: S31 (R0_I0_B0_Aout(11))

И изменённый код:

Maximum combinational path delay: 8.451ns - в случае размещения в Spartan-3 (XC3S200A-4VQ100).

Вот теперь замечательно, есть инвертор и он обрамлён входным и выходным буфером:

.

H - Версия. Константа 001, на данный момент времени, использовать как константу нельзя. Со временем может измениться. Требуется вычислять.

X - Поле поиска 16 бит, 65536 вариантов (0...65535, от 0x0000 до 0xFFFF). Распараллеливание на 65536 ветвей. Внутри каждой ветви, вычислять не требуется, константа.

G - Поле голосования 13 бит, использовать как константу нельзя, требуется вычислять.

|*|HHHX|XXXX|*|XXXX|XXXX|*|XXXG|GGGG|*|GGGG|GGGG|*|

|*|H,H,H,15|14,13,12,11|*|10,9,8,7|6,5,4,3|*|2,1,0,12|11,10,9,8|*|7,6,5,4|3,2,1,0|*|

Изменение порядка байт:

|*|GGGG|GGGG|*|XXXG|GGGG|*|XXXX|XXXX|*|HHHX|XXXX|*|

|*|7,6,5,4|3,2,1,0|*|2,1,0,12|11,10,9,8|*|10,9,8,7|6,5,4,3|*|H,H,H,15|14,13,12,11|*|

Входные данные итерации0

a = h0 := 0x6A09E667

b = h1 := 0xBB67AE85

c = h2 := 0x3C6EF372

d = h3 := 0xA54FF53A

e = h4 := 0x510E527F

f = h5 := 0x9B05688C

g = h6 := 0x1F83D9AB

h = h7 := 0x5BE0CD19

k[0] := 0x428A2F98

Поле поиска имеет значение: 0x0000

Выходные данные итерации0

H = 0x1F83D9AB

G = 0x9B05688C

F = 0x510E527F

E = 0x98C7E2A2 + W[0]

D = 0x3C6EF372

C = 0xBB67AE85

B = 0x6A09E667

A = 0xFC08884D + W[0]

R0_I0_B0 A, Ветвь 0 Выходные данные.

Раунд0 (Round0) - R0

Итерация0 (Iteration0) - I0

Ветвь0 (Branch0) - B0

П - повторитель.

P - бит переноса.

| 1111 1100 | 0000 1000 | 1000 1000 | 0100 1101 | = A

+

| GGGG GGGG | 000G GGGG |0000 0000 | HHH0 0000 | = W[0]

=

|++++ ++ПП | 00P+ +ППП | 1000 100P |++П0 1101|

Требуется три упрощённых сумматора.

Разряды 7, 6, 5 требуют простейшего сумматора, но из-за того, что разряды 7, 6, 5 числа А нам известны, то сумматор вырождается в три логических элемента: инвертор НЕ (not), исключающее ИЛИ (xor) и логического умножения И (and).

0 1 0

+

H2 H1 H0

=

8 разряд = H1 and H2

7 разряд = H1 xor H2

6 разряд = not H1

5 разряд = H0

Входной бит переноса в 5-й разряд отсутствует и всегда равен лог. 0. Бит переноса из 5-ого разряда в 6-ой, всегда равен лог.0 и не требуется. Бит переноса из 6-ого разряда в 7-ой равен H1. Бит переноса из 7-ого в 8-й разряд равен H1 and H2 и этому равен сам восьмой разряд.

Картинка: https://cloud.mail.ru/public/Quah/F2FgEPc4k

LE - Логический элемент (Logical element), например, LE_XOR2, двухвходовый логический элемент исключающее ИЛИ (xor).

Прежде всего, в начале проекта необходимо создать простейшие логические элементы, чтобы потом можно было их многократно использовать. Для начала создадим необходимые, а потом можно будет добавить и другие, по мере надобности.

--Logical element LE_XOR2 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_XOR2 is

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end entity LE_XOR2;

architecture Behav_1 of LE_XOR2 is

begin

out_1 <= in_1 xor in_2;

end architecture Behav_1;

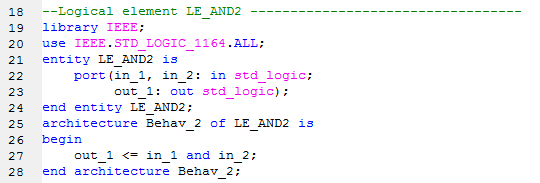

--Logical element LE_AND2 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_AND2 is

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end entity LE_AND2;

architecture Behav_2 of LE_AND2 is

begin

out_1 <= in_1 and in_2;

end architecture Behav_2;

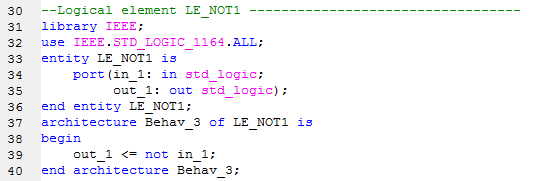

--Logical element LE_NOT1 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_NOT1 is

port(in_1: in std_logic;

out_1: out std_logic);

end entity LE_NOT1;

architecture Behav_3 of LE_NOT1 is

begin

out_1 <= not in_1;

end architecture Behav_3;

--Logical element LE_OR2 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_OR2 is

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end entity LE_OR2;

architecture Behav_4 of LE_OR2 is

begin

out_1 <= in_1 or in_2;

end architecture Behav_4;

Дальнейший расчёт и схемное решение для разрядов 21, 20, 19.

Картинка: https://cloud.mail.ru/public/vZMh/Ybrq19jfD

Дальнейший расчёт и схемное решение для разрядов 31, 30, 29, 28, 27, 26.

Картинка 1: https://cloud.mail.ru/public/ptRy/mKzKWomn3

Картинка 2: https://cloud.mail.ru/public/ku8K/BTod9PM4d

Картинка 3: https://cloud.mail.ru/public/j8XR/L5SqV2Qaj

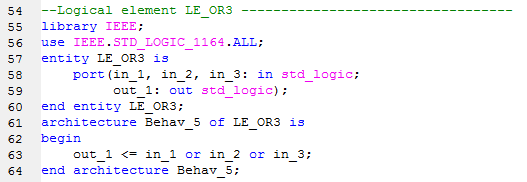

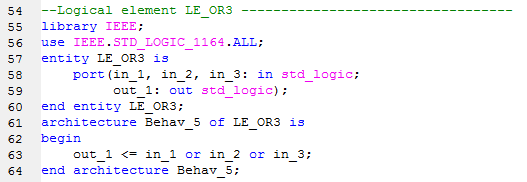

Для реализации нашего компонента, реализующего функции сумматора, в соответствии с схемой, представленной выше, нам потребуются три новых логических элемента: 3ИЛИ (LE_OR3), 4ИЛИ (LE_OR4) и 5ИЛИ (LE_OR5), которых у нас ещё нет в проекте. Поэтому создадим их.

--Logical element LE_OR3 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_OR3 is

port(in_1, in_2, in_3: in std_logic;

out_1: out std_logic);

end entity LE_OR3;

architecture Behav_5 of LE_OR3 is

begin

out_1 <= in_1 or in_2 or in_3;

end architecture Behav_5;

Картинка. Жопа вся в том, что РКП и их приспешники, что-то похерили и мелкие картинки грузятся, а вот на 260 Кб, уже нах посылает, поэтому в виде ссылки:

https://cloud.mail.ru/public/1F6C/uNGuWuKSQ

А хотя я затупил и в формате BMP попытался загнать, а в PNG она уже 8+ Кб весит и вуаля:

Ну и по аналогии, создаём и добавляем в проект ещё два логических элемента:

--Logical element LE_OR4 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_OR4 is

port(in_1, in_2, in_3, in_4: in std_logic;

out_1: out std_logic);

end entity LE_OR4;

architecture Behav_6 of LE_OR4 is

begin

out_1 <= in_1 or in_2 or in_3 or in_4;

end architecture Behav_6;

--Logical element LE_OR5 ----------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity LE_OR5 is

port(in_1, in_2, in_3, in_4, in_5: in std_logic;

out_1: out std_logic);

end entity LE_OR5;

architecture Behav_7 of LE_OR5 is

begin

out_1 <= in_1 or in_2 or in_3 or in_4 or in_5;

end architecture Behav_7;

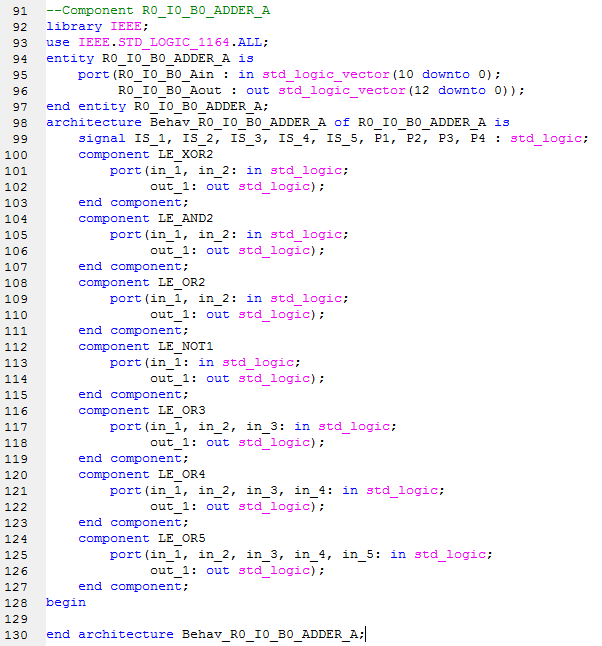

Итак, в нашем компоненте имеется одиннадцать входов (11) и тринадцать выходов (13). Потребуются логические элементы 2И, 2ИЛИ, 3ИЛИ, 4ИЛИ, 5ИЛИ, НЕ, исключающее ИЛИ, которые у нас уже созданы. Осталось написать код.

Название компонента: R0_I0_B0_ADDER_A

R0_I0_B0_Ain : in std_logic_vector(10 downto 0); - Входные 11 сигналов компонента.

R0_I0_B0_Aout : out std_logic_vector(12 downto 0); - Выходные 13 сигналов компонента.

IS_1, IS_2, IS_3, IS_4, IS_5, P1, P2, P3, P4 : std_logic; - Внутренние сигналы.

Основная часть кода компонента готова:

--Component R0_I0_B0_ADDER_A

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity R0_I0_B0_ADDER_A is

port(R0_I0_B0_Ain : in std_logic_vector(10 downto 0);

R0_I0_B0_Aout : out std_logic_vector(12 downto 0));

end entity R0_I0_B0_ADDER_A;

architecture Behav_R0_I0_B0_ADDER_A of R0_I0_B0_ADDER_A is

signal IS_1, IS_2, IS_3, IS_4, IS_5, P1, P2, P3, P4 : std_logic;

component LE_XOR2

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end component;

component LE_AND2

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end component;

component LE_OR2

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end component;

component LE_NOT1

port(in_1: in std_logic;

out_1: out std_logic);

end component;

component LE_OR3

port(in_1, in_2, in_3: in std_logic;

out_1: out std_logic);

end component;

component LE_OR4

port(in_1, in_2, in_3, in_4: in std_logic;

out_1: out std_logic);

end component;

component LE_OR5

port(in_1, in_2, in_3, in_4, in_5: in std_logic;

out_1: out std_logic);

end component;

begin

end architecture Behav_R0_I0_B0_ADDER_A;

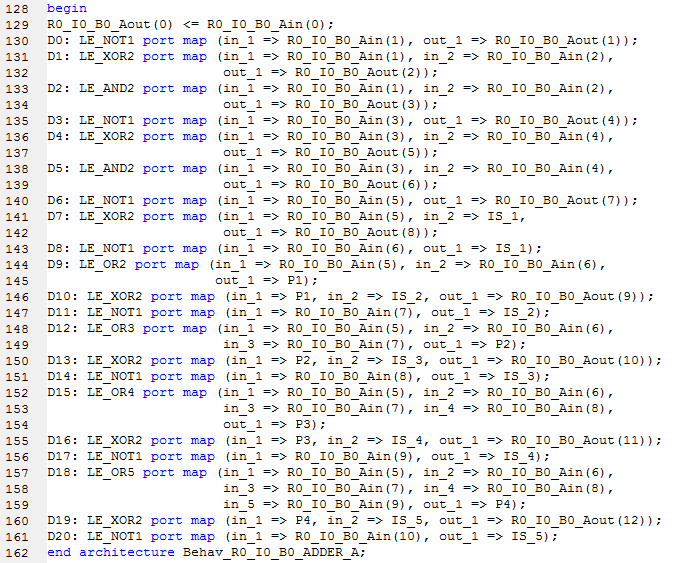

Сама же суть будет находиться после слова begin, а именно, следующее:

R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0);

D0: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(1), out_1 => R0_I0_B0_Aout(1));

D1: LE_XOR2 port map (in_1 => R0_I0_B0_Ain(1), in_2 => R0_I0_B0_Ain(2),

out_1 => R0_I0_B0_Aout(2));

D2: LE_AND2 port map (in_1 => R0_I0_B0_Ain(1), in_2 => R0_I0_B0_Ain(2),

out_1 => R0_I0_B0_Aout(3));

D3: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(3), out_1 => R0_I0_B0_Aout(4));

D4: LE_XOR2 port map (in_1 => R0_I0_B0_Ain(3), in_2 => R0_I0_B0_Ain(4),

out_1 => R0_I0_B0_Aout(5));

D5: LE_AND2 port map (in_1 => R0_I0_B0_Ain(3), in_2 => R0_I0_B0_Ain(4),

out_1 => R0_I0_B0_Aout(6));

D6: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(5), out_1 => R0_I0_B0_Aout(7));

D7: LE_XOR2 port map (in_1 => R0_I0_B0_Ain(5), in_2 => IS_1,

out_1 => R0_I0_B0_Aout(8 ));

D8: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(6), out_1 => IS_1);

D9: LE_OR2 port map (in_1 => R0_I0_B0_Ain(5), in_2 => R0_I0_B0_Ain(6),

out_1 => P1);

D10: LE_XOR2 port map (in_1 => P1, in_2 => IS_2, out_1 => R0_I0_B0_Aout(9));

D11: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(7), out_1 => IS_2);

D12: LE_OR3 port map (in_1 => R0_I0_B0_Ain(5), in_2 => R0_I0_B0_Ain(6),

in_3 => R0_I0_B0_Ain(7), out_1 => P2);

D13: LE_XOR2 port map (in_1 => P2, in_2 => IS_3, out_1 => R0_I0_B0_Aout(10));

D14: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(8 ), out_1 => IS_3);

D15: LE_OR4 port map (in_1 => R0_I0_B0_Ain(5), in_2 => R0_I0_B0_Ain(6),

in_3 => R0_I0_B0_Ain(7), in_4 => R0_I0_B0_Ain(8 ),

out_1 => P3);

D16: LE_XOR2 port map (in_1 => P3, in_2 => IS_4, out_1 => R0_I0_B0_Aout(11));

D17: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(9), out_1 => IS_4);

D18: LE_OR5 port map (in_1 => R0_I0_B0_Ain(5), in_2 => R0_I0_B0_Ain(6),

in_3 => R0_I0_B0_Ain(7), in_4 => R0_I0_B0_Ain(8 ),

in_5 => R0_I0_B0_Ain(9), out_1 => P4);

D19: LE_XOR2 port map (in_1 => P4, in_2 => IS_5, out_1 => R0_I0_B0_Aout(12));

D20: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(10), out_1 => IS_5);

Вот такой у нас получился элемент, ну или точнее компонент:

Внутренняя же структура нашего компонента выглядит так:

Как видно из кода R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0); входной сигнал R0_I0_B0_Ain(0) напрямую проходит на выход, то есть на выходной сигнал R0_I0_B0_Aout(0), но внутри микросхемы ПЛИС напрямую ничего не проходит, только через входные и выходные буферы, что мы и можем наблюдать на внутренней схеме компонента, а именно:

И проанализировав, приходим к выводу, что от этой строчки в коде:

R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0);

нам нужно избавиться, так как мы просто тратим два буфера, входной и выходной и ничего более, а подавать сразу на выход 5-й разряд числа W[0], то есть W0-5. И даже не на выход, а на вход первой итерации.

Что же мы имеем в результате на выходе (R0_I0_B0):

|++++ ++ПП | 00P+ +ППП | 1000 100P |+++0 1101|

Разряд 0: 1

Разряд 1: 0

Разряд 2: 1

Разряд 3: 1

Разряд 4: 0

Разряд 5: S5 (R0_I0_B0_Aout(0))

Разряд 6: S6 (R0_I0_B0_Aout(1))

Разряд 7: S7 (R0_I0_B0_Aout(2))

Разряд 8: S8 (R0_I0_B0_Aout(3))

Разряд 9: 0

Разряд 10: 0

Разряд 11: 1

Разряд 12: 0

Разряд 13: 0

Разряд 14: 0

Разряд 15: 1

Разряд 16: П W0-16

Разряд 17: П W0-17

Разряд 18: П W0-18

Разряд 19: S19 (R0_I0_B0_Aout(4))

Разряд 20: S20 (R0_I0_B0_Aout(5))

Разряд 21: S21 (R0_I0_B0_Aout(6))

Разряд 22: 0

Разряд 23: 0

Разряд 24: П W0-24

Разряд 25: П W0-25

Разряд 26: S26 (R0_I0_B0_Aout(7))

Разряд 27: S27 (R0_I0_B0_Aout(8 ))

Разряд 28: S28 (R0_I0_B0_Aout(9))

Разряд 29: S29 (R0_I0_B0_Aout(10))

Разряд 30: S30 (R0_I0_B0_Aout(11))

Разряд 31: S31 (R0_I0_B0_Aout(12))

Итак, подправим код и избавимся от строчки: R0_I0_B0_Aout(0) <= R0_I0_B0_Ain(0);

Естественно станет меньше на один входной и выходной сигнал:

R0_I0_B0_Ain : in std_logic_vector(9 downto 0); - Входные 10 сигналов компонента.

R0_I0_B0_Aout : out std_logic_vector(11 downto 0); - Выходные 12 сигналов компонента.

|++++ ++ПП | 00P+ +ППП | 1000 100P |++П0 1101|

Разряд 0: 1

Разряд 1: 0

Разряд 2: 1

Разряд 3: 1

Разряд 4: 0

Разряд 5: W0-5

Разряд 6: S6 (R0_I0_B0_Aout(0))

Разряд 7: S7 (R0_I0_B0_Aout(1))

Разряд 8: S8 (R0_I0_B0_Aout(2))

Разряд 9: 0

Разряд 10: 0

Разряд 11: 1

Разряд 12: 0

Разряд 13: 0

Разряд 14: 0

Разряд 15: 1

Разряд 16: П W0-16

Разряд 17: П W0-17

Разряд 18: П W0-18

Разряд 19: S19 (R0_I0_B0_Aout(3))

Разряд 20: S20 (R0_I0_B0_Aout(4))

Разряд 21: S21 (R0_I0_B0_Aout(5))

Разряд 22: 0

Разряд 23: 0

Разряд 24: П W0-24

Разряд 25: П W0-25

Разряд 26: S26 (R0_I0_B0_Aout(6))

Разряд 27: S27 (R0_I0_B0_Aout(7))

Разряд 28: S28 (R0_I0_B0_Aout(8 ))

Разряд 29: S29 (R0_I0_B0_Aout(9))

Разряд 30: S30 (R0_I0_B0_Aout(10))

Разряд 31: S31 (R0_I0_B0_Aout(11))

И изменённый код:

--Component R0_I0_B0_ADDER_A

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity R0_I0_B0_ADDER_A is

port(R0_I0_B0_Ain : in std_logic_vector(9 downto 0);

R0_I0_B0_Aout : out std_logic_vector(11 downto 0));

end entity R0_I0_B0_ADDER_A;

architecture Behav_R0_I0_B0_ADDER_A of R0_I0_B0_ADDER_A is

signal IS_1, IS_2, IS_3, IS_4, IS_5, P1, P2, P3, P4 : std_logic;

component LE_XOR2

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end component;

component LE_AND2

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end component;

component LE_OR2

port(in_1, in_2: in std_logic;

out_1: out std_logic);

end component;

component LE_NOT1

port(in_1: in std_logic;

out_1: out std_logic);

end component;

component LE_OR3

port(in_1, in_2, in_3: in std_logic;

out_1: out std_logic);

end component;

component LE_OR4

port(in_1, in_2, in_3, in_4: in std_logic;

out_1: out std_logic);

end component;

component LE_OR5

port(in_1, in_2, in_3, in_4, in_5: in std_logic;

out_1: out std_logic);

end component;

begin

D0: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(0), out_1 => R0_I0_B0_Aout(0));

D1: LE_XOR2 port map (in_1 => R0_I0_B0_Ain(0), in_2 => R0_I0_B0_Ain(1),

out_1 => R0_I0_B0_Aout(1));

D2: LE_AND2 port map (in_1 => R0_I0_B0_Ain(0), in_2 => R0_I0_B0_Ain(1),

out_1 => R0_I0_B0_Aout(2));

D3: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(2), out_1 => R0_I0_B0_Aout(3));

D4: LE_XOR2 port map (in_1 => R0_I0_B0_Ain(2), in_2 => R0_I0_B0_Ain(3),

out_1 => R0_I0_B0_Aout(4));

D5: LE_AND2 port map (in_1 => R0_I0_B0_Ain(2), in_2 => R0_I0_B0_Ain(3),

out_1 => R0_I0_B0_Aout(5));

D6: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(4), out_1 => R0_I0_B0_Aout(6));

D7: LE_XOR2 port map (in_1 => R0_I0_B0_Ain(4), in_2 => IS_1,

out_1 => R0_I0_B0_Aout(7));

D8: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(5), out_1 => IS_1);

D9: LE_OR2 port map (in_1 => R0_I0_B0_Ain(4), in_2 => R0_I0_B0_Ain(5),

out_1 => P1);

D10: LE_XOR2 port map (in_1 => P1, in_2 => IS_2, out_1 => R0_I0_B0_Aout(8 ));

D11: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(6), out_1 => IS_2);

D12: LE_OR3 port map (in_1 => R0_I0_B0_Ain(4), in_2 => R0_I0_B0_Ain(5),

in_3 => R0_I0_B0_Ain(6), out_1 => P2);

D13: LE_XOR2 port map (in_1 => P2, in_2 => IS_3, out_1 => R0_I0_B0_Aout(9));

D14: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(7), out_1 => IS_3);

D15: LE_OR4 port map (in_1 => R0_I0_B0_Ain(4), in_2 => R0_I0_B0_Ain(5),

in_3 => R0_I0_B0_Ain(6), in_4 => R0_I0_B0_Ain(7),

out_1 => P3);

D16: LE_XOR2 port map (in_1 => P3, in_2 => IS_4, out_1 => R0_I0_B0_Aout(10));

D17: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(8 ), out_1 => IS_4);

D18: LE_OR5 port map (in_1 => R0_I0_B0_Ain(4), in_2 => R0_I0_B0_Ain(5),

in_3 => R0_I0_B0_Ain(6), in_4 => R0_I0_B0_Ain(7),

in_5 => R0_I0_B0_Ain(8 ), out_1 => P4);

D19: LE_XOR2 port map (in_1 => P4, in_2 => IS_5, out_1 => R0_I0_B0_Aout(11));

D20: LE_NOT1 port map (in_1 => R0_I0_B0_Ain(9), out_1 => IS_5);

end architecture Behav_R0_I0_B0_ADDER_A;

Maximum combinational path delay: 8.451ns - в случае размещения в Spartan-3 (XC3S200A-4VQ100).

Вот теперь замечательно, есть инвертор и он обрамлён входным и выходным буфером:

.

Последний раз редактировалось: Viktor2312 (Сб Янв 22 2022, 15:58), всего редактировалось 10 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

R0_I0_B0_ADDER_E

R0_I0_B0_ADDER_E

4

Схема модуля R0_I0_B0_ADDER_A.

Резервная копия: https://cloud.mail.ru/public/ZxSW/LDKeshx6J

R0_I0_B0_ADDER_A

Резервная копия: https://cloud.mail.ru/public/xwXQ/1FchRXtt8

Выходные данные числа А, итерация 0 / Входные данные числа А, итерация 1.

Резервная копия: https://cloud.mail.ru/public/sZxC/CDf7tKWXV

.

Резервная копия: https://cloud.mail.ru/public/ZxSW/LDKeshx6J

R0_I0_B0_ADDER_A

Резервная копия: https://cloud.mail.ru/public/xwXQ/1FchRXtt8

Выходные данные числа А, итерация 0 / Входные данные числа А, итерация 1.

Резервная копия: https://cloud.mail.ru/public/sZxC/CDf7tKWXV

.

Последний раз редактировалось: Viktor2312 (Сб Янв 22 2022, 17:32), всего редактировалось 3 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

5

Кину сюда, чтобы колёсико мышки не сильно насиловать:

|*|GGGG|GGGG|*|XXXG|GGGG|*|XXXX|XXXX|*|HHHX|XXXX|*|

|*|7,6,5,4|3,2,1,0|*|2,1,0,12|11,10,9,8|*|10,9,8,7|6,5,4,3|*|H,H,H,15|14,13,12,11|*|

E = 0x98C7E2A2 + W[0]

Поле поиска имеет значение: 0x0000

П - повторитель.

P - бит переноса.

| 1001 1000 | 1100 0111 | 1110 0010 | 1010 0010 | = E

+

| GGGG GGGG | 000G GGGG |0000 0000 | HHH0 0000 | = W[0]

=

| ++++ +ППП | 11P+ ++++ | 1110 001P | +++0 0000 |

.

|*|GGGG|GGGG|*|XXXG|GGGG|*|XXXX|XXXX|*|HHHX|XXXX|*|

|*|7,6,5,4|3,2,1,0|*|2,1,0,12|11,10,9,8|*|10,9,8,7|6,5,4,3|*|H,H,H,15|14,13,12,11|*|

E = 0x98C7E2A2 + W[0]

Поле поиска имеет значение: 0x0000

П - повторитель.

P - бит переноса.

| 1001 1000 | 1100 0111 | 1110 0010 | 1010 0010 | = E

+

| GGGG GGGG | 000G GGGG |0000 0000 | HHH0 0000 | = W[0]

=

| ++++ +ППП | 11P+ ++++ | 1110 001P | +++0 0000 |

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» HM-SHA256-v1. Теория.

» HM-SHA256-FPGA_v001. R0_I1_B0.

» HM-SHA256-FPGA_v001. Main.

» HM-SHA256-SMD-v1. 001_Детали, Datasheet.

» HM-SHA256-SMD-v1. 004_Обсуждение, флейм.

» HM-SHA256-FPGA_v001. R0_I1_B0.

» HM-SHA256-FPGA_v001. Main.

» HM-SHA256-SMD-v1. 001_Детали, Datasheet.

» HM-SHA256-SMD-v1. 004_Обсуждение, флейм.

RUЭВМ :: Отечественные ЭВМ, ПЭВМ и МВК :: _______вход :: HM-SHA256-FPGA_v001 :: HM-SHA256-FPGA_v001. R0_I0...63_B0+ADDER

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|