Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

HM-SHA256-DIP-v1. (74AC) МФДС - Модули формирования дополнительных слов.

Страница 1 из 1 • Поделиться

HM-SHA256-DIP-v1. (74AC) МФДС - Модули формирования дополнительных слов.

HM-SHA256-DIP-v1. (74AC) МФДС - Модули формирования дополнительных слов.

1

HM-SHA256-DIP-v1. Прототип на микросхемах 74ACxxx от TI (DIP).

(74AC) МФДС - Модули формирования дополнительных слов.

(74AC) МФДС - Модули формирования дополнительных слов.

Данная тема посвящена модулям формирования дополнительных слов. Логично, да.

Как известно, после предварительной обработки message и разбития сообщения на части по 512 бит, можно приступать к вычислениям. Хотя, на самом деле конечно же и раньше... Но это сейчас не важно. Главное, что после того, как мы получаем наш кусок в 512 бит, то мы имеем 16 слов от w[0] до w[15]. И из этих слов необходимо сформировать дополнительные 48 слов, что в сумме даёт нам 64 слова от w[0] до w[63] по одному слову для каждой итерации, нулевое слово для нулевой итерации и т. д... до 63-й.

Формируются они следующим образом:

----------------------------------------------------------------------------------------------

Сгенерировать дополнительные 48 слов:

для i от 16 до 63

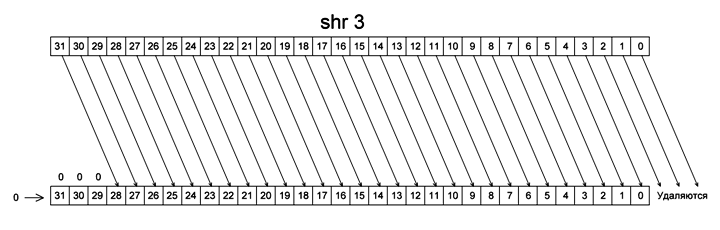

s0 := (w[i-15] rotr 7) xor (w[i-15] rotr 18) xor (w[i-15] shr 3)

s1 := (w[i-2] rotr 17) xor (w[i-2] rotr 19) xor (w[i-2] shr 10)

w[i] := w[i-16] + s0 + w[i-7] + s1

Все переменные беззнаковые, имеют размер 32 бита.

+ — сложение, суммирование по модулю 232.

xor — исключающее «ИЛИ».

shr (shift right) — логический сдвиг вправо.

rotr (rotate right) — циклический сдвиг вправо.

----------------------------------------------------------------------------------------------

Что тут главного, во-первых, то, что у нас есть готовые 16 слов. В момент времени t0 с регистров, где они предварительно были сохранены, выдаются в систему эти 16 слов. Они поступают как готовые данные для первых 16-ти итераций (от 0 до 15). Что это даёт нам? В первую очередь время, у нас есть свободное время для спокойного и не спешного формирования дополнительных слов, равное времени вычисления первых 16 итераций. Во-вторых, мы можем вычислять их относительно параллельно. Главное помнить, я бы даже сказал детское правило, от перемены мест слагаемых сумма не меняется. И как видно из третьей строчки, где мы окончательно вычисляем значение слова, мы можем сразу приступать к сложению. Например, при нахождении 16-го слова мы имеем: w[16 - 16] + w[16 - 7] + s0 + s1, что соответственно равно: w[0] + w[9] + ... То есть нам нужно сложить нулевое и девятое слово, при этом нам не нужно разрабатывать супер быстрый параллельный сумматор с параллельным переносом и применять скоростную логику и при этом мы ещё можем параллельно, одновременно вычислять значения s0 и s1. И в третьих, при нахождении s1 мы можем сэкономить логические элементы, это можно было бы сделать и при нахождении s0, но всё зависит от того, сколько логических элементов в микросхеме. При реализации внутри микросхемы ПЛИС, мы можем сэкономить все 13 логических элементов три на shr 3 и десять на shr 10. А вот при реализации на микросхемах, например серии 74AC, уже так не получится, микросхему придётся ставить из-за одного необходимого логического элемента, и тут проще уже и оставшиеся три использовать, чтобы не создавать лишний разброс по времени, а вот при нахождении s1 мы можем сэкономить 2 микросхемы, что существенно, при реализации всех 48 блоков, это экономит 96 микросхем, вся экономия заключается в том, что shr, логический сдвиг вправо, даёт нам слева известное количество нулей, а как известно, что если на один из входов логического элемента "Исключающее ИЛИ" или иными словами сумматора по модулю два, подан лог. 0, то он превращается в повторитель, то есть что вошло, то и вышло, то есть его можно просто выкинуть из схемы. Вот собственно и все предварительные наброски, всё просто, элементарно но, объёмно по "железу", зато можно получить все 48 слов относительно быстро...

Далее будет процесс, медленный, нудный, с черчением схем, разработкой печатных плат, и т. д. То есть по сути всё тот же процесс по созданию прототипа, денег конечно на платы нет, как и на детали, поэтому улитка по прежнему буксует...

А пока из предварительного, все модули будут разрабатываться для серии 74AC и без какого бы то ни было поверхностного монтажа, не хочу плеваться и материться при сборке и вообще травмировать свою детскую нежную и не окрепшую психику. К тому же, это позволит использовать панельки под микросхемы, что важно для прототипа...

Для s0:

- Спойлер:

Для s1:

- Спойлер:

Datasheet:

74AC86 (ЛП5)

74AC283 (ИМ6)

DIN41612 (разъёмы)

DS1073-01-2x2-MR2T6

- Спойлер:

Продолжение в следующем посте...

Последний раз редактировалось: Viktor2312 (Ср Мар 16 2022, 00:00), всего редактировалось 8 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

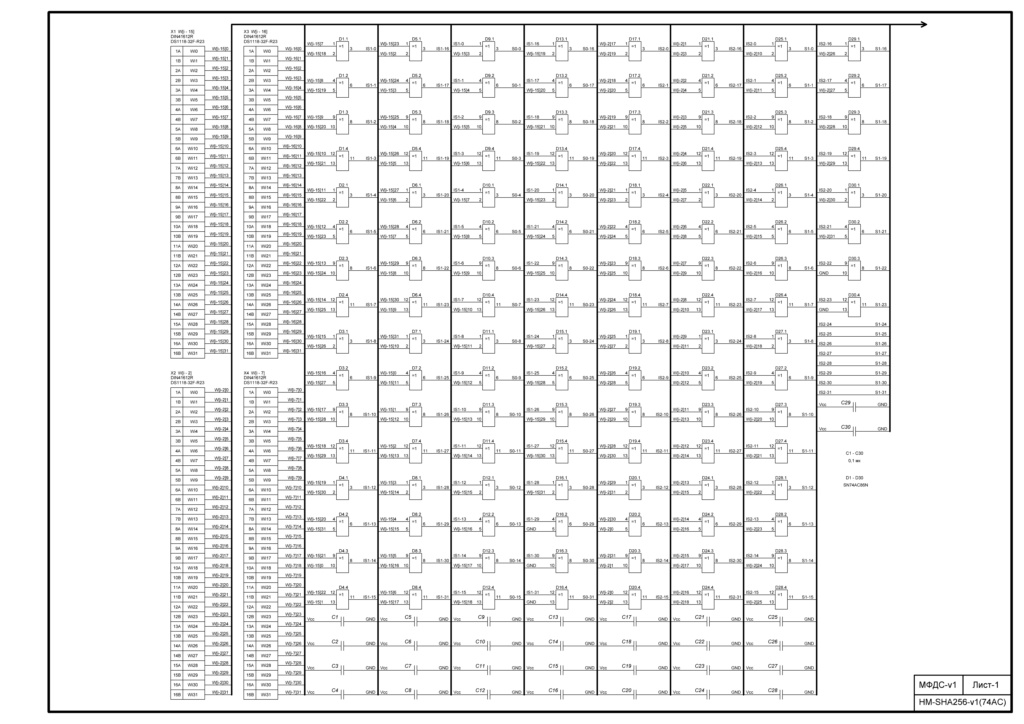

Схема.

Схема.

2

Схема.

Ниже будет представлена электрическая принципиальная схема, базового модуля (74AC) МФДС_v1

Краткое описание. На разъём X6 подаётся напряжение питания. Оно может быть в диапазоне 3,3...5,5 В. При напряжении 3,3 В схема имеет минимальное быстродействие, при 5,5 В, соответственно, максимальное. Главное, что если выбрано напряжение 3,3 В то оно должно быть таковым для всей схемы майнера и т. д. На разъёмы X1, X2, X3, X4 подаются входные слова для обработки и получения искомого слова, которое снимается с разъёма X5. Количество микросхем SN74AC86N можно было сократить ещё на одну, но я решил этого не делать, чтобы упростить разводку печатной платы, оставить симметрию, и для прототипа, это не критично. Как видно из схемы, сумматоры применяются обычные параллельные сумматоры с параллельным переносом внутри тетрады, перенос же между тетрадами последовательный. Применение стандартной схемы и как следствие низкое быстродействие для нас не критично, так как есть необходимый запас по времени. Циклические и логические сдвиги производятся при помощи соответствующей разводки сигналов, при помощи обычного печатного монтажа.

Лист-0.

Лист-1.

Лист-2

Теперь можно приступать к разработке печатной платы и накоплению радиодеталей. Так как для первого блока потребуется 48 печатных плат, в виду того, что все 16 слов нам не известны. А вот для второго блока из 512 слов, которые будут иметь дополнение и как следствие много слов с нулевым значением, всё намного упростится. Так как чётко известно, что Х + 0 = Х или 0 + 0 = 0, что очень сильно упростит схему, но не процесс разработки. Конечно можно было бы тупо тоже применить 48 плат, но зачем, чтобы нули складывать с числами и нули с нулями и впустую расходовать "железо" и электроэнергию...

.

Ниже будет представлена электрическая принципиальная схема, базового модуля (74AC) МФДС_v1

Краткое описание. На разъём X6 подаётся напряжение питания. Оно может быть в диапазоне 3,3...5,5 В. При напряжении 3,3 В схема имеет минимальное быстродействие, при 5,5 В, соответственно, максимальное. Главное, что если выбрано напряжение 3,3 В то оно должно быть таковым для всей схемы майнера и т. д. На разъёмы X1, X2, X3, X4 подаются входные слова для обработки и получения искомого слова, которое снимается с разъёма X5. Количество микросхем SN74AC86N можно было сократить ещё на одну, но я решил этого не делать, чтобы упростить разводку печатной платы, оставить симметрию, и для прототипа, это не критично. Как видно из схемы, сумматоры применяются обычные параллельные сумматоры с параллельным переносом внутри тетрады, перенос же между тетрадами последовательный. Применение стандартной схемы и как следствие низкое быстродействие для нас не критично, так как есть необходимый запас по времени. Циклические и логические сдвиги производятся при помощи соответствующей разводки сигналов, при помощи обычного печатного монтажа.

Лист-0.

- Спойлер:

Лист-1.

- Спойлер:

Лист-2

- Спойлер:

Теперь можно приступать к разработке печатной платы и накоплению радиодеталей. Так как для первого блока потребуется 48 печатных плат, в виду того, что все 16 слов нам не известны. А вот для второго блока из 512 слов, которые будут иметь дополнение и как следствие много слов с нулевым значением, всё намного упростится. Так как чётко известно, что Х + 0 = Х или 0 + 0 = 0, что очень сильно упростит схему, но не процесс разработки. Конечно можно было бы тупо тоже применить 48 плат, но зачем, чтобы нули складывать с числами и нули с нулями и впустую расходовать "железо" и электроэнергию...

.

Последний раз редактировалось: Viktor2312 (Чт Авг 26 2021, 10:35), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

3

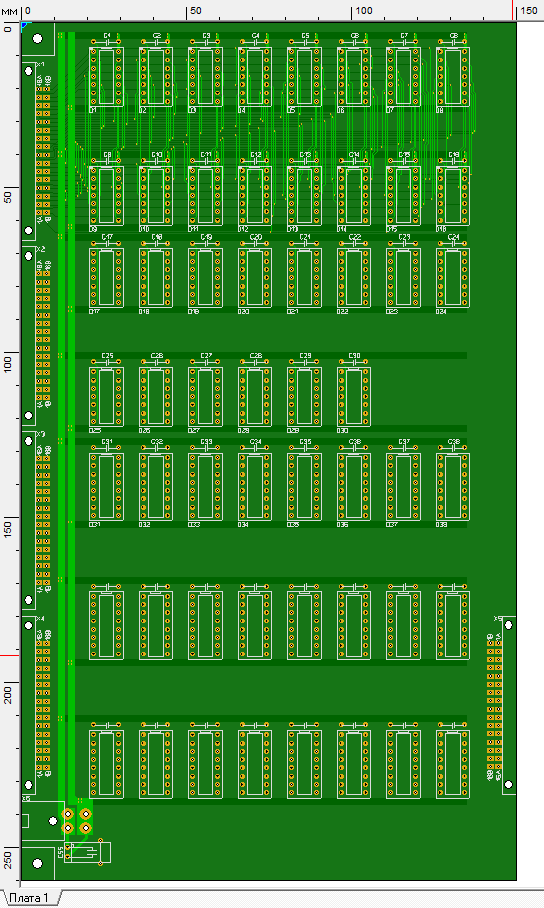

Процесс разработки печатной платы, базового модуля МФДС.

Начало разработки печатной платы:

- Спойлер:

26.08.2021г.

Промежуточный этап разработки. Закончил 1,2 и 3-й этапы из 5. Процесс идёт отлично, поступательно. Внешний вид на данный момент:

- Спойлер:

18.11.2021г.

Решил делать всё в виде идентичных модулей с размерами 150 х 150 мм, поэтому плата выше заброшена, но начата разработка новой. Сейчас, прямо сейчас, разрабатываю модуль для формирования слов S0 и S1, а на второй платке будет уже три 32-разрядных сумматора, по классической схеме, без ускорения, так как оно тут не требуется, есть запас по времени, аж в целых 16 итераций.

В общем прямо сейчас и происходят, те самые, почти зимние, тёмные вечера, хотя у меня и ночи и дни. В принципе для этого модуля не хватает на данный момент, до-разработать плату и заказать её изготовление, и купить 30 шт. микросхем SN74AC86N.

В общим процесс идёт просто отлично, вот тут можно глянуть как платка выглядит сейчас, закончил все подготовительные мероприятия, на 90% и дописав этот пост, сажусь за разработку, ухожу так сказать с головой в разработку платы. Вот тут: https://cloud.mail.ru/public/ADiA/wTkymTvDs

.

Последний раз редактировалось: Viktor2312 (Чт Ноя 18 2021, 11:28), всего редактировалось 3 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: HM-SHA256-DIP-v1. (74AC) МФДС - Модули формирования дополнительных слов.

Re: HM-SHA256-DIP-v1. (74AC) МФДС - Модули формирования дополнительных слов.

4

Детали.

Начал потихоньку подготавливать детали для сборки модулей. Вывел сегодня в фиат, то что напосил кошелёк BARE, 1/3 конечно я потратил в кафешке, после того как купил детали, покушал пельмешки, салатики, под 100г. водочки, попил Чешского пивка, Веталь какашка срулил гулять в Железноводск с женой и отпрысками, ну а я устав от разработки платы, ха.. я сегодня аж 4 сигнала развёл от X2 16B, 16A, 15B, 15A и чутка питания...

ха.. я сегодня аж 4 сигнала развёл от X2 16B, 16A, 15B, 15A и чутка питания...

Сходил сегодня в ЮТ, немного втарился. Тут ниже постом буду вести подсчёт расходов.

.

Начал потихоньку подготавливать детали для сборки модулей. Вывел сегодня в фиат, то что напосил кошелёк BARE, 1/3 конечно я потратил в кафешке, после того как купил детали, покушал пельмешки, салатики, под 100г. водочки, попил Чешского пивка, Веталь какашка срулил гулять в Железноводск с женой и отпрысками, ну а я устав от разработки платы,

Сходил сегодня в ЮТ, немного втарился. Тут ниже постом буду вести подсчёт расходов.

- Спойлер:

- Спойлер:

.

Последний раз редактировалось: Viktor2312 (Чт Авг 26 2021, 10:32), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

5

Расходы.

.

- Панельки SCS-14, SCS-16.

Блокировочные конденсаторы, 0,1мк х 50В

Электролитические конденсаторы, 10мк х 35В555 руб.

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

6

Да, печально, всё очень печально... Подумал я вот так вот, оценил объёмы, габариты, расходы.

Не получится ничего...

Ну нету у меня папика который за всё это будет платить, а мои скромные гроши.., да можно и не пыжиться...

Поэтому проект реализации майнера на серии 74AC приостановлен.

Пойду ковырять на Си... Ну тут вообще жопа. Мало того что я этот язык до недавнего времени терпеть не мог, а изучение проходило тяжко, так и то что изучил, забылось. Правильно говорил, один человек, человеческий мозг как динамическая память, не регенерировал, учи заново, читал я свои же наработки, недавно, пару дней назад, - как баран на новые ворота... Но, вариантов других нет...

Эххх... Поковырял я Си, и убедился в своих выводах ещё раз, даже i9-12xxx с его 16 ядрами, 24 потоками и на частоте 5,2 ГГц, это просто тормоз по сравнению с реализацией на 74ACxxx серии микросхем. Ни а каком серьёзном параллелизме там говорить не приходится...

Серии конечно придётся совмещать, там где скорость не нужна, можно 74AC но в SMD исполнении, иначе никак, и то громоздко, в критически важных местах, только Tiny logic, иначе это всё, будет огромно и медленно, ПЛИС - тут нужна помощь друга, но таких нетути. Решил вернуться к реализации проекта, учитывая новые знания, полученные за этот промежуток времени, от предыдущего поста, но нужно будет извращаться, симметрия - враг компактности... Многое обдумано, изучено, пересмотрено, и иии... картинка же не загрузится, учитывая Soft попытки, стало понятно, что только по-битное разложение может дать результат...

Медленно:

Зато заголовок красивый... ИМХО.

Суки ..., всё похерили, ни... картинки не грузятся, ...e РКП. Ну, тогда только ссылка на картинку в их подконтрольное облако, которое ещё предстоит засрать говном.

Как это всё зa...

https://cloud.mail.ru/public/ah8m/teFY73huE

Даже нить потерял... Уроды.

Короче буду ковырять дальше, но с "второго" раунда, то бишь первого, у нас же есть раунд 0 и 1...

18.11.2021г.

.

Не получится ничего...

Ну нету у меня папика который за всё это будет платить, а мои скромные гроши.., да можно и не пыжиться...

Поэтому проект реализации майнера на серии 74AC приостановлен.

Пойду ковырять на Си... Ну тут вообще жопа. Мало того что я этот язык до недавнего времени терпеть не мог, а изучение проходило тяжко, так и то что изучил, забылось. Правильно говорил, один человек, человеческий мозг как динамическая память, не регенерировал, учи заново, читал я свои же наработки, недавно, пару дней назад, - как баран на новые ворота... Но, вариантов других нет...

-------------------------------------------------------------------------

Поэтому проект реализации майнера на серии 74AC приостановлен.

Эххх... Поковырял я Си, и убедился в своих выводах ещё раз, даже i9-12xxx с его 16 ядрами, 24 потоками и на частоте 5,2 ГГц, это просто тормоз по сравнению с реализацией на 74ACxxx серии микросхем. Ни а каком серьёзном параллелизме там говорить не приходится...

Серии конечно придётся совмещать, там где скорость не нужна, можно 74AC но в SMD исполнении, иначе никак, и то громоздко, в критически важных местах, только Tiny logic, иначе это всё, будет огромно и медленно, ПЛИС - тут нужна помощь друга, но таких нетути. Решил вернуться к реализации проекта, учитывая новые знания, полученные за этот промежуток времени, от предыдущего поста, но нужно будет извращаться, симметрия - враг компактности... Многое обдумано, изучено, пересмотрено, и иии... картинка же не загрузится, учитывая Soft попытки, стало понятно, что только по-битное разложение может дать результат...

Медленно:

Зато заголовок красивый... ИМХО.

Суки ..., всё похерили, ни... картинки не грузятся, ...e РКП. Ну, тогда только ссылка на картинку в их подконтрольное облако, которое ещё предстоит засрать говном.

Как это всё зa...

https://cloud.mail.ru/public/ah8m/teFY73huE

Даже нить потерял... Уроды.

Короче буду ковырять дальше, но с "второго" раунда, то бишь первого, у нас же есть раунд 0 и 1...

-------------------------------------------------------------------------

18.11.2021г.

Хандра закончилась, всё обдумано, и снова в бой. Процесс продолжается !!!

.

Последний раз редактировалось: Viktor2312 (Чт Ноя 18 2021, 11:10), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

7

резерв.

Последний раз редактировалось: Viktor2312 (Сб Ноя 06 2021, 03:05), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» Совместимость EPM7000s и 74AC/ACT

» Модули для ПЭВМ "Поиск" (Вххх)

» Схемы ПЭВМ "Океан-240" и дополнительных контроллеров и устройств

» HM-SHA256-v1. Теория.

» HM-SHA256-FPGA_v001. R0_I1_B0.

» Модули для ПЭВМ "Поиск" (Вххх)

» Схемы ПЭВМ "Океан-240" и дополнительных контроллеров и устройств

» HM-SHA256-v1. Теория.

» HM-SHA256-FPGA_v001. R0_I1_B0.

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|