Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Изучение микропроцессорного комплекта КР580, практика и теория...

Страница 1 из 1 • Поделиться

Изучение микропроцессорного комплекта КР580, практика и теория...

Изучение микропроцессорного комплекта КР580, практика и теория...

1

.

____Данная тема создана для изучения, сбора информации и практической реализации вычислительной системы используя, в основном, микросхемы данного микропроцессорного комплекта.

____Основной, и пожалуй самой важной микросхемой, в микропроцессорном комплекте КР580, является микропроцессор или иными словами центральная процессорная единица (CPU). Микросхема БИС КР580ВМ80А представляет собой 8-разрядный микропроцессор, в котором совмещены операционное и управляющее устройства. Управляющая память недоступна пользователю, в ней уже в процессе изготовления микросхемы БИС записываются микропрограммы операций (микропрограммы, по которым выполняются команды). Таким образом, предусматривается использование некоторой фиксированной системы команд, в которую пользователь не может внести изменений. В связи с этим данный микропроцессор относится к числу немикропрограммируемых, т. е. программируемых не на уровне микрокоманд, а на уровне команд.

____Комплект микросхем серии КР580, выполнен по n-МДП-технологии и ТТЛШ-технологии, характеризуется архитектурным единством, которое обеспечивается автономностью и функциональной законченностью отдельных микросхем, унификацией их интерфейса, программируемостью микросхем, их логической и электрической совместимостью.

____Необходимыми микросхемами в любой системе являются: микропроцессор КР580ВМ80А, тактовый генератор КР580ГФ24, системный контроллер КР580ВК28, буферная схема адреса, построенная на двух микросхемах КР580ВА86 для обеспечения нагрузочной способности по шине адреса. Объём памяти запоминающего устройства и использование одной или нескольких периферийных микросхем определяет пользователь.

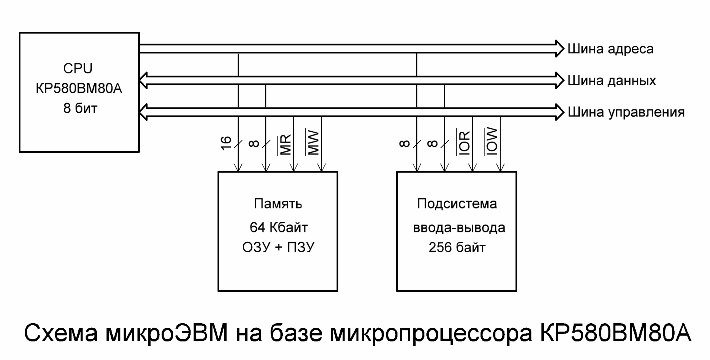

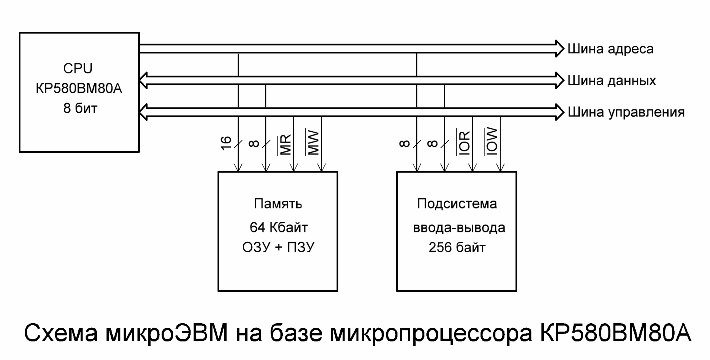

____Микропроцессорная система имеет системную шину, образуемую из трёх шин: шина адреса А15 - А0, шина данных D7 - D0 и шина управления. Системная шина позволяет строить микропроцессорную систему по модульному принципу: модуль центрального процессора, модуль запоминающего устройства, модуль устройств ввода-вывода и т. д. Каждый модуль может содержать собственные буферные схемы адреса и данных.

____Магистральная структура микропроцессорной системы позволяет подключать микросхемы запоминающих устройств общей ёмкостью до 64 Кбайт и микросхемы устройств ввода-вывода до 256 каналов ввода и до 256 каналов вывода.

____Для помехоустойчивости системы низкочастотные помехи по цепи питания необходимо блокировать конденсатором суммарной ёмкостью из расчёта 0,1 мкФ на каждую микросхему, включённым между шинами +5 В и GND непосредственно в начале шины +5 В.

____Высокочастотные помехи необходимо блокировать конденсатором ёмкостью 0,015 - 0,022 мкФ, включённым между каждым выводом +5 В микросхемы и шиной GND в непосредственной близости от микросхем (не далее 5 мм).

____Для увеличения быстродействия системы трёхстабильные линии шины адреса и данных необходимо подключать к шине +5 В через резисторы сопротивлением 2,2 кОм.

____Характеристики микропроцессора КР580ВМ80А однозначно определяют архитектуру устройств, построенных на его основе. Фиксированная разрядность (8 двоичных разрядов), обработка слов, кратных байту, система команд, включающая широкий набор арифметических, логических команд, команд управления и пересылок, а также узел обработки прерываний и развитый интерфейс, определяют применение микропроцессора КР580ВМ80А как центрального процессорного устройства обработки данных.

____Для работы микропроцессора КР580ВМ80А применяется три источника питания: -5 В (ток потребления менее 1 мА), +5 В (ток потребления менее 70 мА) и +12 В (ток потребления менее 50 мА). Кристалл микропроцессора, содержащий около 5000 транзисторов, помещён в корпус с двухрядным расположением 40 выводов и шагом 2,5 мм между ними, типа 2123.40-2. Синхронизация микропроцессора осуществляется от двухфазного внешнего тактового генератора КР580ГФ24, амплитуда тактовых импульсов которого 12В.

____На рисунке ниже приведена базовая структурная схема микропроцессорной системы, построенной на базе микропроцессора КР580ВМ80А.

____В системе используется общая для хранения программ и данных основная память ёмкостью 64 Кбайт и подсистема ввода-вывода ёмкостью 256 байт. Двунаправленная 8-разрядная шина данных, 16-разрядная шина адреса и шина управления служат для организации побайтового обмена между отдельными модулями системы.

____Микропроцессор содержит внутреннее регистровое СОЗУ с организацией 6 х 8 или 3 х 16, а также средства, позволяющие организовать в любой зоне внешней памяти стек объёмом до 64 Кбайт. Это даёт возможность обрабатывать программы практически с неограниченным числом вложений. Микропроцессор имеет средства обслуживания 8-уровневых запросов прерываний, средства управления в режимах ожидания и прямого доступа к памяти, что позволяет осуществлять обмен с внешними устройствами любого быстродействия.

____Структура микропроцессора ориентирована на работу с памятью, имеющую байтовую организацию. Формат обрабатываемых данных имеет вид:

____Байт в зависимости от типа обрабатывающей команды можно интерпретировать следующим образом:

____как целое положительное число без знака в прямом коде. В этом случае числа изменяются в диапазоне

0 - 255:

____как число со знаком в дополнительном коде. Старший бит числа при этом считается знаковым и кодируется 0 для положительных чисел и 1 - для отрицательных. Остальные семь разрядов определяют величину числа. Числа изменяются в диапазоне от +127 до -128:

____как двухразрядное двоично-десятичное число без знака. Старшие разряды D7 - D4 при этом определяют старший двоично-десятичный разряд, а младшие D3 - D0 определяют младший двоично-десятичный разряд. Диапазон представления чисел 0 - 99:

____как логический байт данных.

____Для выполнения некоторых операций допускается представление чисел в 2-байтовом формате в прямом или дополнительном коде. Числа при этом изменяются в диапазоне от +32 767 до -32 768.

____Арифметические операции - сложение, вычитание, инкремент, декремент выполняются по правилам двоичной арифметики над числами в дополнительном коде. Для обработки двоично-десятичных чисел имеется возможность преобразования результата в двоично-десятичный код. Логические операции И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕ, сдвиги - выполняются по правилам двоичной логики. Результат операции представляется числом в соответствующем формате и байтом признаков результата, вместе они образуют слово состояния PSW.

____С точки зрения пользователя и разработчика центрального процессора микроЭВМ важнейшими являются сведения о системе команд микропроцессора КР580ВМ80А. В этом смысле микропроцессор представляет собой массив программно-доступных регистров, над содержимым которых выполняются указанные в командах операции.

____Блок программно-доступных регистров микропроцессора КР580ВМ80А характеризуется большой функциональной неоднородностью. Практически каждый регистр микропроцессора выполняет присущую только ему функцию. Это сделано с целью более короткого кодирования системы команд. Однако из-за необходимости учитывать все функциональные особенности регистрового блока усложнилось программирование. Набор программно-доступных регистров микропроцессора приведён ниже:

____Восьмиразрядный регистр А (аккумулятор) используется в большинстве команд логической и арифметической обработки. Обычно он адресуется неявно и служит как источником операнда, так и приёмником результата. Благодаря этому в командах микропроцессора явно указывается только один операнд.

____Признаки результата операции фиксируются во флажковом регистре F (Flags). Пять флажков С, P, AC, Z и S упакованы в байт, три разряда которого не используются. Флажки имеют следующее функциональное назначение:

С (Carry) - Признак переноса из старшего разряда АЛУ. Устанавливается в 1, если при выполнении операции сложения возникает перенос из старшего разряда или при выполнении вычитания перенос не возникает (т. е. происходит заём из старшего разряда), в противном случае устанавливается в 0.

P (Parity) - Признак чётного числа единиц в результате операции. Устанавливается в 1, если число единиц в результате чётно, в противном случае сбрасывается в 0.

AC (Auxiliary Carry) - Признак дополнительного переноса из младших четырёх разрядов (младшей тетрады) АЛУ. Устанавливается в 1 при появлении переноса из бита 3 (D3) в бит 4 (D4) результата при выполнении операций сложения и вычитания. Признак используется для преобразования двоичного результата в

двоично-десятичный при обработке двоично-десятичных чисел.

Z (Zero) - Признак нулевого результата. Устанавливается в 1, если результат равен нулю, в противном случае сбрасывается в 0.

S (Sign) - Знак результата. Устанавливается равным биту 7 (D7) результата.

____В некоторых командах пересылки флажковый регистр F совместно с аккумулятором А образует 16-разрядный регистр слова состояния программы PSW.

____Шестнадцатиразрядный регистр H, как правило, служит адресным регистром. При косвенной регистровой адресации он хранит 16-разрядный исполнительный адрес основной памяти. В этом случае к нему ссылаются с помощью мнемоники М (Memory). В некоторых командах старший и младший байты 16-разрядного регистра H могут быть адресованы независимо и использованы как отдельные 8-разрядные регистры данных H (High Byte) и L (Low Byte) соответственно, (старший и младший байты).

____Для организации вызова подпрограмм и процедур обслуживания прерываний, а также ряда других функций в состав регистров введён 16-разрядный указатель стека SP. Он всегда указывает на вершину стека TOS, которая содержит последний введённый в стек элемент. Стек заполняется в сторону младших адресов. Такое направление заполнения для микропроцессорных систем считается стандартным.

____Программный счётчик PC выполняет свою обычную функцию адресации объектного кода. В фазе исполнения текущей команды он указывает на следующий подлежащий выборке элемент командной последовательности. В этот момент возможна его перезагрузка, которая приведёт к изменению последовательной выборки команд.

INTE - Программно-доступный триггер разрешения прерывания. Связан с одноимённым выводом микропроцессора. Указывает на то, что микропроцессор готов к обмену в режиме прерывания (INTE=1), может принять запрос прерывания. Если микропроцессор готов к обмену в режиме прерывания, триггер установлен и микропроцессор может принять запрос прерывания. После перехода к обслуживанию прерывания, триггер сбрасывается, на одноимённом выводе микропроцессора соответственно устанавливается сигнал низкого уровня и запросы прерывания не воспринимаются. Способность восприятия микропроцессором последующих запросов устанавливается программным путём.

____Перечисленные выше 8-разрядные арифметические регистры F, A вместе с 16-разрядными адресными регистрами H, SP и PC образуют стандартный регистровый набор микропроцессора с аккумулятором. Набор микропроцессора КР580ВМ80А расширен четырьмя 8-разрядными регистрами общего назначения РОН: B, C, D и E. Эти регистры могут быть использованы либо как четыре регистра данных, либо как два 16-разрядных адресных регистра B и D, образованных парами BC и DE соответственно. Младшими байтами в парах являются C и E. Введение РОН позволило создать достаточно эффективный 8-разрядный микропроцессор с широкими функциональными возможностями.

____В командах на регистры ссылаются как явно, кодируя его 3-разрядным полем, так и неявно с помощью кода операции (КОП). Код операции всегда подразумевает способ использования регистров. Широкому распространению неявной формы ссылки способствует функциональная неоднородность регистров.

____Основная память микропроцессора КР580ВМ80А рассматривается как линейный массив, состоящий из 64 Кбайт. Формируемый микропроцессором 16-разрядный адрес даёт ему возможность адресовать любой байт памяти. Слова в памяти хранятся в двух соседних байтах. В байте с младшим адресом хранится младшая половина слова, а в байте со следующим адресом - старшая. Адресом слова служит адрес его младшего байта.

____В микропроцессоре определено четыре способа задания места расположения данных в памяти: прямой, косвенный регистровый через 16-разрядный адресный регистр H, B или D, непосредственный и автоинкрементный (автодекрементный) через указатель стека SP (стековый). При прямой и непосредственной адресации данных могут быть доступны байты или слова, при косвенной адресации - только байты. Стековая адресация применяется только при работе со словами. Как способ адресации, так и тип операнда определяется неявно кодом операции.

____Способы адресации, используемые в микропроцессоре КР580ВМ80А, следующие:

Непосредственная - байт 2 или 2 и 3 непосредственно содержат данные (операнд или адрес, заносимый в регистр). Единственное исключение составляет команда вызова подпрограммы обслуживания прерывания - адрес вектора указывается в байте КОП.

Прямая - для адресации слов данных, содержащихся в памяти или во внешнем устройстве. Прямой адрес указывается в байтах 2 или 2 и 3 команды.

Прямая регистровая - для адресации 1- и 2-байтовых слов, содержащихся в регистрах микропроцессора (адреса регистров, участвующих в операции, указываются в байте КОП).

Косвенная регистровая - для адресации байтов данных, находящихся в памяти, адрес ячеек которой определяется содержимым регистров, используемых в качестве адресных указателей (адрес регистра указывается в байтах КОП).

Стековая - для косвенной адресации 2-байтовых слов данных или адресов, находящихся в области памяти, отведённой под стек (адрес определяется по содержимому регистра - указателя стека).

Неявная - адрес регистра в команде явно не указывается, а способ адресации задаётся КОП.

____В микропроцессоре КР580ВМ80А используется изолированное пространство ввода-вывода. Эта отдельная область организована в виде массива из 256 8-разрядных портов ввода и 256 8-разрядных портов вывода. Допускается только один способ доступа к пространству ввода-вывода - прямой, когда 8-разрядный адрес порта указывается непосредственно в команде.

____Формат представления команд зависит от типа команды и используемого способа адресации. Для представления кода операции используется 1 байт. Максимальная длина команды составляет 3 байта.

____Для обеспечения гибкости кодирования вычислительного процесса используются три формата команд:

____Многобайтовые команды хранятся в соседних ячейках памяти и адресуются по байту 1. Формат определяется кодом операции (КОП).

Продолжение в следующем посте...

.

Изучение микропроцессорного комплекта КР580, практика и теория...

____Данная тема создана для изучения, сбора информации и практической реализации вычислительной системы используя, в основном, микросхемы данного микропроцессорного комплекта.

____Основной, и пожалуй самой важной микросхемой, в микропроцессорном комплекте КР580, является микропроцессор или иными словами центральная процессорная единица (CPU). Микросхема БИС КР580ВМ80А представляет собой 8-разрядный микропроцессор, в котором совмещены операционное и управляющее устройства. Управляющая память недоступна пользователю, в ней уже в процессе изготовления микросхемы БИС записываются микропрограммы операций (микропрограммы, по которым выполняются команды). Таким образом, предусматривается использование некоторой фиксированной системы команд, в которую пользователь не может внести изменений. В связи с этим данный микропроцессор относится к числу немикропрограммируемых, т. е. программируемых не на уровне микрокоманд, а на уровне команд.

____Комплект микросхем серии КР580, выполнен по n-МДП-технологии и ТТЛШ-технологии, характеризуется архитектурным единством, которое обеспечивается автономностью и функциональной законченностью отдельных микросхем, унификацией их интерфейса, программируемостью микросхем, их логической и электрической совместимостью.

____Необходимыми микросхемами в любой системе являются: микропроцессор КР580ВМ80А, тактовый генератор КР580ГФ24, системный контроллер КР580ВК28, буферная схема адреса, построенная на двух микросхемах КР580ВА86 для обеспечения нагрузочной способности по шине адреса. Объём памяти запоминающего устройства и использование одной или нескольких периферийных микросхем определяет пользователь.

____Микропроцессорная система имеет системную шину, образуемую из трёх шин: шина адреса А15 - А0, шина данных D7 - D0 и шина управления. Системная шина позволяет строить микропроцессорную систему по модульному принципу: модуль центрального процессора, модуль запоминающего устройства, модуль устройств ввода-вывода и т. д. Каждый модуль может содержать собственные буферные схемы адреса и данных.

____Магистральная структура микропроцессорной системы позволяет подключать микросхемы запоминающих устройств общей ёмкостью до 64 Кбайт и микросхемы устройств ввода-вывода до 256 каналов ввода и до 256 каналов вывода.

____Для помехоустойчивости системы низкочастотные помехи по цепи питания необходимо блокировать конденсатором суммарной ёмкостью из расчёта 0,1 мкФ на каждую микросхему, включённым между шинами +5 В и GND непосредственно в начале шины +5 В.

____Высокочастотные помехи необходимо блокировать конденсатором ёмкостью 0,015 - 0,022 мкФ, включённым между каждым выводом +5 В микросхемы и шиной GND в непосредственной близости от микросхем (не далее 5 мм).

____Для увеличения быстродействия системы трёхстабильные линии шины адреса и данных необходимо подключать к шине +5 В через резисторы сопротивлением 2,2 кОм.

____Характеристики микропроцессора КР580ВМ80А однозначно определяют архитектуру устройств, построенных на его основе. Фиксированная разрядность (8 двоичных разрядов), обработка слов, кратных байту, система команд, включающая широкий набор арифметических, логических команд, команд управления и пересылок, а также узел обработки прерываний и развитый интерфейс, определяют применение микропроцессора КР580ВМ80А как центрального процессорного устройства обработки данных.

____Для работы микропроцессора КР580ВМ80А применяется три источника питания: -5 В (ток потребления менее 1 мА), +5 В (ток потребления менее 70 мА) и +12 В (ток потребления менее 50 мА). Кристалл микропроцессора, содержащий около 5000 транзисторов, помещён в корпус с двухрядным расположением 40 выводов и шагом 2,5 мм между ними, типа 2123.40-2. Синхронизация микропроцессора осуществляется от двухфазного внешнего тактового генератора КР580ГФ24, амплитуда тактовых импульсов которого 12В.

____На рисунке ниже приведена базовая структурная схема микропроцессорной системы, построенной на базе микропроцессора КР580ВМ80А.

____В системе используется общая для хранения программ и данных основная память ёмкостью 64 Кбайт и подсистема ввода-вывода ёмкостью 256 байт. Двунаправленная 8-разрядная шина данных, 16-разрядная шина адреса и шина управления служат для организации побайтового обмена между отдельными модулями системы.

____Микропроцессор содержит внутреннее регистровое СОЗУ с организацией 6 х 8 или 3 х 16, а также средства, позволяющие организовать в любой зоне внешней памяти стек объёмом до 64 Кбайт. Это даёт возможность обрабатывать программы практически с неограниченным числом вложений. Микропроцессор имеет средства обслуживания 8-уровневых запросов прерываний, средства управления в режимах ожидания и прямого доступа к памяти, что позволяет осуществлять обмен с внешними устройствами любого быстродействия.

____Структура микропроцессора ориентирована на работу с памятью, имеющую байтовую организацию. Формат обрабатываемых данных имеет вид:

____Байт в зависимости от типа обрабатывающей команды можно интерпретировать следующим образом:

____как целое положительное число без знака в прямом коде. В этом случае числа изменяются в диапазоне

0 - 255:

010 = 0000 00002 = 0016;

25510 = 1111 11112 = FF16;

25510 = 1111 11112 = FF16;

____как число со знаком в дополнительном коде. Старший бит числа при этом считается знаковым и кодируется 0 для положительных чисел и 1 - для отрицательных. Остальные семь разрядов определяют величину числа. Числа изменяются в диапазоне от +127 до -128:

+12710 = 0111 11112 = 7F16;

010 = 0000 00002 = 0016;

-110 = 1111 11112 = FF16;

-12810 = 1000 00002 = 8016;

010 = 0000 00002 = 0016;

-110 = 1111 11112 = FF16;

-12810 = 1000 00002 = 8016;

____как двухразрядное двоично-десятичное число без знака. Старшие разряды D7 - D4 при этом определяют старший двоично-десятичный разряд, а младшие D3 - D0 определяют младший двоично-десятичный разряд. Диапазон представления чисел 0 - 99:

010 = 0000 00002 = 0016;

9910 = 1001 10012 = 9916,

9910 = 1001 10012 = 9916,

____как логический байт данных.

____Для выполнения некоторых операций допускается представление чисел в 2-байтовом формате в прямом или дополнительном коде. Числа при этом изменяются в диапазоне от +32 767 до -32 768.

____Арифметические операции - сложение, вычитание, инкремент, декремент выполняются по правилам двоичной арифметики над числами в дополнительном коде. Для обработки двоично-десятичных чисел имеется возможность преобразования результата в двоично-десятичный код. Логические операции И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕ, сдвиги - выполняются по правилам двоичной логики. Результат операции представляется числом в соответствующем формате и байтом признаков результата, вместе они образуют слово состояния PSW.

____С точки зрения пользователя и разработчика центрального процессора микроЭВМ важнейшими являются сведения о системе команд микропроцессора КР580ВМ80А. В этом смысле микропроцессор представляет собой массив программно-доступных регистров, над содержимым которых выполняются указанные в командах операции.

____Блок программно-доступных регистров микропроцессора КР580ВМ80А характеризуется большой функциональной неоднородностью. Практически каждый регистр микропроцессора выполняет присущую только ему функцию. Это сделано с целью более короткого кодирования системы команд. Однако из-за необходимости учитывать все функциональные особенности регистрового блока усложнилось программирование. Набор программно-доступных регистров микропроцессора приведён ниже:

____Восьмиразрядный регистр А (аккумулятор) используется в большинстве команд логической и арифметической обработки. Обычно он адресуется неявно и служит как источником операнда, так и приёмником результата. Благодаря этому в командах микропроцессора явно указывается только один операнд.

____Признаки результата операции фиксируются во флажковом регистре F (Flags). Пять флажков С, P, AC, Z и S упакованы в байт, три разряда которого не используются. Флажки имеют следующее функциональное назначение:

С (Carry) - Признак переноса из старшего разряда АЛУ. Устанавливается в 1, если при выполнении операции сложения возникает перенос из старшего разряда или при выполнении вычитания перенос не возникает (т. е. происходит заём из старшего разряда), в противном случае устанавливается в 0.

P (Parity) - Признак чётного числа единиц в результате операции. Устанавливается в 1, если число единиц в результате чётно, в противном случае сбрасывается в 0.

AC (Auxiliary Carry) - Признак дополнительного переноса из младших четырёх разрядов (младшей тетрады) АЛУ. Устанавливается в 1 при появлении переноса из бита 3 (D3) в бит 4 (D4) результата при выполнении операций сложения и вычитания. Признак используется для преобразования двоичного результата в

двоично-десятичный при обработке двоично-десятичных чисел.

Z (Zero) - Признак нулевого результата. Устанавливается в 1, если результат равен нулю, в противном случае сбрасывается в 0.

S (Sign) - Знак результата. Устанавливается равным биту 7 (D7) результата.

____В некоторых командах пересылки флажковый регистр F совместно с аккумулятором А образует 16-разрядный регистр слова состояния программы PSW.

____Шестнадцатиразрядный регистр H, как правило, служит адресным регистром. При косвенной регистровой адресации он хранит 16-разрядный исполнительный адрес основной памяти. В этом случае к нему ссылаются с помощью мнемоники М (Memory). В некоторых командах старший и младший байты 16-разрядного регистра H могут быть адресованы независимо и использованы как отдельные 8-разрядные регистры данных H (High Byte) и L (Low Byte) соответственно, (старший и младший байты).

____Для организации вызова подпрограмм и процедур обслуживания прерываний, а также ряда других функций в состав регистров введён 16-разрядный указатель стека SP. Он всегда указывает на вершину стека TOS, которая содержит последний введённый в стек элемент. Стек заполняется в сторону младших адресов. Такое направление заполнения для микропроцессорных систем считается стандартным.

____Программный счётчик PC выполняет свою обычную функцию адресации объектного кода. В фазе исполнения текущей команды он указывает на следующий подлежащий выборке элемент командной последовательности. В этот момент возможна его перезагрузка, которая приведёт к изменению последовательной выборки команд.

INTE - Программно-доступный триггер разрешения прерывания. Связан с одноимённым выводом микропроцессора. Указывает на то, что микропроцессор готов к обмену в режиме прерывания (INTE=1), может принять запрос прерывания. Если микропроцессор готов к обмену в режиме прерывания, триггер установлен и микропроцессор может принять запрос прерывания. После перехода к обслуживанию прерывания, триггер сбрасывается, на одноимённом выводе микропроцессора соответственно устанавливается сигнал низкого уровня и запросы прерывания не воспринимаются. Способность восприятия микропроцессором последующих запросов устанавливается программным путём.

____Перечисленные выше 8-разрядные арифметические регистры F, A вместе с 16-разрядными адресными регистрами H, SP и PC образуют стандартный регистровый набор микропроцессора с аккумулятором. Набор микропроцессора КР580ВМ80А расширен четырьмя 8-разрядными регистрами общего назначения РОН: B, C, D и E. Эти регистры могут быть использованы либо как четыре регистра данных, либо как два 16-разрядных адресных регистра B и D, образованных парами BC и DE соответственно. Младшими байтами в парах являются C и E. Введение РОН позволило создать достаточно эффективный 8-разрядный микропроцессор с широкими функциональными возможностями.

____В командах на регистры ссылаются как явно, кодируя его 3-разрядным полем, так и неявно с помощью кода операции (КОП). Код операции всегда подразумевает способ использования регистров. Широкому распространению неявной формы ссылки способствует функциональная неоднородность регистров.

____Основная память микропроцессора КР580ВМ80А рассматривается как линейный массив, состоящий из 64 Кбайт. Формируемый микропроцессором 16-разрядный адрес даёт ему возможность адресовать любой байт памяти. Слова в памяти хранятся в двух соседних байтах. В байте с младшим адресом хранится младшая половина слова, а в байте со следующим адресом - старшая. Адресом слова служит адрес его младшего байта.

____В микропроцессоре определено четыре способа задания места расположения данных в памяти: прямой, косвенный регистровый через 16-разрядный адресный регистр H, B или D, непосредственный и автоинкрементный (автодекрементный) через указатель стека SP (стековый). При прямой и непосредственной адресации данных могут быть доступны байты или слова, при косвенной адресации - только байты. Стековая адресация применяется только при работе со словами. Как способ адресации, так и тип операнда определяется неявно кодом операции.

____Способы адресации, используемые в микропроцессоре КР580ВМ80А, следующие:

Непосредственная - байт 2 или 2 и 3 непосредственно содержат данные (операнд или адрес, заносимый в регистр). Единственное исключение составляет команда вызова подпрограммы обслуживания прерывания - адрес вектора указывается в байте КОП.

Прямая - для адресации слов данных, содержащихся в памяти или во внешнем устройстве. Прямой адрес указывается в байтах 2 или 2 и 3 команды.

Прямая регистровая - для адресации 1- и 2-байтовых слов, содержащихся в регистрах микропроцессора (адреса регистров, участвующих в операции, указываются в байте КОП).

Косвенная регистровая - для адресации байтов данных, находящихся в памяти, адрес ячеек которой определяется содержимым регистров, используемых в качестве адресных указателей (адрес регистра указывается в байтах КОП).

Стековая - для косвенной адресации 2-байтовых слов данных или адресов, находящихся в области памяти, отведённой под стек (адрес определяется по содержимому регистра - указателя стека).

Неявная - адрес регистра в команде явно не указывается, а способ адресации задаётся КОП.

____В микропроцессоре КР580ВМ80А используется изолированное пространство ввода-вывода. Эта отдельная область организована в виде массива из 256 8-разрядных портов ввода и 256 8-разрядных портов вывода. Допускается только один способ доступа к пространству ввода-вывода - прямой, когда 8-разрядный адрес порта указывается непосредственно в команде.

____Формат представления команд зависит от типа команды и используемого способа адресации. Для представления кода операции используется 1 байт. Максимальная длина команды составляет 3 байта.

____Для обеспечения гибкости кодирования вычислительного процесса используются три формата команд:

____Многобайтовые команды хранятся в соседних ячейках памяти и адресуются по байту 1. Формат определяется кодом операции (КОП).

Продолжение в следующем посте...

.

Последний раз редактировалось: Viktor2312 (Пн Сен 18 2017, 18:05), всего редактировалось 29 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучение микропроцессорного комплекта КР580, практика и теория...

Re: Изучение микропроцессорного комплекта КР580, практика и теория...

2

.

____В микропроцессоре КР580ВМ80А применяется довольно простой формат команд. Команды имеют длину от одного до трёх байт. Код операции всегда размещён в первом байте команды. Второй и, если необходимо, третий байты команды отводятся под непосредственные данные, адрес порта или ячейки памяти. В командах допускается явное задание только одного адреса памяти. По этой причине систему команд микропроцессора следует отнести к классу одноадресных.

____В зависимости от характера выполняемых операций систему команд можно разбить на следующие группы:

Группа команд пересылки:

MOV D, S - Команды пересылки между регистрами A, B, C, D, E, H, L или между регистрами и памятью с использованием соответственно регистровой и косвенной адресации через пару HL.

____В командах пересылки байтов поля DDD и SSS используются для указания 8-разрядных регистров A, B, C, D, E, H, L, а М обозначает косвенную адресацию через регистровую пару HL, которая должна содержать прямой адрес байта, участвующего в обмене. Важно отметить, что первый и второй операнды не должны определять имя ячейки памяти одновременно. Например, если указать первый операнд как 110 и второй 110, то получится код 0111 01102 = 7616, который соответствует команде HLT - останова выполнения команд в микропроцессоре. Данные команды являются однобайтными и не изменяют признаки регистра F.

MVI D, D8 - Команды непосредственной загрузки регистров или ячеек памяти байтом данных, содержащимся в байте 2 команды.

Данные команды являются двухбайтными и не изменяют признаки регистра F.

LDA ADR - Загрузка аккумулятора из памяти по адресу, указанному в адресной части команды.

STA ADR - Запоминание содержимого аккумулятора в памяти по адресу, заданному в адресной части.

Данные команды являются трёхбайтными и не изменяют признаки регистра F.

LDAX rp - Загрузка аккумулятора из памяти по адресу, указанному в паре регистров BC или DE.

STAX rp - Запоминание содержимого аккумулятора в памяти по адресу, указанному в паре регистров BC или DE.

Данные команды являются однобайтными и не изменяют признаки регистра F.

____С учётом значимости 16-разрядного регистра H (регистровая пара HL) в системе команд предусмотрены операции загрузки LHLD и запоминания SHLD его содержимого по прямому адресу.

LHLD ADR - Команда загрузки регистровой пары HL двумя байтами из памяти, адрес первого из которых задан в байтах 2 и 3 команды, а адрес второго вычисляется увеличением на 1 первого.

SHLD ADR - Команда запоминания содержимого регистровой пары HL в двух байтах памяти, адрес младшего из которых задан в байтах 2 и 3 команды, а адрес старшего вычисляется увеличением на 1 адреса младшего байта.

Данные команды являются трёхбайтными и не изменяют признаки регистра F.

LXI X, D16 - Команда непосредственной загрузки регистровых пар и указателя стека SP 2-байтовыми словами, содержащимися в байтах 2 и 3 команды.

Данные команды являются трёхбайтными и не изменяют признаки регистра F.

PUSH rp - Команда занесения в стек 2 байт данных из регистров BC, DE, HL или PSW.

POP rp - Команда извлечения из стека 2 байт данных и занесения их в регистры BC, DE, HL или PSW.

Данные команды являются однобайтными и не изменяют признаки регистра F. За исключением команды

POP PSW, так как при извлечении из стека 2 байт данных содержимое регистра признаков F заменяется новыми извлечёнными данными. И соответственно, содержимое регистра признаков F может вообще не измениться, а может полностью изменить значение всех бит признаков, на противоположное.

____Команды PUSH и POP организуют запись в стек и выборку из него содержимого 16-разрядных регистров B, D, H или PSW. Благодаря этим операциям создаётся удобный механизм сохранения и восстановления текущего контекста регистровой области или её части для передачи параметров через стек, а также для выполнения других важных при программировании функций. Системный стек растёт в сторону уменьшения адресов, а его указатель всегда адресует последний элемент стека или его вершину TOS.

.

Продолжение.

____В микропроцессоре КР580ВМ80А применяется довольно простой формат команд. Команды имеют длину от одного до трёх байт. Код операции всегда размещён в первом байте команды. Второй и, если необходимо, третий байты команды отводятся под непосредственные данные, адрес порта или ячейки памяти. В командах допускается явное задание только одного адреса памяти. По этой причине систему команд микропроцессора следует отнести к классу одноадресных.

____В зависимости от характера выполняемых операций систему команд можно разбить на следующие группы:

- Команды пересылки.

- Арифметические команды.

- Логические команды.

- Команды управления.

Группа команд пересылки:

MOV D, S - Команды пересылки между регистрами A, B, C, D, E, H, L или между регистрами и памятью с использованием соответственно регистровой и косвенной адресации через пару HL.

____В командах пересылки байтов поля DDD и SSS используются для указания 8-разрядных регистров A, B, C, D, E, H, L, а М обозначает косвенную адресацию через регистровую пару HL, которая должна содержать прямой адрес байта, участвующего в обмене. Важно отметить, что первый и второй операнды не должны определять имя ячейки памяти одновременно. Например, если указать первый операнд как 110 и второй 110, то получится код 0111 01102 = 7616, который соответствует команде HLT - останова выполнения команд в микропроцессоре. Данные команды являются однобайтными и не изменяют признаки регистра F.

MVI D, D8 - Команды непосредственной загрузки регистров или ячеек памяти байтом данных, содержащимся в байте 2 команды.

Данные команды являются двухбайтными и не изменяют признаки регистра F.

LDA ADR - Загрузка аккумулятора из памяти по адресу, указанному в адресной части команды.

STA ADR - Запоминание содержимого аккумулятора в памяти по адресу, заданному в адресной части.

Данные команды являются трёхбайтными и не изменяют признаки регистра F.

LDAX rp - Загрузка аккумулятора из памяти по адресу, указанному в паре регистров BC или DE.

STAX rp - Запоминание содержимого аккумулятора в памяти по адресу, указанному в паре регистров BC или DE.

Данные команды являются однобайтными и не изменяют признаки регистра F.

____С учётом значимости 16-разрядного регистра H (регистровая пара HL) в системе команд предусмотрены операции загрузки LHLD и запоминания SHLD его содержимого по прямому адресу.

LHLD ADR - Команда загрузки регистровой пары HL двумя байтами из памяти, адрес первого из которых задан в байтах 2 и 3 команды, а адрес второго вычисляется увеличением на 1 первого.

SHLD ADR - Команда запоминания содержимого регистровой пары HL в двух байтах памяти, адрес младшего из которых задан в байтах 2 и 3 команды, а адрес старшего вычисляется увеличением на 1 адреса младшего байта.

Данные команды являются трёхбайтными и не изменяют признаки регистра F.

LXI X, D16 - Команда непосредственной загрузки регистровых пар и указателя стека SP 2-байтовыми словами, содержащимися в байтах 2 и 3 команды.

Данные команды являются трёхбайтными и не изменяют признаки регистра F.

PUSH rp - Команда занесения в стек 2 байт данных из регистров BC, DE, HL или PSW.

POP rp - Команда извлечения из стека 2 байт данных и занесения их в регистры BC, DE, HL или PSW.

Данные команды являются однобайтными и не изменяют признаки регистра F. За исключением команды

POP PSW, так как при извлечении из стека 2 байт данных содержимое регистра признаков F заменяется новыми извлечёнными данными. И соответственно, содержимое регистра признаков F может вообще не измениться, а может полностью изменить значение всех бит признаков, на противоположное.

____Команды PUSH и POP организуют запись в стек и выборку из него содержимого 16-разрядных регистров B, D, H или PSW. Благодаря этим операциям создаётся удобный механизм сохранения и восстановления текущего контекста регистровой области или её части для передачи параметров через стек, а также для выполнения других важных при программировании функций. Системный стек растёт в сторону уменьшения адресов, а его указатель всегда адресует последний элемент стека или его вершину TOS.

.

Последний раз редактировалось: Viktor2312 (Чт Окт 05 2017, 10:40), всего редактировалось 17 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Похожие темы

Похожие темы» STM32F Конспект, теория, практика.

» Использование ЯВУ для разработки программ для РК86

» Литература к разделу современные компьютеры и ПО. Разное...

» Статьи, заметки, очерки, разное...

» Программирование для компьютера РК86

» Использование ЯВУ для разработки программ для РК86

» Литература к разделу современные компьютеры и ПО. Разное...

» Статьи, заметки, очерки, разное...

» Программирование для компьютера РК86

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|