Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Микросхемы ПЛИС CPLD CoolRunner-II.

Страница 1 из 1 • Поделиться

Микросхемы ПЛИС CPLD CoolRunner-II.

Микросхемы ПЛИС CPLD CoolRunner-II.

1

.

____Программируемые логические интегральные схемы (ПЛИС) семейства CPLD (Complex Programmable Logic Device) находят широкое применение в цифровых устройствах различного назначения благодаря низкой стоимости и таким преимуществам, как сохранение конфигурации при выключении питания и возможность программирования в системе.

____Фирма Xilinx, является ведущим мировым производителем ПЛИС, наряду с разработкой новых семейств FPGA ведёт постоянную работу по созданию перспективных микросхем с архитектурой CPLD отвечающих современным требованиям. При этом основными направлениями являются повышение производительности ПЛИС, снижение потребляемой мощности, реализация возможности поддержки различных цифровых сигнальных стандартов ввода/вывода, обеспечение надёжной защиты конфигурационных данных от копирования.

CoolRunner-II CPLD White Papers:

Скачать: White papers. Secure Applications.

____Результатом внедрения передовых методов технологии производства микросхем и новых архитектурных решений является выпуск семейства микросхем CPLD CoolRunner-II, сочетающих высокое быстродействие с минимальной потребляемой мощностью. Это семейство представляет собой новое поколение ПЛИС с архитектурой XPLA3 (eXtended Programmable Logic Array), применяемой в микросхемах CoolRunner XPLA3.

CoolRunner-II CPLD Data Sheets:

Скачать: CoolRunner-II Family Data Sheet.

Скачать: XC2C32A Data Sheet.

Скачать: XC2C64А Data Sheet.

Скачать: XC2C128 Data Sheet.

Скачать: XC2C256 Data Sheet.

Скачать: XC2C384 Data Sheet.

Скачать: XC2C512 Data Sheet.

____Семейство микросхем ПЛИС CoolRunner-II содержит шесть типов микросхем ПЛИС логической ёмкостью от 32 до 512 макроячеек, выпускаемых по технологии 0,18 мкм. Напряжение питания ядра микросхем составляет 1,8 В.

____Микросхемы рассматриваемого семейства позволяют реализовать на их основе проекты с системными частотами до 323 МГц. Минимальная задержка распространения сигнала от входного контакта микросхемы до выходного через комбинационную логику составляет от 3,8 до 7,1 нс. Архитектурные особенности микросхем ПЛИС семейства CoolRunner-II предоставляют возможность повышения производительности проектируемых устройств без увеличения внешней частоты синхронизации за счёт использования триггеров, тактируемых фронтом и спадом сигнала синхронизации. При этом микросхемы семейства CoolRunner-II характеризуются ультранизкими значениями мощности, потребляемой как в статическом, так и в динамическом режиме. Значение потребляемого тока для статического режима не превосходит 100 мкА, что на порядок ниже по сравнению с ПЛИС других серий и производителей. Мощность, потребляемая в динамическом режиме, также в несколько раз меньше, чем у других типов микросхем с соответствующим объёмом ресурсов. Такие показатели обусловлены, в первую очередь, применением технологии FZP (Fast Zero Power), обеспечивающей достижение минимального уровня потребляемой мощности в сочетании с высоким быстродействием. Основные временные параметры микросхем ПЛИС семейства CoolRunner-II представлены в таблице ниже:

____Но лучше ориентироваться по таблице из datasheet, а таблица которая выше приведена из-за расшифровки, на русским языке, параметров указанных в таблице.

____Использование в архитектуре микросхем рассматриваемого семейства усовершенствованной коммутационной матрицы Advansed Interconnect Matrix (AIM) позволяет реализовать высокую скорость переключения при низкой потребляемой мощности. Кроме того, архитектурные особенности предоставляют возможность внедрения новых технических решений, позволяющих добиться дополнительного снижения общей потребляемой мощности. К числу таких решений относится применение методики CoolCLOCK и технологии DataGATE. В основе методики CoolCLOCK лежит двукратное деление частоты исходного тактового сигнала и последующее её "удвоение" в макроячейках за счёт применения триггеров, тактируемых фронтом и спадом сигнала синхронизации. Наличие встроенного делителя частоты тактового сигнала с коэффициентами деления 2, 4, 6, 8, 10, 12, 14, 16 обеспечивает оптимальную реализацию этой методики. Технология DataGATE предусматривает возможность сокращения потребляемой мощности за счёт блокировки неиспользуемых в определённые интервалы времени входных сигналов в ячейках ввода/вывода.

____Микросхемы ПЛИС данного семейства отличаются оптимизированной архитектурой, обеспечивающей повышение эффективности процесса логического синтеза реализуемых проектов. Используемые архитектурные решения предоставляют расширенные возможности фиксации пользовательских выводов микросхем перед выполнением фазы Fit этапа реализации (Implementation), которые сочетаются с полной трассировкой проекта. Простая детерминированная временная модель, данных микросхем ПЛИС, обусловленная особенностями их архитектуры, позволяет достаточно точно рассчитать задержки распространения сигналов проектируемого устройства.

____В блоках ввода/вывода предусмотрены дополнительные функции, направленные на минимизацию влияния помех на пользовательских контактах микросхем. Функция раздельного управления длительностью фронтов выходных сигналов для каждого вывода ПЛИС обеспечивает снижение уровня помех на выходных контактах микросхемы. Возможность выборочной установки встроенных триггеров Шмитта во входных цепях блоков ввода/вывода позволяет снизить влияние помех на входах ПЛИС. Кроме того, неиспользуемые выводы микросхемы могут быть сконфигурированы как дополнительные контакты, подключаемые к "общей" шине, что позволяет повысить помехозащищённость ПЛИС.

____Совместимость блоков ввода/вывода с логическими уровнями стандартов цифровых сигналов 1,5 В; 1,8 В; 2,5 В и 3,3 В позволяет реализовывать устройства со смешанным питанием. Организация блоков ввода/вывода в виде банков (в ПЛИС с большим числом ячеек) создаёт возможность одновременной реализации в одной микросхеме нескольких стандартов цифровых сигналов, требующих различных напряжений питания VCCIO. Предусмотрена поддержка следующих стандартов: LVTTL, LVCMOS33, LVCMOS25, LVCMOS18, 1,5 В I/O, HSTL-1, SSTL2-1, SSTL3-1. Ячейки ввода/вывода предоставляют возможность формирования выходов с открытым стоком и тремя состояниями.

____Макроячейки данного семейства микросхем ПЛИС отличаются, прежде всего, возможностью конфигурирования триггерного элемента не только в виде D - или Т - триггерного элемента с динамическим управлением, с потенциальным управлением (защёлки), но и триггера тактируемого фронтом и спадом сигнала синхронизации. В каждой макроячейке предусмотрена реализация сигнала разрешения синхронизации (clock enable). Ресурсы ПЛИС предоставляют возможность комплексного асинхронного тактирования элементов проектируемого устройства с использованием тактовых сигналов, формируемых внутри функционального блока, и четырёх глобальных тактовых сигналов, поступающих с выводов микросхемы. Макроячейки позволяют реализовать режимы асинхронного сброса или асинхронной установки триггера, используя для этого локальные и глобальные управляющие сигналы.

____Четыре независимых уровня защиты конфигурационных данных от несанкционированного копирования обеспечивают надёжную охрану прав интеллектуальной собственности. Обнаружение попытки нарушения защиты на любом уровне приводит к стиранию конфигурационной информации в микросхеме.

____Для работы с микросхемами данного семейства, как и других серий CPLD, выпускаемых фирмой Xilinx, не требуется аппаратный программатор. Все операции программирования и обратного считывания конфигурационных данных могут выполняться непосредственно в проектируемой схеме через порт JTAG-интерфейса. При этом полностью поддерживается протокол периферийного сканирования в соответствии со спецификацией стандарта IEEE Std 1149.1 (JTAG). Кроме того, предусмотрена поддержка конфигурирования в системе с напряжением питания 1,8 В по стандарту IEEE Std 1532. Загрузочный кабель, связывающий JTAG-порт с параллельным портом ПК, можно изготовить самостоятельно, воспользовавшись, например, схемой, представленной в документации. Всё что касается данного кабеля будет выложено в последующих постах, с подробным описанием.

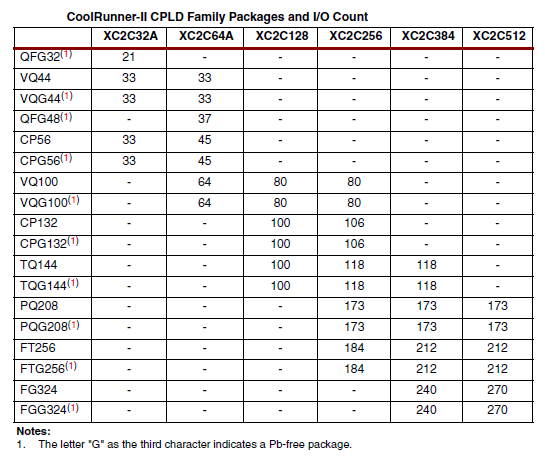

____Микросхемы ПЛИС рассматриваемого семейства производятся с использованием расширенного типового ряда корпусов, который включает в себя Chip Scale Packege (CSP), BGA, Fine Line BGA, TQFP, PQFP, VQFP и PLCC. Все микросхемы обладают совместимостью по выводам в случае использования одинаковых корпусов. Применяемые разновидности корпусов для каждого типа микросхем с указанием числа доступных пользовательских выводов приведены в таблице ниже.

____Ниже представлена таблица из datasheet.

Package Drawings:

Скачать: PK076 - QFG32/QFG48 - Package Drawing.

Скачать: PK012 - VQ44/VQG44 - Package Drawing.

Скачать: PK013 - CP56/CPG56 - Package Drawing.

Скачать: PK012 - VQ100/VQG100 - Package Drawing.

____Высокая надёжность микросхем обеспечивает не менее 1000 циклов перепрограммирования и гарантированный срок хранения запрограммированной конфигурации не менее 20 лет.

____Применение микросхем ПЛИС фирмы Xilinx семейства CPLD позволяет избежать дополнительных затрат на приобретение программных средств для разработки проектов и конфигурирования микросхем. Полнофункциональная свободно распространяемая система автоматического проектирования WebPACK ISE (Integrated Synthesis Environment) поддерживает семейство CoolRunner-II в полном объёме.

____Основные параметры микросхем ПЛИС, входящих в семейство CoolRunner-II, представлены в таблице ниже:

____Ниже представлена таблица из datasheet.

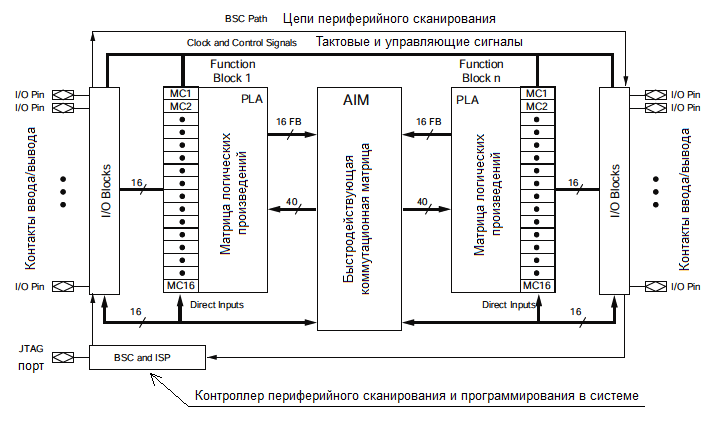

____Обобщённая архитектура микросхем ПЛИС семейства CoolRunner-II представлена на рисунке ниже. Её основу составляют совокупность функциональных блоков (Function Block, FB), блоков ввода/вывода (Input/Output block, IOB) и быстродействующая переключающая матрица AIM. Число функциональных блоков и блоков ввода/вывода определяется типом микросхемы ПЛИС. Несмотря на схожесть с типовой архитектурой ПЛИС семейств CPLD, структура принципиально отличается способом реализации её элементов.

____В функциональных блоках сосредоточены основные логические ресурсы микросхем. Каждый функциональный блок имеет 40 входов, подключённых к выводам переключающей матрицы, и 16 "быстрых" входов, которые соединены непосредственно с блоками ввода/вывода. Кроме того, к функциональным блокам подведено четыре глобальных сигнала: сигнал сброса и установки GSR и три тактовых сигнала GCK0 - GCK2. Структура функционального блока включает в себя программируемую матрицу логических произведений и 16 независимых макроячеек. Используется программируемая матрица логических произведений типа PLA (Programmable Logic Array). Принципиальные отличия её от PAL-матриц, применяемых в большинстве ПЛИС семейств CPLD, мы рассмотрим в отдельном посте, позже.Применение PLA-матрицы позволяет оптимизировать разделение и совместное использование ресурсов микросхемы при реализации проекта. Её 40 прямых и инверсных входов соединены непосредственно с выходами переключающей матрицы. PLA-матрица логических произведений позволяет сформировать 56 термов, часть которых может использоваться в качестве управляющих сигналов, доступных для любой макроячейки функционального блока. Эти сигналы выполняют функции тактирования, сброса и установки триггеров макроячеек, а также разрешения выходов микросхемы.

____Структура макроячейки показана на рисунке ниже вместе с программируемой матрицей логических произведений.

____Каждая макроячейка может быть сконфигурирована для выполнения комбинаторной и регистровой функции, причём триггер, входящий в её состав, может быть реализован как D- или Т-триггер или как защёлка. Кроме того, он может быть сконфигурирован как триггер, тактируемый фронтом и спадом сигнала синхронизации. При реализации только комбинаторной функции триггер не используется. В состав макроячейки также входят элементы, позволяющие реализовать, при необходимости, режим асинхронного сброса и установки триггера. При этом в качестве сигналов сброса и установки могут использоваться сформированные PLA-матрицей термы (PTA), управляющие термы (CTR и CTS соответственно) и глобальный сигнал сброса/установки (GSR). Следует обратить внимание на то, что сигналы управляющих термов CTR и CTS являются общими для всех макроячеек одного функционального блока, а глобальный сигнал сброса/установки GSR - общим для всех функциональных блоков микросхемы.

____Помимо входов, соединённых с выходами PLA-матрицы логических произведений, макроячейка содержит дополнительный, так называемый "быстрый" вход, подключённый непосредственно к блокам ввода/вывода. Тем самым предоставляется возможность использования триггера, входящего в состав макроячейки, в качестве входного триггера или защёлки. При этом комбинаторные функции макроячейки сохраняются.

____Результирующие сигналы с выходов макроячеек поступают в блоки ввода/вывода и на входы высокоскоростной переключающей матрицы AIM, которая позволяет передать их далее на входы других функциональных блоков. На остальные её входы подаются сигналы, поступающие из блоков ввода/вывода, которые затем направляются ко входам функциональных блоков микросхемы. Переключающая матрица AIM обеспечивает необходимую коммутацию сигналов, поступающих из блоков ввода/вывода, входных и выходных сигналов функциональных блоков, при минимальной потребляемой мощности в сочетании с высоким быстродействием.

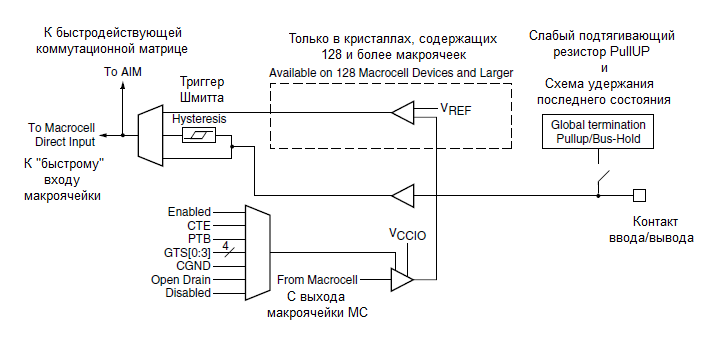

____Блоки ввода/вывода предназначены для организации интерфейса между внутренними сигналами микросхемы и выводами ПЛИС. Они выполняют функцию буферизации всех входных и выходных сигналов, управления выходами и формирования программируемого "общего" вывода. Структура блока ввода/вывода показана на рисунке ниже.

____Помимо входного и выходного буферных элементов в состав блоков ввода/вывода входит триггер Шмитта, предназначенный для выборочного использования с целью уменьшения уровня помех на входных контактах микросхемы. Структура блоков ввода/вывода включает также высокоомный подтягивающий резистор PullUP и цепь удержания последнего состояния Bus Hold. Выходные цепи обеспечивают возможность формирования выходов, функционирующих в обычном режиме, с открытым стоком или с тремя состояниями (высокоимпедансное состояние). Кроме того, они выполняют функцию управления длительностью фронтов выходных сигналов.

____Характерной особенностью блоков ввода/вывода является поддержка ряда широко используемых стандартов цифровых сигналов, позволяющих организовать взаимодействие с внешними элементами высокоскоростной памяти и сопряжение с шинными интерфейсами. Например, стандарт HSTL (High-Speed Transceiver Logic), широко применяется в высокоскоростных интерфейсах памяти, а SSTL (Stub-Series Terminated Logic) - при реализации шинных интерфейсов. Некоторые из поддерживаемых стандартов требуют подачи дополнительного внешнего напряжения порогового уровня входных каскадов. В таблице ниже приведён список стандартов цифровых сигналов, поддерживаемых блоками ввода/вывода, с указанием значений напряжения питания выходных каскадов VCCIO и порогового уровня входных каскадов VREF.

____Ниже представлена таблица из datasheet.

____Все блоки ввода/вывода сгруппированы в виде банков, число которых определяется типом микросхемы. Каждый пользовательский вывод ПЛИС может быть сконфигурирован в соответствии с выбранным стандартом. При этом следует учитывать, что в рамках одного банка ввода/вывода одновременно могут быть реализованы только стандарты, требующие одно значение напряжения питания выходных каскадов VCCIO.

____Контроллер периферийного сканирования и программирования в системе обеспечивает выполнение операций конфигурирования микросхемы и периферийного сканирования через порт JTAG-интерфейса.

.

Микросхемы ПЛИС CPLD CoolRunner-II.

____Программируемые логические интегральные схемы (ПЛИС) семейства CPLD (Complex Programmable Logic Device) находят широкое применение в цифровых устройствах различного назначения благодаря низкой стоимости и таким преимуществам, как сохранение конфигурации при выключении питания и возможность программирования в системе.

____Фирма Xilinx, является ведущим мировым производителем ПЛИС, наряду с разработкой новых семейств FPGA ведёт постоянную работу по созданию перспективных микросхем с архитектурой CPLD отвечающих современным требованиям. При этом основными направлениями являются повышение производительности ПЛИС, снижение потребляемой мощности, реализация возможности поддержки различных цифровых сигнальных стандартов ввода/вывода, обеспечение надёжной защиты конфигурационных данных от копирования.

CoolRunner-II CPLD White Papers:

Скачать: White papers. Secure Applications.

____Результатом внедрения передовых методов технологии производства микросхем и новых архитектурных решений является выпуск семейства микросхем CPLD CoolRunner-II, сочетающих высокое быстродействие с минимальной потребляемой мощностью. Это семейство представляет собой новое поколение ПЛИС с архитектурой XPLA3 (eXtended Programmable Logic Array), применяемой в микросхемах CoolRunner XPLA3.

CoolRunner-II CPLD Data Sheets:

Скачать: CoolRunner-II Family Data Sheet.

Скачать: XC2C32A Data Sheet.

Скачать: XC2C64А Data Sheet.

Скачать: XC2C128 Data Sheet.

Скачать: XC2C256 Data Sheet.

Скачать: XC2C384 Data Sheet.

Скачать: XC2C512 Data Sheet.

Общая характеристика.

____Семейство микросхем ПЛИС CoolRunner-II содержит шесть типов микросхем ПЛИС логической ёмкостью от 32 до 512 макроячеек, выпускаемых по технологии 0,18 мкм. Напряжение питания ядра микросхем составляет 1,8 В.

____Микросхемы рассматриваемого семейства позволяют реализовать на их основе проекты с системными частотами до 323 МГц. Минимальная задержка распространения сигнала от входного контакта микросхемы до выходного через комбинационную логику составляет от 3,8 до 7,1 нс. Архитектурные особенности микросхем ПЛИС семейства CoolRunner-II предоставляют возможность повышения производительности проектируемых устройств без увеличения внешней частоты синхронизации за счёт использования триггеров, тактируемых фронтом и спадом сигнала синхронизации. При этом микросхемы семейства CoolRunner-II характеризуются ультранизкими значениями мощности, потребляемой как в статическом, так и в динамическом режиме. Значение потребляемого тока для статического режима не превосходит 100 мкА, что на порядок ниже по сравнению с ПЛИС других серий и производителей. Мощность, потребляемая в динамическом режиме, также в несколько раз меньше, чем у других типов микросхем с соответствующим объёмом ресурсов. Такие показатели обусловлены, в первую очередь, применением технологии FZP (Fast Zero Power), обеспечивающей достижение минимального уровня потребляемой мощности в сочетании с высоким быстродействием. Основные временные параметры микросхем ПЛИС семейства CoolRunner-II представлены в таблице ниже:

____Но лучше ориентироваться по таблице из datasheet, а таблица которая выше приведена из-за расшифровки, на русским языке, параметров указанных в таблице.

____Использование в архитектуре микросхем рассматриваемого семейства усовершенствованной коммутационной матрицы Advansed Interconnect Matrix (AIM) позволяет реализовать высокую скорость переключения при низкой потребляемой мощности. Кроме того, архитектурные особенности предоставляют возможность внедрения новых технических решений, позволяющих добиться дополнительного снижения общей потребляемой мощности. К числу таких решений относится применение методики CoolCLOCK и технологии DataGATE. В основе методики CoolCLOCK лежит двукратное деление частоты исходного тактового сигнала и последующее её "удвоение" в макроячейках за счёт применения триггеров, тактируемых фронтом и спадом сигнала синхронизации. Наличие встроенного делителя частоты тактового сигнала с коэффициентами деления 2, 4, 6, 8, 10, 12, 14, 16 обеспечивает оптимальную реализацию этой методики. Технология DataGATE предусматривает возможность сокращения потребляемой мощности за счёт блокировки неиспользуемых в определённые интервалы времени входных сигналов в ячейках ввода/вывода.

____Микросхемы ПЛИС данного семейства отличаются оптимизированной архитектурой, обеспечивающей повышение эффективности процесса логического синтеза реализуемых проектов. Используемые архитектурные решения предоставляют расширенные возможности фиксации пользовательских выводов микросхем перед выполнением фазы Fit этапа реализации (Implementation), которые сочетаются с полной трассировкой проекта. Простая детерминированная временная модель, данных микросхем ПЛИС, обусловленная особенностями их архитектуры, позволяет достаточно точно рассчитать задержки распространения сигналов проектируемого устройства.

____В блоках ввода/вывода предусмотрены дополнительные функции, направленные на минимизацию влияния помех на пользовательских контактах микросхем. Функция раздельного управления длительностью фронтов выходных сигналов для каждого вывода ПЛИС обеспечивает снижение уровня помех на выходных контактах микросхемы. Возможность выборочной установки встроенных триггеров Шмитта во входных цепях блоков ввода/вывода позволяет снизить влияние помех на входах ПЛИС. Кроме того, неиспользуемые выводы микросхемы могут быть сконфигурированы как дополнительные контакты, подключаемые к "общей" шине, что позволяет повысить помехозащищённость ПЛИС.

____Совместимость блоков ввода/вывода с логическими уровнями стандартов цифровых сигналов 1,5 В; 1,8 В; 2,5 В и 3,3 В позволяет реализовывать устройства со смешанным питанием. Организация блоков ввода/вывода в виде банков (в ПЛИС с большим числом ячеек) создаёт возможность одновременной реализации в одной микросхеме нескольких стандартов цифровых сигналов, требующих различных напряжений питания VCCIO. Предусмотрена поддержка следующих стандартов: LVTTL, LVCMOS33, LVCMOS25, LVCMOS18, 1,5 В I/O, HSTL-1, SSTL2-1, SSTL3-1. Ячейки ввода/вывода предоставляют возможность формирования выходов с открытым стоком и тремя состояниями.

____Макроячейки данного семейства микросхем ПЛИС отличаются, прежде всего, возможностью конфигурирования триггерного элемента не только в виде D - или Т - триггерного элемента с динамическим управлением, с потенциальным управлением (защёлки), но и триггера тактируемого фронтом и спадом сигнала синхронизации. В каждой макроячейке предусмотрена реализация сигнала разрешения синхронизации (clock enable). Ресурсы ПЛИС предоставляют возможность комплексного асинхронного тактирования элементов проектируемого устройства с использованием тактовых сигналов, формируемых внутри функционального блока, и четырёх глобальных тактовых сигналов, поступающих с выводов микросхемы. Макроячейки позволяют реализовать режимы асинхронного сброса или асинхронной установки триггера, используя для этого локальные и глобальные управляющие сигналы.

____Четыре независимых уровня защиты конфигурационных данных от несанкционированного копирования обеспечивают надёжную охрану прав интеллектуальной собственности. Обнаружение попытки нарушения защиты на любом уровне приводит к стиранию конфигурационной информации в микросхеме.

____Для работы с микросхемами данного семейства, как и других серий CPLD, выпускаемых фирмой Xilinx, не требуется аппаратный программатор. Все операции программирования и обратного считывания конфигурационных данных могут выполняться непосредственно в проектируемой схеме через порт JTAG-интерфейса. При этом полностью поддерживается протокол периферийного сканирования в соответствии со спецификацией стандарта IEEE Std 1149.1 (JTAG). Кроме того, предусмотрена поддержка конфигурирования в системе с напряжением питания 1,8 В по стандарту IEEE Std 1532. Загрузочный кабель, связывающий JTAG-порт с параллельным портом ПК, можно изготовить самостоятельно, воспользовавшись, например, схемой, представленной в документации. Всё что касается данного кабеля будет выложено в последующих постах, с подробным описанием.

____Микросхемы ПЛИС рассматриваемого семейства производятся с использованием расширенного типового ряда корпусов, который включает в себя Chip Scale Packege (CSP), BGA, Fine Line BGA, TQFP, PQFP, VQFP и PLCC. Все микросхемы обладают совместимостью по выводам в случае использования одинаковых корпусов. Применяемые разновидности корпусов для каждого типа микросхем с указанием числа доступных пользовательских выводов приведены в таблице ниже.

____Ниже представлена таблица из datasheet.

Package Drawings:

Скачать: PK076 - QFG32/QFG48 - Package Drawing.

Скачать: PK012 - VQ44/VQG44 - Package Drawing.

Скачать: PK013 - CP56/CPG56 - Package Drawing.

Скачать: PK012 - VQ100/VQG100 - Package Drawing.

____Высокая надёжность микросхем обеспечивает не менее 1000 циклов перепрограммирования и гарантированный срок хранения запрограммированной конфигурации не менее 20 лет.

____Применение микросхем ПЛИС фирмы Xilinx семейства CPLD позволяет избежать дополнительных затрат на приобретение программных средств для разработки проектов и конфигурирования микросхем. Полнофункциональная свободно распространяемая система автоматического проектирования WebPACK ISE (Integrated Synthesis Environment) поддерживает семейство CoolRunner-II в полном объёме.

____Основные параметры микросхем ПЛИС, входящих в семейство CoolRunner-II, представлены в таблице ниже:

____Ниже представлена таблица из datasheet.

Архитектура.

____Обобщённая архитектура микросхем ПЛИС семейства CoolRunner-II представлена на рисунке ниже. Её основу составляют совокупность функциональных блоков (Function Block, FB), блоков ввода/вывода (Input/Output block, IOB) и быстродействующая переключающая матрица AIM. Число функциональных блоков и блоков ввода/вывода определяется типом микросхемы ПЛИС. Несмотря на схожесть с типовой архитектурой ПЛИС семейств CPLD, структура принципиально отличается способом реализации её элементов.

____В функциональных блоках сосредоточены основные логические ресурсы микросхем. Каждый функциональный блок имеет 40 входов, подключённых к выводам переключающей матрицы, и 16 "быстрых" входов, которые соединены непосредственно с блоками ввода/вывода. Кроме того, к функциональным блокам подведено четыре глобальных сигнала: сигнал сброса и установки GSR и три тактовых сигнала GCK0 - GCK2. Структура функционального блока включает в себя программируемую матрицу логических произведений и 16 независимых макроячеек. Используется программируемая матрица логических произведений типа PLA (Programmable Logic Array). Принципиальные отличия её от PAL-матриц, применяемых в большинстве ПЛИС семейств CPLD, мы рассмотрим в отдельном посте, позже.Применение PLA-матрицы позволяет оптимизировать разделение и совместное использование ресурсов микросхемы при реализации проекта. Её 40 прямых и инверсных входов соединены непосредственно с выходами переключающей матрицы. PLA-матрица логических произведений позволяет сформировать 56 термов, часть которых может использоваться в качестве управляющих сигналов, доступных для любой макроячейки функционального блока. Эти сигналы выполняют функции тактирования, сброса и установки триггеров макроячеек, а также разрешения выходов микросхемы.

____Структура макроячейки показана на рисунке ниже вместе с программируемой матрицей логических произведений.

____Каждая макроячейка может быть сконфигурирована для выполнения комбинаторной и регистровой функции, причём триггер, входящий в её состав, может быть реализован как D- или Т-триггер или как защёлка. Кроме того, он может быть сконфигурирован как триггер, тактируемый фронтом и спадом сигнала синхронизации. При реализации только комбинаторной функции триггер не используется. В состав макроячейки также входят элементы, позволяющие реализовать, при необходимости, режим асинхронного сброса и установки триггера. При этом в качестве сигналов сброса и установки могут использоваться сформированные PLA-матрицей термы (PTA), управляющие термы (CTR и CTS соответственно) и глобальный сигнал сброса/установки (GSR). Следует обратить внимание на то, что сигналы управляющих термов CTR и CTS являются общими для всех макроячеек одного функционального блока, а глобальный сигнал сброса/установки GSR - общим для всех функциональных блоков микросхемы.

____Помимо входов, соединённых с выходами PLA-матрицы логических произведений, макроячейка содержит дополнительный, так называемый "быстрый" вход, подключённый непосредственно к блокам ввода/вывода. Тем самым предоставляется возможность использования триггера, входящего в состав макроячейки, в качестве входного триггера или защёлки. При этом комбинаторные функции макроячейки сохраняются.

____Результирующие сигналы с выходов макроячеек поступают в блоки ввода/вывода и на входы высокоскоростной переключающей матрицы AIM, которая позволяет передать их далее на входы других функциональных блоков. На остальные её входы подаются сигналы, поступающие из блоков ввода/вывода, которые затем направляются ко входам функциональных блоков микросхемы. Переключающая матрица AIM обеспечивает необходимую коммутацию сигналов, поступающих из блоков ввода/вывода, входных и выходных сигналов функциональных блоков, при минимальной потребляемой мощности в сочетании с высоким быстродействием.

____Блоки ввода/вывода предназначены для организации интерфейса между внутренними сигналами микросхемы и выводами ПЛИС. Они выполняют функцию буферизации всех входных и выходных сигналов, управления выходами и формирования программируемого "общего" вывода. Структура блока ввода/вывода показана на рисунке ниже.

____Помимо входного и выходного буферных элементов в состав блоков ввода/вывода входит триггер Шмитта, предназначенный для выборочного использования с целью уменьшения уровня помех на входных контактах микросхемы. Структура блоков ввода/вывода включает также высокоомный подтягивающий резистор PullUP и цепь удержания последнего состояния Bus Hold. Выходные цепи обеспечивают возможность формирования выходов, функционирующих в обычном режиме, с открытым стоком или с тремя состояниями (высокоимпедансное состояние). Кроме того, они выполняют функцию управления длительностью фронтов выходных сигналов.

____Характерной особенностью блоков ввода/вывода является поддержка ряда широко используемых стандартов цифровых сигналов, позволяющих организовать взаимодействие с внешними элементами высокоскоростной памяти и сопряжение с шинными интерфейсами. Например, стандарт HSTL (High-Speed Transceiver Logic), широко применяется в высокоскоростных интерфейсах памяти, а SSTL (Stub-Series Terminated Logic) - при реализации шинных интерфейсов. Некоторые из поддерживаемых стандартов требуют подачи дополнительного внешнего напряжения порогового уровня входных каскадов. В таблице ниже приведён список стандартов цифровых сигналов, поддерживаемых блоками ввода/вывода, с указанием значений напряжения питания выходных каскадов VCCIO и порогового уровня входных каскадов VREF.

____Ниже представлена таблица из datasheet.

____Все блоки ввода/вывода сгруппированы в виде банков, число которых определяется типом микросхемы. Каждый пользовательский вывод ПЛИС может быть сконфигурирован в соответствии с выбранным стандартом. При этом следует учитывать, что в рамках одного банка ввода/вывода одновременно могут быть реализованы только стандарты, требующие одно значение напряжения питания выходных каскадов VCCIO.

____Контроллер периферийного сканирования и программирования в системе обеспечивает выполнение операций конфигурирования микросхемы и периферийного сканирования через порт JTAG-интерфейса.

***

.

Последний раз редактировалось: Viktor2312 (Ср Июн 19 2019, 13:37), всего редактировалось 19 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

2

.

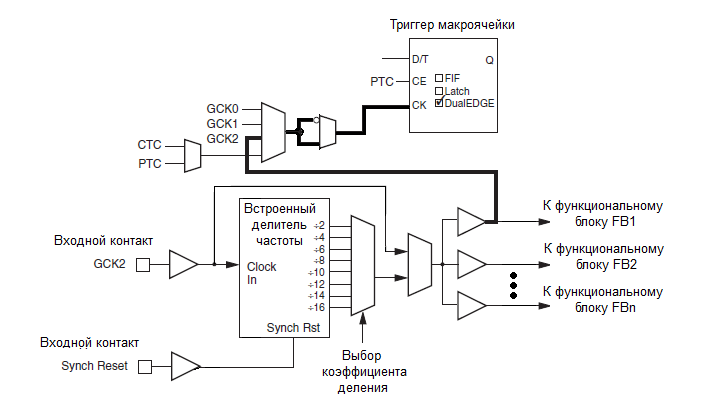

____В состав микросхем ПЛИС содержащих 128 и более макроячеек, кроме основных элементов, входит встроенный делитель частоты тактового сигнала. Этот модуль, выполняющий деление частоты входного сигнала на 2, 4, 6, 8, 10, 12, 14 и 16, сопряжён с одним из трёх контактов микросхемы, которые предназначены для подключения глобальных тактовых сигналов, а именно, с выводом GCK2. Встроенный делитель позволяет получить внутренний тактовый сигнал с требуемым значением частоты, не используя основных логических ресурсов микросхемы (макроячеек). Структурная схема приведённая на рисунке ниже, иллюстрирует процесс формирования внутреннего сигнала синхронизации. Внешний тактовый сигнал, поступающий на контакт ПЛИС GCK2 через буферный элемент, связанный с глобальной цепью синхронизации, передаётся на вход встроенного делителя частоты. С выхода делителя сигнал с выбранным значением частоты через глобальные цепи распределяется по всем функциональным блокам микросхемы. Глобальные цепи обеспечивают распространение тактовых сигналов внутри микросхем без временных перекосов.

____Встроенный делитель частоты содержит вход синхронного сброса с активным высоким логическим уровнем сигнала. Сигнал сброса может подаваться через специально выделенный контакт микросхемы CDRST. При переключении сигнала на входе сброса в состояние высокого логического уровня выход делителя частоты блокируется после завершения текущего цикла. При подаче питания ПЛИС выход устанавливается в состояние низкого логического уровня.

____В состав встроенного делителя частоты также входит схема генерации начальной задержки, которая позволяет после выполнения процедуры сброса или включения питания микросхемы внести дополнительный временной сдвиг на выходе, длительность которого равна одному полному периоду формируемого тактового сигнала. На рисунке ниже показаны временные диаграммы, поясняющие процесс получения внутренних тактовых сигналов без задержки и с начальным временным сдвигом путём деления частоты входного сигнала синхронизации на 2 и на 16.

____Средства разработки и синтеза проектов серии ISE (Integrated Synthesis Environment) содержат группу компонентов, которые позволяют достаточно просто реализовать различные режимы функционирования встроенного делителя частоты тактового сигнала. Эти компоненты могут использоваться как при схемотехническом представлении проектируемого устройства, так и при использовании языков описания аппаратуры высокого уровня HDL (Hardware Description Language), например, VHDL. Для каждого режима работы делителя предусмотрен соответствующий компонент.

____Компоненты, обозначения которых соответствуют шаблону CLK_DIVn (CLK_DIV2, CLK_DIV4, CLK_DIV6, CLK_DIV8, CLK_DIV10, CLK_DIV12, CLK_DIV14, CLK_DIV16), представляют делитель частоты с соответствующим коэффициентом деления, который не использует вход асинхронного сброса и цепи начальной задержки формируемого сигнала. На рисунке ниже приведена схема формирования внутреннего тактового сигнала из внешнего сигнала синхронизации, выполненная на основе этих компонентов в схемотехническом редакторе. Буферный элемент который должен находиться между входным контактом ПЛИС GCK2 и соответствующим входом встроенного делителя частоты, можно не устанавливать. Средства синтеза XST автоматически выполняют требуемых буферных элементов во входные и выходные цепи схемы проектируемого устройства.

____Ниже показан образец применения компонентов CLK_DIVn в составе VHDL-описания проектируемого устройства. Вместо n следует указать требуемый коэффициент деления. Порт CLKIN соответствует входу внешнего тактового сигнала, поступающего с контакта ПЛИС GCK2, а CLKDV - выходу делителя, с которого снимается внутренний тактовый сигнал.

____В качестве примера далее приведено описание на языке VHDL встроенного делителя частоты сигнала clk_in без входа синхронного сброса и начального временного сдвига, функционирующего в режиме деления на 2.

____Компоненты с названиями вида CLK_DIVnR (CLK_DIV2R, CLK_DIV4R, CLK_DIV6R, CLK_DIV8R, CLK_DIV10R, CLK_DIV12R, CLK_DIV14R, CLK_DIV16R) позволяют сконфигурировать делитель частоты с соответствующим коэффициентом деления n и асинхронным сбросом, формирующий выходной сигнал без начальной задержки. Применение указанных компонентов в схемотехнической форме отображено на рисунке ниже.

____В приведённом ниже фрагменте показан способ использования компонентов CLK_DIVnR при описании устройства с использованием языка VHDL. Порт CDRST соответствует входу сигнала сброса.

____Например, следующий фрагмент описания представляет встроенный делитель частоты тактового сигнала clk_in на 16 со входом сброса div_reset.

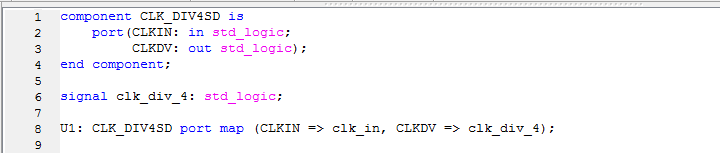

____Компоненты, идентификаторы которых имеют вид CLK_DIVnSD (CLK_DIV2SD, CLK_DIV4SD, CLK_DIV6SD, CLK_DIV8SD, CLK_DIV10SD, CLK_DIV12SD, CLK_DIV14SD, CLK_DIV16SD), предназначены для реализации в составе проекта встроенного делителя частоты с указанным коэффициентом деления n и начальной задержкой выходного сигнала на один период. Указанные компоненты применяются в составе схем и модулей HDL-описаний в той же форме, что и компоненты CLK_DIVn. Например, для формирования внутреннего тактового сигнала clk_div_4 (путём четырёхкратного деления частоты входного сигнала синхронизации clk_in) с начальным запаздыванием на один период следует включить в состав VHDL-описания следующие выражения декларации и создания экземпляра компонента CLK_DIV4SD.

____Для включения в состав проекта встроенного делителя частоты с требуемым коэффициентом деления, асинхронным сбросом и начальной задержкой выходного сигнала следует использовать компоненты с названиями вида CLK_DIVnRSD (CLK_DIV2RSD, CLK_DIV4RSD, CLK_DIV6RSD, CLK_DIV8RSD, CLK_DIV10RSD, CLK_DIV12RSD, CLK_DIV14RSD, CLK_DIV16RSD). Способ их применения в схемах и модулях HDL-описаний тот же, что и для компонентов CLK_DIVnR. Использование компонентов CLK_DIVnRSD в составе исходного модуля проекта, написанного на языке VHDL, иллюстрирует описание восьмикратного делителя тактовой частоты с асинхронным сбросом и начальной задержкой формируемого сигнала.

____Методика CoolCLOCK, предлагаемая фирмой Xilinx, направлена на снижение мощности, потребляемой в динамическом режиме микросхемами с числом макроячеек 128 и более. Предпосылками создания этой методики явились такие архитектурные особенности указанных микросхем ПЛИС, как наличие встроенного делителя частоты тактового сигнала и и возможность конфигурирования триггеров, тактируемых фронтом и спадом сигнала синхронизации.

____Значение тока, потребляемого микросхемой от источника питания в динамическом режиме, напрямую зависит от частоты сигналов устройства, проектируемого на его основе. Использование методики CoolCLOCK позволяет добиться значительного уменьшения потребляемой мощности ПЛИС за счёт двукратного понижения частоты внутреннего сигнала синхронизации, которое выполняется встроенным делителем частоты. При этом требуемая производительность проектируемого устройства достигается за счёт использования в макроячейках триггеров, управляемых фронтом и спадом тактового сигнала. Следует обратить внимание на то, что применение CoolCLOCK возможно только по отношению к сигналу синхронизации, поступающему со входа ПЛИС GCK2. Как уже упоминалось, только этот контакт микросхемы сопряжён со входом встроенного делителя частоты тактового сигнала.

____Структурная схема, приведённая на рисунке ниже, наглядно иллюстрирует реализацию методики CoolCLOCK. Внешний тактовый сигнал, который подаётся на входной контакт микросхемы GCK2, поступает на вход встроенного делителя частоты. С выхода делителя снимается внутренний сигнал синхронизации, частота которого в два раза ниже, чем у внешнего тактового сигнала. Далее внутренний тактовый сигнал через глобальные цепи ПЛИС передаётся на соответствующие входы макроячеек, используемых в проекте. В этих макроячейках триггерный элемент конфигурируется как триггер, тактируемый фронтом и спадом сигнала синхронизации.

____Для применения методики CoolCLOCK в разрабатываемых проектах достаточно присвоить атрибут COOL_CLK входной цепи синхронизации, подключённой к контакту ПЛИС GCK2. Этот атрибут может быть указан в файле временных и топологических ограничений проекта UCF (User Constraint File) или непосредственно в модуле исходного описания на используемом языке HDL. Применение файла UCF является в большинстве случаев наиболее универсальным способом установки атрибутов, так как сочетается с различными формами описания проектируемого устройства. Формат атрибута COOL_CLK, применяемый в файле UCF, имеет следующий вид:

NET <название_цепи_синхронизации> COOL_CLK;

Например:

NET clk_ext COOL_CLK;

____Чтобы задать атрибут COOL_CLK непосредственно в модуле исходного VHDL-описания, необходимо включить в него выражения, имеющие следующий формат:

attribute COOL_CLK: string;

attribute COOL_CLK of <название_цепи_синхронизации>: signal is "TRUE";

Например,

____При обнаружении указанного атрибута в файле временных и топологических ограничений или в модуле исходного описания проекта программа синтеза XST автоматически включает в состав синтезированного описания проектируемого устройства встроенный делитель частоты тактового сигнала, работающий в режиме деления на два. Кроме того, все триггеры макроячеек, на который подаётся сформированный сигнал синхронизации с пониженной частотой, автоматически синтезируются как элементы, тактируемые фронтом и спадом этого сигнала.

____Дополнительным способом сокращения потребляемой мощности микросхемами данного семейства, содержащих 128 и более макроячеек, является использование запатентованной технологии DataGATE. В её основе лежит возможность управления блокировкой входных сигналов, поступающих на контакты микросхемы. Если значения входных сигналов используются в проектируемом устройстве только в определённые моменты времени, то в остальные, достаточно продолжительные временные интервалы, эти сигналы могут быть заблокированы при использовании специальных ресурсов микросхемы. Тем самым снижается потребляемая мощность в соответствующих цепях ПЛИС. Применение функции DataGATE даёт заметный выигрыш в снижении потребляемой мощности при реализации различных шинных интерфейсов.

____Рисунок представленный ниже поясняет принцип технологии DataGATE на примере одной входной цепи микросхемы. В каждой входной цепи ПЛИС, между входным буфером и входом быстродействующей переключающей матрицы AIM предусмотрен управляемый ключ и регистр защёлка. Для каждой входной цепи проекта в конфигурационной последовательности, загружаемой в микросхему, имеется соответствующий бит данных, значение которого определяет, будет ли использована функция управления этого ключа. Если функция DataGATE активизирована, то при наличии активного уровня управляющего сигнала производится блокировка этой входной цепи, а значение входного информационного сигнала в момент блокировки записывается в регистр-защёлку.

____Для применения функции DataGATE в разрабатываемом проекте предназначены два атрибута. Первый из них, DATA_GATE, определяет название входной цепи, для которой используется функция. Этот атрибут, как и COOL_CLK, может задаваться в файле временных и топологических ограничений UFC или непосредственно в модуле исходного HDL-описания проекта. Формат строки, устанавливающей атрибут DATA_GATE в файле UFC, имеет следующий вид:

NET <название_входной_цепи> DATA_GATE;

____Например,

NET data_input DATA_GATE;

____Синтаксис выражений, задающих атрибут DATA_GATE в модуле исходного VHDL-описания, выглядит следующим образом:

attribute DATA_GATE: string;

attribute DATA_GATE of <название_входной_цепи>: signal is "TRUE";

____Например,

attribute DATA_GATE: string;

attribute DATA_GATE of data_input: signal is "TRUE";

____Следует обратить внимание на то, что, если в файле исходного описания атрибут DATA_GATE задаётся для нескольких входных цепей, то строка объявления этого атрибута указывается только один раз.

____Второй атрибут BUFG=DATA_GATE, задаёт название цепи, сигнал которой управляет процессом блокировки входных цепей DataGATE Enable (DGE). В качестве управляющего может использоваться любой сигнал, поступающий на контакты ввода/вывода микросхемы, или формируемый внутри ПЛИС. В файле временных и топологических ограничений проекта этот атрибут указывается с помощью строки, формат которой имеет следующий вид:

NET <название_цепи_управляющего_сигнала> BUFG=DATA_GATE;

____Например,

NET dg_en BUFG=DATA_GATE;

____В модуле исходного описания проекта на языке VHDL для определения названия цепи управляющего сигнала DGE при реализации функции DataGATE используется следующая последовательность выражений:

attribute BUFG: string;

attribute BUFG of <название_цепи_управляющего_сигнала>: signal is "DATA_GATE";

____Например,

attribute BUFG: string;

attribute BUFG of dg_en: signal is "DATA_GATE";

Скачать: White Papers. DataGATE.

____Для использования во входных цепях встроенных триггеров Шмитта, расположенных в блоках ввода/вывода и предназначенных для снижения уровня помех, необходимо присвоить атрибут SCHMITT_TRIGGER соответствующей цепи, подключённой к входному пользовательскому контакту микросхемы. Формат строки, устанавливающий этот атрибут в файле UCF, выглядит следующим образом:

NET <название_входной_цепи> SCHMITT_TRIGGER;

____Например,

NET data_in SCHMITT_TRIGGER;

NET clock SCHMITT_TRIGGER;

____Для установки атрибута SCHMITT_TRIGGER в модуле VHDL-исходного описания проекта следует использовать выражения:

attribute SCHMITT_TRIGGER: string;

attribute SCHMITT_TRIGGER of <название_входной_цепи>: signal is "true";

____Например,

attribute SCHMITT_TRIGGER: string;

attribute SCHMITT_TRIGGER of data_in: signal is "true";

____При установке триггеров Шмитта в нескольких входных цепях достаточно одного выражения декларации атрибута SCHMITT_TRIGGER.

____Средства синтеза XST при обнаружении атрибута SCHMITT_TRIGGER автоматически включают в состав указанных входных цепей синтезированного описания проектируемого устройства триггеры Шмитта.

.

Формирование тактовых сигналов с использованием встроенного делителя частоты.

____В состав микросхем ПЛИС содержащих 128 и более макроячеек, кроме основных элементов, входит встроенный делитель частоты тактового сигнала. Этот модуль, выполняющий деление частоты входного сигнала на 2, 4, 6, 8, 10, 12, 14 и 16, сопряжён с одним из трёх контактов микросхемы, которые предназначены для подключения глобальных тактовых сигналов, а именно, с выводом GCK2. Встроенный делитель позволяет получить внутренний тактовый сигнал с требуемым значением частоты, не используя основных логических ресурсов микросхемы (макроячеек). Структурная схема приведённая на рисунке ниже, иллюстрирует процесс формирования внутреннего сигнала синхронизации. Внешний тактовый сигнал, поступающий на контакт ПЛИС GCK2 через буферный элемент, связанный с глобальной цепью синхронизации, передаётся на вход встроенного делителя частоты. С выхода делителя сигнал с выбранным значением частоты через глобальные цепи распределяется по всем функциональным блокам микросхемы. Глобальные цепи обеспечивают распространение тактовых сигналов внутри микросхем без временных перекосов.

____Встроенный делитель частоты содержит вход синхронного сброса с активным высоким логическим уровнем сигнала. Сигнал сброса может подаваться через специально выделенный контакт микросхемы CDRST. При переключении сигнала на входе сброса в состояние высокого логического уровня выход делителя частоты блокируется после завершения текущего цикла. При подаче питания ПЛИС выход устанавливается в состояние низкого логического уровня.

____В состав встроенного делителя частоты также входит схема генерации начальной задержки, которая позволяет после выполнения процедуры сброса или включения питания микросхемы внести дополнительный временной сдвиг на выходе, длительность которого равна одному полному периоду формируемого тактового сигнала. На рисунке ниже показаны временные диаграммы, поясняющие процесс получения внутренних тактовых сигналов без задержки и с начальным временным сдвигом путём деления частоты входного сигнала синхронизации на 2 и на 16.

____Средства разработки и синтеза проектов серии ISE (Integrated Synthesis Environment) содержат группу компонентов, которые позволяют достаточно просто реализовать различные режимы функционирования встроенного делителя частоты тактового сигнала. Эти компоненты могут использоваться как при схемотехническом представлении проектируемого устройства, так и при использовании языков описания аппаратуры высокого уровня HDL (Hardware Description Language), например, VHDL. Для каждого режима работы делителя предусмотрен соответствующий компонент.

____Компоненты, обозначения которых соответствуют шаблону CLK_DIVn (CLK_DIV2, CLK_DIV4, CLK_DIV6, CLK_DIV8, CLK_DIV10, CLK_DIV12, CLK_DIV14, CLK_DIV16), представляют делитель частоты с соответствующим коэффициентом деления, который не использует вход асинхронного сброса и цепи начальной задержки формируемого сигнала. На рисунке ниже приведена схема формирования внутреннего тактового сигнала из внешнего сигнала синхронизации, выполненная на основе этих компонентов в схемотехническом редакторе. Буферный элемент который должен находиться между входным контактом ПЛИС GCK2 и соответствующим входом встроенного делителя частоты, можно не устанавливать. Средства синтеза XST автоматически выполняют требуемых буферных элементов во входные и выходные цепи схемы проектируемого устройства.

____Ниже показан образец применения компонентов CLK_DIVn в составе VHDL-описания проектируемого устройства. Вместо n следует указать требуемый коэффициент деления. Порт CLKIN соответствует входу внешнего тактового сигнала, поступающего с контакта ПЛИС GCK2, а CLKDV - выходу делителя, с которого снимается внутренний тактовый сигнал.

____В качестве примера далее приведено описание на языке VHDL встроенного делителя частоты сигнала clk_in без входа синхронного сброса и начального временного сдвига, функционирующего в режиме деления на 2.

____Компоненты с названиями вида CLK_DIVnR (CLK_DIV2R, CLK_DIV4R, CLK_DIV6R, CLK_DIV8R, CLK_DIV10R, CLK_DIV12R, CLK_DIV14R, CLK_DIV16R) позволяют сконфигурировать делитель частоты с соответствующим коэффициентом деления n и асинхронным сбросом, формирующий выходной сигнал без начальной задержки. Применение указанных компонентов в схемотехнической форме отображено на рисунке ниже.

____В приведённом ниже фрагменте показан способ использования компонентов CLK_DIVnR при описании устройства с использованием языка VHDL. Порт CDRST соответствует входу сигнала сброса.

____Например, следующий фрагмент описания представляет встроенный делитель частоты тактового сигнала clk_in на 16 со входом сброса div_reset.

____Компоненты, идентификаторы которых имеют вид CLK_DIVnSD (CLK_DIV2SD, CLK_DIV4SD, CLK_DIV6SD, CLK_DIV8SD, CLK_DIV10SD, CLK_DIV12SD, CLK_DIV14SD, CLK_DIV16SD), предназначены для реализации в составе проекта встроенного делителя частоты с указанным коэффициентом деления n и начальной задержкой выходного сигнала на один период. Указанные компоненты применяются в составе схем и модулей HDL-описаний в той же форме, что и компоненты CLK_DIVn. Например, для формирования внутреннего тактового сигнала clk_div_4 (путём четырёхкратного деления частоты входного сигнала синхронизации clk_in) с начальным запаздыванием на один период следует включить в состав VHDL-описания следующие выражения декларации и создания экземпляра компонента CLK_DIV4SD.

____Для включения в состав проекта встроенного делителя частоты с требуемым коэффициентом деления, асинхронным сбросом и начальной задержкой выходного сигнала следует использовать компоненты с названиями вида CLK_DIVnRSD (CLK_DIV2RSD, CLK_DIV4RSD, CLK_DIV6RSD, CLK_DIV8RSD, CLK_DIV10RSD, CLK_DIV12RSD, CLK_DIV14RSD, CLK_DIV16RSD). Способ их применения в схемах и модулях HDL-описаний тот же, что и для компонентов CLK_DIVnR. Использование компонентов CLK_DIVnRSD в составе исходного модуля проекта, написанного на языке VHDL, иллюстрирует описание восьмикратного делителя тактовой частоты с асинхронным сбросом и начальной задержкой формируемого сигнала.

Применение методики CoolCLOCK.

____Методика CoolCLOCK, предлагаемая фирмой Xilinx, направлена на снижение мощности, потребляемой в динамическом режиме микросхемами с числом макроячеек 128 и более. Предпосылками создания этой методики явились такие архитектурные особенности указанных микросхем ПЛИС, как наличие встроенного делителя частоты тактового сигнала и и возможность конфигурирования триггеров, тактируемых фронтом и спадом сигнала синхронизации.

____Значение тока, потребляемого микросхемой от источника питания в динамическом режиме, напрямую зависит от частоты сигналов устройства, проектируемого на его основе. Использование методики CoolCLOCK позволяет добиться значительного уменьшения потребляемой мощности ПЛИС за счёт двукратного понижения частоты внутреннего сигнала синхронизации, которое выполняется встроенным делителем частоты. При этом требуемая производительность проектируемого устройства достигается за счёт использования в макроячейках триггеров, управляемых фронтом и спадом тактового сигнала. Следует обратить внимание на то, что применение CoolCLOCK возможно только по отношению к сигналу синхронизации, поступающему со входа ПЛИС GCK2. Как уже упоминалось, только этот контакт микросхемы сопряжён со входом встроенного делителя частоты тактового сигнала.

____Структурная схема, приведённая на рисунке ниже, наглядно иллюстрирует реализацию методики CoolCLOCK. Внешний тактовый сигнал, который подаётся на входной контакт микросхемы GCK2, поступает на вход встроенного делителя частоты. С выхода делителя снимается внутренний сигнал синхронизации, частота которого в два раза ниже, чем у внешнего тактового сигнала. Далее внутренний тактовый сигнал через глобальные цепи ПЛИС передаётся на соответствующие входы макроячеек, используемых в проекте. В этих макроячейках триггерный элемент конфигурируется как триггер, тактируемый фронтом и спадом сигнала синхронизации.

____Для применения методики CoolCLOCK в разрабатываемых проектах достаточно присвоить атрибут COOL_CLK входной цепи синхронизации, подключённой к контакту ПЛИС GCK2. Этот атрибут может быть указан в файле временных и топологических ограничений проекта UCF (User Constraint File) или непосредственно в модуле исходного описания на используемом языке HDL. Применение файла UCF является в большинстве случаев наиболее универсальным способом установки атрибутов, так как сочетается с различными формами описания проектируемого устройства. Формат атрибута COOL_CLK, применяемый в файле UCF, имеет следующий вид:

NET <название_цепи_синхронизации> COOL_CLK;

Например:

NET clk_ext COOL_CLK;

____Чтобы задать атрибут COOL_CLK непосредственно в модуле исходного VHDL-описания, необходимо включить в него выражения, имеющие следующий формат:

attribute COOL_CLK: string;

attribute COOL_CLK of <название_цепи_синхронизации>: signal is "TRUE";

Например,

____При обнаружении указанного атрибута в файле временных и топологических ограничений или в модуле исходного описания проекта программа синтеза XST автоматически включает в состав синтезированного описания проектируемого устройства встроенный делитель частоты тактового сигнала, работающий в режиме деления на два. Кроме того, все триггеры макроячеек, на который подаётся сформированный сигнал синхронизации с пониженной частотой, автоматически синтезируются как элементы, тактируемые фронтом и спадом этого сигнала.

Реализация технологии DataGATE.

____Дополнительным способом сокращения потребляемой мощности микросхемами данного семейства, содержащих 128 и более макроячеек, является использование запатентованной технологии DataGATE. В её основе лежит возможность управления блокировкой входных сигналов, поступающих на контакты микросхемы. Если значения входных сигналов используются в проектируемом устройстве только в определённые моменты времени, то в остальные, достаточно продолжительные временные интервалы, эти сигналы могут быть заблокированы при использовании специальных ресурсов микросхемы. Тем самым снижается потребляемая мощность в соответствующих цепях ПЛИС. Применение функции DataGATE даёт заметный выигрыш в снижении потребляемой мощности при реализации различных шинных интерфейсов.

____Рисунок представленный ниже поясняет принцип технологии DataGATE на примере одной входной цепи микросхемы. В каждой входной цепи ПЛИС, между входным буфером и входом быстродействующей переключающей матрицы AIM предусмотрен управляемый ключ и регистр защёлка. Для каждой входной цепи проекта в конфигурационной последовательности, загружаемой в микросхему, имеется соответствующий бит данных, значение которого определяет, будет ли использована функция управления этого ключа. Если функция DataGATE активизирована, то при наличии активного уровня управляющего сигнала производится блокировка этой входной цепи, а значение входного информационного сигнала в момент блокировки записывается в регистр-защёлку.

____Для применения функции DataGATE в разрабатываемом проекте предназначены два атрибута. Первый из них, DATA_GATE, определяет название входной цепи, для которой используется функция. Этот атрибут, как и COOL_CLK, может задаваться в файле временных и топологических ограничений UFC или непосредственно в модуле исходного HDL-описания проекта. Формат строки, устанавливающей атрибут DATA_GATE в файле UFC, имеет следующий вид:

NET <название_входной_цепи> DATA_GATE;

____Например,

NET data_input DATA_GATE;

____Синтаксис выражений, задающих атрибут DATA_GATE в модуле исходного VHDL-описания, выглядит следующим образом:

attribute DATA_GATE: string;

attribute DATA_GATE of <название_входной_цепи>: signal is "TRUE";

____Например,

attribute DATA_GATE: string;

attribute DATA_GATE of data_input: signal is "TRUE";

____Следует обратить внимание на то, что, если в файле исходного описания атрибут DATA_GATE задаётся для нескольких входных цепей, то строка объявления этого атрибута указывается только один раз.

____Второй атрибут BUFG=DATA_GATE, задаёт название цепи, сигнал которой управляет процессом блокировки входных цепей DataGATE Enable (DGE). В качестве управляющего может использоваться любой сигнал, поступающий на контакты ввода/вывода микросхемы, или формируемый внутри ПЛИС. В файле временных и топологических ограничений проекта этот атрибут указывается с помощью строки, формат которой имеет следующий вид:

NET <название_цепи_управляющего_сигнала> BUFG=DATA_GATE;

____Например,

NET dg_en BUFG=DATA_GATE;

____В модуле исходного описания проекта на языке VHDL для определения названия цепи управляющего сигнала DGE при реализации функции DataGATE используется следующая последовательность выражений:

attribute BUFG: string;

attribute BUFG of <название_цепи_управляющего_сигнала>: signal is "DATA_GATE";

____Например,

attribute BUFG: string;

attribute BUFG of dg_en: signal is "DATA_GATE";

Скачать: White Papers. DataGATE.

Использование встроенного триггера Шмитта во входных цепях.

____Для использования во входных цепях встроенных триггеров Шмитта, расположенных в блоках ввода/вывода и предназначенных для снижения уровня помех, необходимо присвоить атрибут SCHMITT_TRIGGER соответствующей цепи, подключённой к входному пользовательскому контакту микросхемы. Формат строки, устанавливающий этот атрибут в файле UCF, выглядит следующим образом:

NET <название_входной_цепи> SCHMITT_TRIGGER;

____Например,

NET data_in SCHMITT_TRIGGER;

NET clock SCHMITT_TRIGGER;

____Для установки атрибута SCHMITT_TRIGGER в модуле VHDL-исходного описания проекта следует использовать выражения:

attribute SCHMITT_TRIGGER: string;

attribute SCHMITT_TRIGGER of <название_входной_цепи>: signal is "true";

____Например,

attribute SCHMITT_TRIGGER: string;

attribute SCHMITT_TRIGGER of data_in: signal is "true";

____При установке триггеров Шмитта в нескольких входных цепях достаточно одного выражения декларации атрибута SCHMITT_TRIGGER.

____Средства синтеза XST при обнаружении атрибута SCHMITT_TRIGGER автоматически включают в состав указанных входных цепей синтезированного описания проектируемого устройства триггеры Шмитта.

***

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

3

.

____Блоки ввода/вывода предоставляют возможность выборочного использования внутреннего резистора, подключённого к контакту микросхемы и шине питания. Применение встроенных подтягивающих резисторов PullUP позволяет исключить внешние резисторы, подключаемые к выводам ПЛИС, которые предназначены для выполнения аналогичной функции. Тем самым сокращается общее число внешних элементов, что позволяет не только минимизировать размеры печатной платы, но и оптимизировать процесс её трассировки.

____Активизация подтягивающего резистора PullUP, расположенного в блоках ввода/вывода, осуществляется с помощью одноимённого атрибута PULLUP, который присваивается цепи, подключённой к соответствующему контакту микросхемы. В файле временных и топологических ограничений проекта UCF для указания интерфейсной цепи проекта, в которой необходимо задействовать интегрированный резистор PullUP, следует воспользоваться выражением, формат которого имеет вид:

NET <название_цепи> PULLUP;

____Например,

NET data_net PULLUP;

NET clock_net PULLUP;

определяют необходимость подключения встроенного подтягивающего резистора к выводам микросхемы, которые связаны с цепями data_net и clock_net соответственно.

____Установка атрибутов PULLUP может выполняться непосредственно в модулях исходного описания проекта. В описаниях разрабатываемых на языке VHDL, для этого используется следующая конструкция:

attribute PULLUP: string;

attribute PULLUP of <название_сигнала>: signal is "TRUE";

____Если в модуле VHDL-описания необходимо указать несколько сигналов, в цепях которых должен быть активизирован встроенный подтягивающий резистор, достаточно одного выражения декларации атрибута PULLUP. Например, приведённый ниже фрагмент VHDL-кода с точки зрения выполняемых функций эквивалентен рассмотренным выше выражениям ограничений для контактов микросхемы, подключаемых к цепям data_net и clock_net.

attribute PULLUP: string;

attribute PULLUP of data_net: signal is "TRUE";

attribute PULLUP of clock_net: signal is "TRUE";

____Помимо встроенного подтягивающего резистора в блоках ввода/вывода, можно использовать цепь удержания последнего состояния Bus Hold. Работа этой цепи основана на подключении к пользовательскому контакту кристалла резистора, соединённого с шиной питания PullUP или общей шиной PullDown. Тип подключаемого резистора обуславливается последним определённым состоянием сигнала (высокого или низкого логического уровня) на соответствующем выводе ПЛИС.

____Для включения функции удержания последнего состояния сигнала на требуемом контакте микросхемы предусмотрен атрибут KEEPER. Этот атрибут указывается для цепи (сигнала), подключённой к соответствующему выводу ПЛИС. Формат строки, устанавливающей атрибут KEEPER в файле временных и топологических ограничений проекта UCF, имеет вид:

NET <название_цепи> KEEPER;

____Например, выражения

NET data_net KEEPER;

и

NET clock_net KEEPER;

предписывают подключить цепь удержания последнего состояния Bus Hold для пользовательских выводов ПЛИС, подключаемых к цепям data_net и clock_net соответственно.

____Чтобы непосредственно в файле VHDL-описания определить выводы микросхемы, для которых должна быть активизирована цепь удержания последнего состояния, нужно с помощью атрибута KEEPER указать названия соответствующих сигналов проектируемого устройства. Выражения, описывающие этот атрибут в составе VHDL-описания, выглядят следующим образом:

attribute KEEPER: string;

attribute KEEPER of <название_сигнала>: signal is "TRUE";

____Строка декларации атрибута KEEPER, как и в предыдущих случаях, должна присутствовать в описании в единичном экземпляре, независимо от числа сигналов, для которых устанавливается этот атрибут. Например:

attribute KEEPER: string;

attribute KEEPER of data_net: signal is "TRUE";

attribute KEEPER of clock_net: signal is "TRUE";

____Если в проекте, предполагается использование одного стандарта ввода/вывода, то вид требуемого стандарта можно указать сразу для всех пользовательских контактов микросхемы при выполнении этапа реализации. Эта операция выполняется в среде управляющей оболочки средств проектирование ISE - Навигатора проекта. Для выбора требуемого стандарта ввода/вывода следует воспользоваться выпадающим меню параметра Output Voltage Standard, который находится в окне Process Properties. Этот параметр позволяет установить стандарт ввода/вывода, используемый по умолчанию в процессе реализации проекта.

____Конфигурирование отдельных пользовательских выводов микросхемы в соответствии с требуемым стандартом ввода/вывода осуществляется с помощью атрибута IOSTANDARD. Этот атрибут присваивается входной или выходной цепи (сигналу), подключённой к соответствующему выводу ПЛИС. Каждому стандарту ввода/вывода соответствует индивидуальное значение атрибута IOSTANDARD. В таблице ниже приведён список значений этого атрибута для всех стандартов ввода/вывода, поддерживаемых микросхемами семейства CoolRunner-II. При установке значения атрибута IOSTANDARD следует убедиться, что выбранный стандарт поддерживается микросхемой, используемой для реализации проекта.

____Для установки требуемого значения атрибута IOSTANDARD в файле временных и топологических ограничений проекта UCF используется следующий формат строки:

NET <название_цепи> IOSTANDARD = <значение_атрибута_IOSTANDARD_для_соответствующего_стандарта_ввода/вывода>;

____Например, выражения

NET data_in IOSTANDARD = LVCMOS18;

и

NET clock IOSTANDARD = LVCMOS18;

определяют режим конфигурирования выводов микросхемы, связанных с цепями data_in и clock, в соответствии с спецификацией стандарта LVCMOS 1.8 V.

____Чтобы указать требуемые стандарты ввода/вывода для отдельных контактов ПЛИС в модуле исходного описания на языке VHDL, нужно воспользоваться конструкцией, представленной ниже.

attribute IOSTANDARD: string;

attribute IOSTANDARD of <название_сигнала>: signal is "<значение_атрибута_IOSTANDARD_для_соответствующего_стандарта_ввода/вывода>";

____В качестве примера далее приведён фрагмент VHDL-описания, в котором для выводов микросхемы, используемых для подключения сигналов data_in и clock, устанавливается соответствие требованиям стандарту LVCMOS 1.8 V.

attribute IOSTANDARD: string;

attribute IOSTANDARD of data_in: signal is "LVCMOS18";

attribute IOSTANDARD of clock: signal is "LVCMOS18";

____Независимо от используемого стандарта ввода/вывода любой выходной контакт микросхемы может быть сконфигурирован по схеме с открытым стоком. Эта операция выполняется путём присвоения атрибута OPEN_DRAIN соответствующей выходной цепи проектируемого устройства. Синтаксис выражения, предназначенного для установки этого атрибута в файле UCF, имеет следующий вид:

NET <название цепи> OPEN_DRAIN;

Строка

NET data_out OPEN_DRAIN;

определяет контакт микросхемы, к которому подключена цепь с названием data_out как выход с открытым стоком.

____Назначение атрибута OPEN_DRAIN непосредственно в составе VHDL-описания выполняется с помощью конструкции, формат которой выглядит следующим образом:

attribute OPEN_DRAIN: string;

attribute OPEN_DRAIN of <название_сигнала>: signal is "TRUE";

____Вместо приведённого выше выражения ограничения для цепи data_out в файле UCF можно использовать следующую последовательность строк в модуле исходного описания на языке VHDL:

attribute OPEN_DRAIN: string;

attribute OPEN_DRAIN of data_out: signal is "TRUE";

____Временная модель микросхем ПЛИС данного семейства может быть наглядно отображена в виде структурной схемы, каждый элемент которой соответствует временным параметрам распространения сигналов через определённые ресурсы микросхемы. Графическое представление временной модели представлено на рисунке ниже.

____Значения параметров используются в качестве исходных данных программами моделирования и статического анализа, входящими в состав средств проектирования. Полные отчёты, содержащие значения временных характеристик проектируемого устройства, могут быть сформированы системой проектирования только после завершения этапа размещения и трассировки проекта в микросхеме, когда становятся известными ресурсы ПЛИС, используемые для реализации проекта, и маршруты распространения сигналов внутри микросхемы.

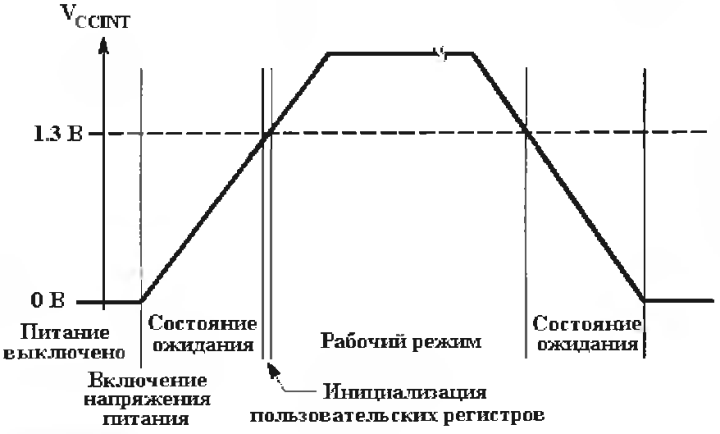

____Микросхемы ПЛИС программируются и перепрограммируются в системе (in system programmable, ISP) с напряжением питания 1,8 В. Все внутренние напряжения, необходимые для программирования микросхемы, формируются встроенными узлами из напряжения питания ядра ПЛИС, номинальное значение которого составляет 1,8 В. При этом следует учитывать, что для питания буферных элементов порта JTAG-интерфейса требуется дополнительное напряжение VCCAUX, которое подаётся через специально выделенный для этого контакт микросхемы. Допустимое значение этого напряжения находится в диапазоне от 1,7 до 3,6 В.

____Все операции периферийного сканирования и программирования в системе выполняются через порт интерфейса JTAG микросхемы. Для программирования используются только четыре сигнала из совокупности, описанной в спецификации стандарта JTAG (IEEE Standard 1149.1). Эти сигналы поступают на одноимённые контакты микросхемы:

____Для программирования микросхем ПЛИС достаточно подключить загрузочный кабель к соответствующему порту компьютера (параллельному LPT или последовательному COM, USB в зависимости от типа используемого кабеля) и контактам JTAG-порта микросхемы. Операции загрузки конфигурационной последовательности разрабатываемого проекта в микросхему ПЛИС и обратного считывания данных выполняются с помощью модуля программирования iMPACT, который входит в состав средств проектирования ISE.

____Микросхемы ПЛИС семейства CoolRunner-II поддерживают следующие команды периферийного сканирования JTAG-интерфейса:

.

Использование встроенного подтягивающего резистора PullUP

в блоках ввода/вывода.

в блоках ввода/вывода.

____Блоки ввода/вывода предоставляют возможность выборочного использования внутреннего резистора, подключённого к контакту микросхемы и шине питания. Применение встроенных подтягивающих резисторов PullUP позволяет исключить внешние резисторы, подключаемые к выводам ПЛИС, которые предназначены для выполнения аналогичной функции. Тем самым сокращается общее число внешних элементов, что позволяет не только минимизировать размеры печатной платы, но и оптимизировать процесс её трассировки.

____Активизация подтягивающего резистора PullUP, расположенного в блоках ввода/вывода, осуществляется с помощью одноимённого атрибута PULLUP, который присваивается цепи, подключённой к соответствующему контакту микросхемы. В файле временных и топологических ограничений проекта UCF для указания интерфейсной цепи проекта, в которой необходимо задействовать интегрированный резистор PullUP, следует воспользоваться выражением, формат которого имеет вид:

NET <название_цепи> PULLUP;

____Например,

NET data_net PULLUP;

NET clock_net PULLUP;

определяют необходимость подключения встроенного подтягивающего резистора к выводам микросхемы, которые связаны с цепями data_net и clock_net соответственно.

____Установка атрибутов PULLUP может выполняться непосредственно в модулях исходного описания проекта. В описаниях разрабатываемых на языке VHDL, для этого используется следующая конструкция:

attribute PULLUP: string;

attribute PULLUP of <название_сигнала>: signal is "TRUE";

____Если в модуле VHDL-описания необходимо указать несколько сигналов, в цепях которых должен быть активизирован встроенный подтягивающий резистор, достаточно одного выражения декларации атрибута PULLUP. Например, приведённый ниже фрагмент VHDL-кода с точки зрения выполняемых функций эквивалентен рассмотренным выше выражениям ограничений для контактов микросхемы, подключаемых к цепям data_net и clock_net.

attribute PULLUP: string;

attribute PULLUP of data_net: signal is "TRUE";

attribute PULLUP of clock_net: signal is "TRUE";

Активизация цепи удержания последнего состояния Bus Hold.

____Помимо встроенного подтягивающего резистора в блоках ввода/вывода, можно использовать цепь удержания последнего состояния Bus Hold. Работа этой цепи основана на подключении к пользовательскому контакту кристалла резистора, соединённого с шиной питания PullUP или общей шиной PullDown. Тип подключаемого резистора обуславливается последним определённым состоянием сигнала (высокого или низкого логического уровня) на соответствующем выводе ПЛИС.

____Для включения функции удержания последнего состояния сигнала на требуемом контакте микросхемы предусмотрен атрибут KEEPER. Этот атрибут указывается для цепи (сигнала), подключённой к соответствующему выводу ПЛИС. Формат строки, устанавливающей атрибут KEEPER в файле временных и топологических ограничений проекта UCF, имеет вид:

NET <название_цепи> KEEPER;

____Например, выражения

NET data_net KEEPER;

и

NET clock_net KEEPER;

предписывают подключить цепь удержания последнего состояния Bus Hold для пользовательских выводов ПЛИС, подключаемых к цепям data_net и clock_net соответственно.

____Чтобы непосредственно в файле VHDL-описания определить выводы микросхемы, для которых должна быть активизирована цепь удержания последнего состояния, нужно с помощью атрибута KEEPER указать названия соответствующих сигналов проектируемого устройства. Выражения, описывающие этот атрибут в составе VHDL-описания, выглядят следующим образом:

attribute KEEPER: string;

attribute KEEPER of <название_сигнала>: signal is "TRUE";

____Строка декларации атрибута KEEPER, как и в предыдущих случаях, должна присутствовать в описании в единичном экземпляре, независимо от числа сигналов, для которых устанавливается этот атрибут. Например:

attribute KEEPER: string;

attribute KEEPER of data_net: signal is "TRUE";

attribute KEEPER of clock_net: signal is "TRUE";

Программирование стандартов ввода/вывода

для пользовательских контактов.

для пользовательских контактов.

____Если в проекте, предполагается использование одного стандарта ввода/вывода, то вид требуемого стандарта можно указать сразу для всех пользовательских контактов микросхемы при выполнении этапа реализации. Эта операция выполняется в среде управляющей оболочки средств проектирование ISE - Навигатора проекта. Для выбора требуемого стандарта ввода/вывода следует воспользоваться выпадающим меню параметра Output Voltage Standard, который находится в окне Process Properties. Этот параметр позволяет установить стандарт ввода/вывода, используемый по умолчанию в процессе реализации проекта.

____Конфигурирование отдельных пользовательских выводов микросхемы в соответствии с требуемым стандартом ввода/вывода осуществляется с помощью атрибута IOSTANDARD. Этот атрибут присваивается входной или выходной цепи (сигналу), подключённой к соответствующему выводу ПЛИС. Каждому стандарту ввода/вывода соответствует индивидуальное значение атрибута IOSTANDARD. В таблице ниже приведён список значений этого атрибута для всех стандартов ввода/вывода, поддерживаемых микросхемами семейства CoolRunner-II. При установке значения атрибута IOSTANDARD следует убедиться, что выбранный стандарт поддерживается микросхемой, используемой для реализации проекта.

____Для установки требуемого значения атрибута IOSTANDARD в файле временных и топологических ограничений проекта UCF используется следующий формат строки:

NET <название_цепи> IOSTANDARD = <значение_атрибута_IOSTANDARD_для_соответствующего_стандарта_ввода/вывода>;

____Например, выражения

NET data_in IOSTANDARD = LVCMOS18;

и

NET clock IOSTANDARD = LVCMOS18;

определяют режим конфигурирования выводов микросхемы, связанных с цепями data_in и clock, в соответствии с спецификацией стандарта LVCMOS 1.8 V.

____Чтобы указать требуемые стандарты ввода/вывода для отдельных контактов ПЛИС в модуле исходного описания на языке VHDL, нужно воспользоваться конструкцией, представленной ниже.

attribute IOSTANDARD: string;

attribute IOSTANDARD of <название_сигнала>: signal is "<значение_атрибута_IOSTANDARD_для_соответствующего_стандарта_ввода/вывода>";

____В качестве примера далее приведён фрагмент VHDL-описания, в котором для выводов микросхемы, используемых для подключения сигналов data_in и clock, устанавливается соответствие требованиям стандарту LVCMOS 1.8 V.

attribute IOSTANDARD: string;

attribute IOSTANDARD of data_in: signal is "LVCMOS18";