Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Изучаем основы VHDL, ISE, ПЛИС Xilinx.

Страница 2 из 2 • Поделиться

Страница 2 из 2 •  1, 2

1, 2

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

26

резерв.

Последний раз редактировалось: Viktor2312 (Вт Май 10 2016, 20:49), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

27

резерв.

Последний раз редактировалось: Viktor2312 (Вт Май 10 2016, 20:50), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

28

резерв.

Последний раз редактировалось: Viktor2312 (Вт Май 10 2016, 20:57), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

Re: Изучаем основы VHDL, ISE, ПЛИС Xilinx.

29

резерв.

Последний раз редактировалось: Viktor2312 (Вт Май 10 2016, 20:59), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

31

.

________________________________________________________________________________________________________

____Статья открывает цикл публикаций, которые знакомят с процессом сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx, выполняемого с применением последней версии системы проектирования серии Xilinx ISE. В первой части цикла рассматриваются процедуры установки необходимого программного обеспечения, а также приводятся варианты принципиальной схемы загрузочного кабеля, рекомендуемые для самостоятельного изготовления.

________________________________________________________________________________________________________

Введение.

____Предлагаемый курс рассчитан, в первую очередь, на разработчиков, знакомых с основами цифровой техники, но не имеющих опыта проектирования устройств на основе ПЛИС фирмы Xilinx [1]. Информация, приведённая в рамках этого курса, может также использоваться опытными специалистами для быстрого самостоятельного освоения последней версии системы автоматизированного проектирования серии Xilinx ISE (Integrated Synthesis Environment/Integrated Software Environment).

[1] Кузелин М. О., Кнышев Д. А., Зотов В. Ю. Современные семейства ПЛИС фирмы Xilinx. Справочное пособие. М.: Горячая линия – Телеком, 2004.

____Настоящий курс охватывает выполнение всех этапов процесса разработки цифрового устройства: от создания нового проекта до его аппаратной реализации – программирования (конфигурирования) кристалла ПЛИС. Каждая из частей курса нацелена на изучение соответствующего этапа (или нескольких этапов) этого процесса. Часть 1 является вводной и посвящена подготовке необходимых для изучения курса средств.

Организация рабочего места.

____Для результативного освоения материала курса и последующей практической работы потребуются следующие инструменты:

____Для эффективной работы со средствами проектирования и моделирования рекомендуется использовать компьютер с процессором не ниже Pentium-IV 2,8 ГГц и ОЗУ объёмом не менее 512 Мб. Размер свободного пространства на жёстком диске, необходимого для установки последних версий САПР серии Xilinx ISE [2] и системы моделирования ModelSim XE Starter в полном объёме, должен составлять не менее 3,5 Гб. Процедуры установки систем проектирования и моделирования подробно рассматриваются в следующих разделах.

[2] Зотов В. Средства проектирования встраиваемых микропроцессорных систем, реализуемых на основе ПЛИС фирмы Xilinx. Современная электроника. 2006. №№ 7 – 9.

____Все кристаллы и элементы конфигурационной памяти современных семейств, выпускаемых фирмой Xilinx, программируемы в системе (In-System Programmable). Это означает, что конфигурационные данные могут загружаться непосредственно в ПЛИС или ППЗУ, установленные на печатной плате разрабатываемого устройства или системы. Поэтому для выполнения операций программирования (конфигурирования) не требуется аппаратный программатор. Загрузка конфигурационной информации в кристалл и обратное считывание данных осуществляется с помощью специального интерфейсного модуля, который преобразует сигналы стандартного порта персонального компьютера (параллельного LPT или USB) в сигналы конфигурационного порта ПЛИС. Такой модуль выполнен, как правило, в виде загрузочного кабеля (Download Cable). В процессе изучения курса проектирования цифровых устройств на основе ПЛИС и для последующей практической работы можно использовать любой из серийно выпускаемых фирмой Xilinx загрузочных кабелей [2]. Кроме того, в последнем разделе настоящей статьи приведены принципиальные схемы, которые могут быть использованы для самостоятельного изготовления загрузочного кабеля. Следует обратить внимание на то, что стоимость компонентов этих схем на порядок ниже стоимости фирменного загрузочного кабеля.

____Для аппаратной отладки разрабатываемого проекта необходим инструментальный модуль, выполненный на основе соответствующей ПЛИС. Такой модуль можно также подготовить самостоятельно, изготовив печатную плату и выполнив на ней монтаж выбранной ПЛИС. Кроме того, можно воспользоваться серийно выпускаемыми аппаратными модулями, которые входят в состав «стартовых» инструментальных комплектов (Starter Kit) [3 – 6] и отличаются сравнительно невысокой стоимостью. Применение таких готовых модулей позволяет не только сократить время разработки, но и исключить возможность появления ошибок, возникающих при трассировке печатной платы и монтаже компонентов. Для овладения методикой разработки устройств на основе кристаллов с архитектурой CPLD (Complex Programmable Logic Device) рекомендуется использовать инструментальный комплект CoolRunner-II Design Kit [3, 4]. Изучение процесса сквозного проектирования систем на основе ПЛИС с архитектурой FPGA удобно проводить с использованием «стартовых» комплектов Spartan-3 Starter Kit и Spartan-3E Starter Kit [3, 5, 6].

[3]Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М.: Горячая линия – Телеком, 2006.

[4]Зотов В. Инструментальный комплект CoolRunner-II Design Kit для практического освоения методов программирования ПЛИС семейств CPLD фирмы Xilinx. Компоненты и технологии. 2003. № 2.

[5]Зотов В. Инструментальный комплект Spartan-3 Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx. Компоненты и технологии. 2005. № 7.

[6]Зотов В. Новый инструментальный комплект Spartan-3E Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx. Компоненты и технологии, 2006. № 10.

Установка САПР серии Xilinx ISE.

____Дистрибутив пакета средств проектирования серии Xilinx ISE может предоставляться в форме самораспаковывающегося архива (на Web-сервере фирмы Xilinx) или в развёрнутом виде (на DVD-носителе). После распаковки архива автоматически запускается «мастер»установки САПР серии Xilinx ISE на жёсткий диск компьютера. При использовании разархивированного дистрибутива процесс инсталляции инициируется путём активизации программы setup.exe, которая находится в папке win.

____Работа «мастера» начинается с поочерёдного вывода трёх диалоговых панелей с заголовком Accept Software License, в которых отображаются соответствующие части лицензионного соглашения по использованию устанавливаемого программного обеспечения. Необходимо принять условия каждой части лицензии. Для этого в каждой из этих диалоговых панелей нужно поместить курсор на поле индикатора «I accept the terms of this software license» и щёлкнуть левой кнопкой мыши. При этом в поле индикатора отобразится соответствующий маркер и станет активной кнопка Далее (Next), расположенная в нижней части диалоговой панели. Эта кнопка позволяет перейти к следующей диалоговой панели «мастера» с заголовком Select Destination Directory, в которой нужно указать имя диска и каталога, используемого для размещения программ пакета САПР, а также название раздела (программной группы), создаваемого в меню Пуск/Программы (Start/Programs).

____Полное имя каталога, включающее путь доступа к нему, указывается в поле редактирования Select a Destination Directory, расположенном в верхней части одноименной диалоговой панели. По умолчанию предлагается каталог с названием Xilinx, который автоматически создаётся на диске С. Изменить название диска или каталога можно с помощью клавиатуры после активизации этого поля редактирования или кнопки Browse, которая открывает стандартную панель выбора каталога. Название раздела, создаваемого в меню Пуск/Программы (Start/Programs) и используемого для вызова программ пакета, определяется в поле редактирования Select a Program Folder. Рекомендуется использовать название, предлагаемое по умолчанию: Xilinx ISE N.Mi (где N.M – номер устанавливаемой версии САПР серии Xilinx ISE). При необходимости его изменения следует использовать клавиатуру. После нажатия кнопки Далее (Next) в нижней части диалоговой панели Select Destination Directory открывается очередная диалоговая панель «мастера», озаглавленная Update Environment.

____Данная панель позволяет определить значения параметров, управляющих установкой переменных окружения и путей доступа к программам пакета САПР серии Xilinx ISE в системных файлах. Значение переменной окружения LMC_HOME должно быть установлено в том случае, если в разрабатываемых проектах планируется использование компонентов процессора PowerPC или высокоскоростных приёмопередатчиков Rocket I/O. Определение значений переменных PATH и XILINX необходимо для нормального функционирования модулей пакета САПР в пакетном режиме и в режиме командной строки. Значения этих параметров используются для определения путей доступа к программам пакета в системных файлах. Управление установкой значений всех переменных окружения осуществляется с помощью индикаторов состояния, которые расположены слева в каждой строке с идентификатором переменной. Значение «включено», отмеченное маркером на поле соответствующего индикатора, разрешает автоматическое определение выбранной переменной окружения. Для изменения состояния индикатора на противоположное следует поместить курсор на поле индикатора и щёлкнуть левой кнопкой мыши. Для всех параметров, управляющих определением значений переменных окружения, рекомендуется использовать состояние «включено», установленное по умолчанию. Чтобы перейти к следующему шагу инсталляции средств проектирования серии Xilinx ISE, нужно воспользоваться кнопкой Далее (Next), расположенной в нижней части диалоговой панели Update Environment.

____Очередная диалоговая панель Begin Installation, отображаемая после нажатия кнопки Далее (Next), содержит список всех указанных ранее параметров процесса установки пакета. В этой панели также перечисляются семейства ПЛИС, которые поддерживаются данной версией САПР. При необходимости изменения каких-либо значений параметров установки следует вернуться к предыдущим шагам, нажав кнопку Назад (Back). Если все параметры установлены корректно, то следует нажать кнопку Установка (Install), которая активизирует собственно процесс инсталляции программ пакета САПР. При этом на экран выводится информационная панель, в верхней части которой отображается индикатор выполнения этого процесса. Процесс установки средств проектирования может занимать заметное время, в зависимости от производительности компьютера и скорости работы жёсткого диска. В течение этого процесса в информационной панели, отображаемой на экране монитора, приводятся сведения о новых возможностях устанавливаемой версии САПР.

____После завершения инсталляции программ пакета САПР серии Xilinx ISE может выводиться запрос о замене драйверов. Для нормальной работы загрузочных кабелей рекомендуется ответить на этот запрос утвердительно (Yes).

____Далее, при отсутствии ошибок, отображается сообщение об успешном окончании процесса инсталляции, которое закрывается кнопкой ОК. После этого следует обязательно установить модули обновления, которые устраняют ошибки, обнаруженные в процессе эксплуатации САПР, а также расширяют список поддерживаемых семейств ПЛИС. Процесс установки модулей обновления Service Pack рассматривается в следующем разделе.

Обновление программных средств пакета САПР серии Xilinx ISE.

____Обновление программных средств пакета САПР серии Xilinx ISE выполняется с помощью модулей Service Pack, которые устанавливаются поверх существующей версии. К моменту написания данной статьи на web-сервере фирмы Xilinx был представлен Service Pack 3. Этот модуль представляет собой самораспаковывающийся архив, после развёртывания которого автоматически запускается «мастер» инсталляции Service Pack.

____В процессе установки модуля обновления Service Pack необходимо указать диск и каталог, в котором расположены программные средства пакета САПР серии Xilinx ISE, используя стартовую диалоговую панель «мастера» Select a Destination Directory. Ввод названия каталога осуществляется с помощью клавиатуры после активизации поля редактирования «Select the directory where you want the software installed» или кнопки Browse, которая открывает стандартную панель выбора каталога. В этой же диалоговой панели содержится параметр Create Backup before installing update, который управляет созданием резервных копий изменяемых файлов. По умолчанию для этого параметра используется значение «включено», позволяющее впоследствии при необходимости отменить изменения, выполненные в процессе обновления пакета средств проектирования.

____Перед началом копирования файлов выводится панель Begin Installation, в которой приведены выбранные значения параметров инсталляции. При необходимости внесения изменений следует вернуться к предыдущим шагам, нажав кнопку Назад (Back). Если все значения параметров установлены верно, то следует нажать кнопку Установка (Install), которая активизирует собственно процесс инсталляции файлов модуля обновления Service Pack.

____Дальнейший ход процесса установки модуля обновления выполняется в автоматическом режиме и сопровождается отображением в диалоговой панели информационных сообщений о последних изменениях в САПР. Завершается этот процесс выводом информационной панели, уведомляющей об успешном окончании установки файлов модуля обновления.

Установка системы HDL-моделирования ModelSim XE III Starter.

____Процесс установки системы HDL-моделирования ModelSim XE III Starter выполняется также с помощью «мастера», который активизируется сразу после автоматической распаковки инсталляционного архива. В начале инсталляции на экран выводится стартовая диалоговая панель с заголовком Select Components, с помощью которой следует выбрать редакцию устанавливаемой системы ModelSim. Дистрибутив пакета позволяет установить как полную, так и ограниченную свободно распространяемую версию системы моделирования. Но для каждой редакции необходима соответствующая лицензия (файл с лицензионным кодом). Фирмой Xilinx бесплатно предоставляется лицензия на использование только свободно распространяемой редакции ModelSim XE III Starter. Для инсталляции этой версии нужно в диалоговой панели Select Components зафиксировать в нажатом состоянии кнопку MXE III Starter – Limited Version MXE III (Free).

____Переход к следующему шагу установки программных средств ModelSim осуществляется нажатием кнопки Далее (Next) в нижней части диалоговой панели. Очередная диалоговая панель «мастера» установки Welcome содержит предупреждение о необходимости закрытия всех других открытых приложений (программ) перед началом процесса инсталляции. Для прекращения установки системы моделирования и последующего завершения работы активных приложений, которые могут повлиять на процесс инсталляции, следует воспользоваться кнопкой Отмена (Cancel), находящейся в нижней части диалоговой панели Welcome.

____Нажатие кнопки Далее (Next) приводит к открытию следующей диалоговой панели «мастера» Software License Agreement. В этой панели отображается текст лицензионного соглашения об использовании устанавливаемой версии системы ModelSim. Чтобы продолжить процесс установки, необходимо принять условия лицензии, нажав кнопку Yes, расположенную в нижней части диалоговой панели Software License Agreement.

____Далее необходимо указать диск и каталог, в который будут установлены программные модули и библиотеки системы моделирования, используя очередную диалоговую панель Choose Destination Location. Полное название каталога отображается в поле Destination Folder. По умолчанию программа установки предлагает разместить средства моделирования ModelSim в каталоге Modeltech_xe_starter, который автоматически создаётся на диске С. Для изменения предлагаемого названия диска и каталога следует воспользоваться стандартной панелью навигации по дискам компьютера, которая открывается после нажатия кнопки Browse, расположенной в поле Destination Folder. Указав место расположения системы моделирования, можно перейти к следующему шагу процесса её инсталляции, воспользовавшись кнопкой Далее (Next), находящейся в нижней части диалоговой панели Choose Destination Location.

____На этом шаге производится выбор устанавливаемых исходных файлов и библиотек. Очередная диалоговая панель «мастера» Select Library Installation Option содержит список возможных вариантов конфигурации библиотек для языков VHDL и Verilog. При разработке проектов с использованием языка описания аппаратуры VHDL следует в этом списке выбрать строку Full VHDL.

____Следующая диалоговая панель Select Program Folder предназначена для определения названия раздела, создаваемого в меню Пуск/Программы (Start/Programs), предоставляющего доступ к программам системы моделирования ModelSim. Имя программной группы указывается в поле редактирования Program Folders. По умолчанию в качестве названия раздела используется строка ModelSim XE III 6.1e. Если данный раздел не используется для других целей, рекомендуется оставить название программной группы, предлагаемое по умолчанию. Выбор названия раздела завершается нажатием кнопки Далее (Next), находящейся в нижней части диалоговой панели Select Program Folder.

____В очередной диалоговой панели «мастера» инсталляции Add ModelSim To Path представлен запрос об установке путей доступа к программам пакета ModelSim в системных файлах компьютера. Указание полного пути доступа к каталогу, содержащему исполняемые программные модули системы моделирования, необходимо для выполнения компиляции в пакетном режиме и осуществления моделирования в окне сеанса DOS. Процедура установки путей доступа выполняется автоматически при нажатии кнопки Yes в панели запроса Add ModelSim To Path.

____Функционирование системы моделирования ModelSim XE III невозможно без файла, содержащего лицензионный код. Процедура его получения может быть выполнена сразу же после завершения установки пакета, если используемый компьютер имеет выход в Интернет. С этой целью на экран выводится диалоговая панель License Request, содержащая запрос о немедленном выполнении процедуры получения файла лицензии. При утвердительном ответе на этот запрос автоматически стартует утилита Submit License Request. Вопросы получения лицензионного кода подробно обсуждаются в следующем разделе.

____Заключительная информационная панель «мастера» ModelSim XE III Setup Complete содержит сведения об успешном выполнении основных операций установки системы моделирования ModelSim XE III Starter. Процесс инсталляции средств моделирования завершается нажатием кнопки Готово (Finish) в нижней части этой информационной панели.

____Для системы моделирования ModelSim XE также периодически выпускаются пакеты обновлений библиотек моделей компонентов и IP-ядер фирмы Xilinx. Получить данные пакеты можно теми же путями, что и САПР серии Xilinx ISE [2]: через Интернет или официального дистрибьютора. Пакеты обновлений для системы ModelSim XE обычно выполнены в виде zip-архивов, содержимое которых нужно скопировать непосредственно в основной каталог, созданный для установки средств моделирования.

Получение лицензионного кода для системы моделирования ModelSim XE III Starter.

____Для получения файла лицензии следует активизировать строку Submit License Request в меню Программы/ModelSim, которое открывается при нажатии кнопки Пуск операционной системы Windows. Эта утилита автоматически собирает всю информацию о технических параметрах используемого компьютера, необходимую для получения лицензионного кода, преобразует её в формат адресной строки Internet и автоматически запускает обозреватель Microsoft Internet Explorer. Если компьютер, на котором установлен пакет, подключен к Интернету, то файл лицензии может быть получен в течение нескольких минут. В процессе получения лицензии необходимо ввести идентификатор пользователя и пароль, полученные ранее при регистрации, и вновь заполнить анкету с указанием адреса электронной почты, по которому будет выслан файл, содержащий лицензионный код.

____В противном случае, при отсутствии выхода в Интернет, следует скопировать содержимое адресной строки Microsoft Internet Explorer в буфер обмена, выделив его и воспользовавшись командой копирования из меню Edit или всплывающего контекстно-зависимого меню. Затем содержимое буфера обмена нужно сохранить в виде текстового файла на дискете или Flash-диске (используя любой текстовый редактор, например, Notepad или WordPad), которые следует перенести на компьютер, подключенный к Интернету. Далее нужно выполнить обратную операцию – скопировать текст из файла на дискете или Flash-диске в буфер обмена, после чего активизировать обозреватель Internet Explorer и вставить содержимое буфера в адресную строку. Полученный файл лицензии необходимо перенести на жёсткий диск компьютера, где установлен пакет ModelSim XE III Starter.

____Перед началом работы с пакетом моделирования необходимо активизировать полученный лицензионный код. Для этого следует запустить программу Licensing Wizard, используя меню Программы/ModelSim, с помощью которой указывается размещение файла лицензии на диске и автоматически устанавливается полный путь доступа к нему, а также необходимые переменные окружения.

Принципиальные схемы загрузочных кабелей, предназначенных для конфигурирования ПЛИС фирмы Xilinx.

____Принципиальные схемы загрузочных кабелей, которые рассматриваются в настоящем разделе, отличаются простотой и доступностью используемых компонентов. Эти схемы представлены в разделе поддержки сайта xilinx.com и в описании инструментальных комплектов, перечисленных в начале статьи. Все загрузочные кабели, выполненные на основе данных схем, предназначены для подключения к параллельному порту (LPT) персонального компьютера.

____На рис. 1 изображена принципиальная схема параллельного загрузочного кабеля Parallel Download Cable III, который серийно производился фирмой Xilinx до выпуска его новой версии – Parallel Download Cable IV. С помощью данного кабеля можно выполнять загрузку конфигурационной последовательности в ПЛИС с архитектурой FPGA (Field Programmable Gate Array), а также программирование кристаллов с архитектурой CPLD и конфигурационной памяти. Поэтому его целесообразно использовать в том случае, когда планируется работа с различными семействами ПЛИС. Загрузка конфигурационных данных в кристалл и обратное считывание информации осуществляется через параллельный порт персонального компьютера, который функционирует в режиме EPP (Enhanced Parallel Port). Питание загрузочного кабеля (рис. 1) осуществляется от стабилизатора напряжения, расположенного на печатной плате проектируемого устройства, в состав которого входит конфигурируемая ПЛИС.

____Схема загрузочного кабеля Xilinx Parallel Download Cable III выполнена на основе двух микросхем SN74HC125N. Все компоненты схемы располагаются на печатной плате. Сопряжение печатной платы модуля загрузочного кабеля с параллельным портом персонального компьютера осуществляется обычно посредством 25-проводного ленточного кабеля, рекомендуемая длина которого не должна превышать 1 м. Для подключения модуля программирования к порту JTAG-интерфейса конфигурируемой ПЛИС можно использовать 10-проводный ленточный кабель, рекомендуемая длина которого не должна превосходить 150 мм. В случае применения ленточных кабелей большей длины велика вероятность возникновения помех в процессе программирования ПЛИС, а также изменения длительности фронтов конфигурационных сигналов. Следствием проявления этих факторов являются сбои в процессе конфигурирования кристалла, которые в конечном итоге приводят к отсутствию работоспособности запрограммированной ПЛИС.

____Для программирования ПЛИС с архитектурой CPLD, в частности, кристаллов семейства CoolRunner-II, можно изготовить загрузочный кабель по упрощённому варианту принципиальной схемы, приведённой на рис. 1. Основу модифицированного варианта схемы образует одна микросхема SN74HC125N. Загрузочный кабель, выполненный по такой схеме, применяется, например, в составе отладочной платы Digilab XC2 из комплекта CoolRunner-II Design Kit, который выпускается фирмой Digilent Incorporated [3, 4 ]. Принципиальная схема упрощённого варианта загрузочного кабеля показана на рис. 2. Сокращение количества компонентов принципиальной схемы позволяет существенно уменьшить размеры печатной платы модуля загрузочного кабеля. Кроме того, разъём, предназначенный для подключения к порту JTAG-интерфейса программируемой ПЛИС, можно также расположить непосредственно на этой печатной плате, исключив тем самым соответствующий ленточный кабель. В этом случае для обеспечения механической совместимости загрузочного кабеля с платой разрабатываемого устройства рекомендуется выбирать ширину печатной платы модуля равной длине разъёма JTAG-интерфейса. Таким образом, исключаются возможные проблемы при подключении разъёма JTAG-интерфейса загрузочного кабеля к соответствующему разъёму на печатной плате разрабатываемой системы, в состав которой входит программируемый кристалл. Электропитание данного загрузочного кабеля при работе с ПЛИС семейства CoolRunner-II осуществляется от источника с выходным напряжением 3,3 В. Для этой цели может использоваться дополнительный внешний источник с указанным значением выходного напряжения или стабилизатор, расположенный на печатной плате (на которой установлена программируемая ПЛИС) и вырабатывающий напряжение 3,3 В.

____Наиболее эффективным вариантом принципиальной схемы загрузочного кабеля, рекомендуемым для самостоятельного изготовления, является схема кабеля JTAG-интерфейса, который выпускается фирмой Digilent Incorporated. Этот загрузочный кабель Digilent JTAG3 Download/Debug Cable входит, в частности, в состав инструментального комплекта Spartan-3 Starter Kit [4, 5]. Важным преимуществом указанного загрузочного кабеля является поддержка достаточно широкого диапазона значений напряжения питания: 2,8...5 В. Основу принципиальной схемы этого кабеля (рис. 3) образуют две микросхемы: NL37WZ17 и NL17SZ125, выпускаемые фирмой ON Semiconductor.

Использование в составе схемы компонентов, выполненных в миниатюрных корпусах, позволяет разместить их на печатной плате вместе с разъёмом JTAG-интерфейса. Для подключения данного загрузочного кабеля к параллельному порту персонального компьютера можно использовать пятипроводный кабель длиной не более 1,5 м. Соединение контактов 8, 11, 12 разъёма параллельного порта осуществляется перемычками, размещаемыми непосредственно на разъёме загрузочного кабеля DB25P.

Продолжение в следующем посте...

.

Практический курс сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx.

(часть 1)

Валерий Зотов

Валерий Зотов

________________________________________________________________________________________________________

____Статья открывает цикл публикаций, которые знакомят с процессом сквозного проектирования цифровых устройств на основе ПЛИС фирмы Xilinx, выполняемого с применением последней версии системы проектирования серии Xilinx ISE. В первой части цикла рассматриваются процедуры установки необходимого программного обеспечения, а также приводятся варианты принципиальной схемы загрузочного кабеля, рекомендуемые для самостоятельного изготовления.

________________________________________________________________________________________________________

Введение.

____Предлагаемый курс рассчитан, в первую очередь, на разработчиков, знакомых с основами цифровой техники, но не имеющих опыта проектирования устройств на основе ПЛИС фирмы Xilinx [1]. Информация, приведённая в рамках этого курса, может также использоваться опытными специалистами для быстрого самостоятельного освоения последней версии системы автоматизированного проектирования серии Xilinx ISE (Integrated Synthesis Environment/Integrated Software Environment).

[1] Кузелин М. О., Кнышев Д. А., Зотов В. Ю. Современные семейства ПЛИС фирмы Xilinx. Справочное пособие. М.: Горячая линия – Телеком, 2004.

____Настоящий курс охватывает выполнение всех этапов процесса разработки цифрового устройства: от создания нового проекта до его аппаратной реализации – программирования (конфигурирования) кристалла ПЛИС. Каждая из частей курса нацелена на изучение соответствующего этапа (или нескольких этапов) этого процесса. Часть 1 является вводной и посвящена подготовке необходимых для изучения курса средств.

Организация рабочего места.

____Для результативного освоения материала курса и последующей практической работы потребуются следующие инструменты:

- персональный компьютер с установленной системой автоматизированного проектирования серии Xilinx ISE и системой HDL-моделирования ModelSim XE,

- загрузочный кабель,

- отладочная плата.

____Для эффективной работы со средствами проектирования и моделирования рекомендуется использовать компьютер с процессором не ниже Pentium-IV 2,8 ГГц и ОЗУ объёмом не менее 512 Мб. Размер свободного пространства на жёстком диске, необходимого для установки последних версий САПР серии Xilinx ISE [2] и системы моделирования ModelSim XE Starter в полном объёме, должен составлять не менее 3,5 Гб. Процедуры установки систем проектирования и моделирования подробно рассматриваются в следующих разделах.

[2] Зотов В. Средства проектирования встраиваемых микропроцессорных систем, реализуемых на основе ПЛИС фирмы Xilinx. Современная электроника. 2006. №№ 7 – 9.

____Все кристаллы и элементы конфигурационной памяти современных семейств, выпускаемых фирмой Xilinx, программируемы в системе (In-System Programmable). Это означает, что конфигурационные данные могут загружаться непосредственно в ПЛИС или ППЗУ, установленные на печатной плате разрабатываемого устройства или системы. Поэтому для выполнения операций программирования (конфигурирования) не требуется аппаратный программатор. Загрузка конфигурационной информации в кристалл и обратное считывание данных осуществляется с помощью специального интерфейсного модуля, который преобразует сигналы стандартного порта персонального компьютера (параллельного LPT или USB) в сигналы конфигурационного порта ПЛИС. Такой модуль выполнен, как правило, в виде загрузочного кабеля (Download Cable). В процессе изучения курса проектирования цифровых устройств на основе ПЛИС и для последующей практической работы можно использовать любой из серийно выпускаемых фирмой Xilinx загрузочных кабелей [2]. Кроме того, в последнем разделе настоящей статьи приведены принципиальные схемы, которые могут быть использованы для самостоятельного изготовления загрузочного кабеля. Следует обратить внимание на то, что стоимость компонентов этих схем на порядок ниже стоимости фирменного загрузочного кабеля.

____Для аппаратной отладки разрабатываемого проекта необходим инструментальный модуль, выполненный на основе соответствующей ПЛИС. Такой модуль можно также подготовить самостоятельно, изготовив печатную плату и выполнив на ней монтаж выбранной ПЛИС. Кроме того, можно воспользоваться серийно выпускаемыми аппаратными модулями, которые входят в состав «стартовых» инструментальных комплектов (Starter Kit) [3 – 6] и отличаются сравнительно невысокой стоимостью. Применение таких готовых модулей позволяет не только сократить время разработки, но и исключить возможность появления ошибок, возникающих при трассировке печатной платы и монтаже компонентов. Для овладения методикой разработки устройств на основе кристаллов с архитектурой CPLD (Complex Programmable Logic Device) рекомендуется использовать инструментальный комплект CoolRunner-II Design Kit [3, 4]. Изучение процесса сквозного проектирования систем на основе ПЛИС с архитектурой FPGA удобно проводить с использованием «стартовых» комплектов Spartan-3 Starter Kit и Spartan-3E Starter Kit [3, 5, 6].

[3]Зотов В. Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx. М.: Горячая линия – Телеком, 2006.

[4]Зотов В. Инструментальный комплект CoolRunner-II Design Kit для практического освоения методов программирования ПЛИС семейств CPLD фирмы Xilinx. Компоненты и технологии. 2003. № 2.

[5]Зотов В. Инструментальный комплект Spartan-3 Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx. Компоненты и технологии. 2005. № 7.

[6]Зотов В. Новый инструментальный комплект Spartan-3E Starter Kit для практического освоения методов проектирования встраиваемых микропроцессорных систем на основе ПЛИС семейств FPGA фирмы Xilinx. Компоненты и технологии, 2006. № 10.

Установка САПР серии Xilinx ISE.

____Дистрибутив пакета средств проектирования серии Xilinx ISE может предоставляться в форме самораспаковывающегося архива (на Web-сервере фирмы Xilinx) или в развёрнутом виде (на DVD-носителе). После распаковки архива автоматически запускается «мастер»установки САПР серии Xilinx ISE на жёсткий диск компьютера. При использовании разархивированного дистрибутива процесс инсталляции инициируется путём активизации программы setup.exe, которая находится в папке win.

____Работа «мастера» начинается с поочерёдного вывода трёх диалоговых панелей с заголовком Accept Software License, в которых отображаются соответствующие части лицензионного соглашения по использованию устанавливаемого программного обеспечения. Необходимо принять условия каждой части лицензии. Для этого в каждой из этих диалоговых панелей нужно поместить курсор на поле индикатора «I accept the terms of this software license» и щёлкнуть левой кнопкой мыши. При этом в поле индикатора отобразится соответствующий маркер и станет активной кнопка Далее (Next), расположенная в нижней части диалоговой панели. Эта кнопка позволяет перейти к следующей диалоговой панели «мастера» с заголовком Select Destination Directory, в которой нужно указать имя диска и каталога, используемого для размещения программ пакета САПР, а также название раздела (программной группы), создаваемого в меню Пуск/Программы (Start/Programs).

____Полное имя каталога, включающее путь доступа к нему, указывается в поле редактирования Select a Destination Directory, расположенном в верхней части одноименной диалоговой панели. По умолчанию предлагается каталог с названием Xilinx, который автоматически создаётся на диске С. Изменить название диска или каталога можно с помощью клавиатуры после активизации этого поля редактирования или кнопки Browse, которая открывает стандартную панель выбора каталога. Название раздела, создаваемого в меню Пуск/Программы (Start/Programs) и используемого для вызова программ пакета, определяется в поле редактирования Select a Program Folder. Рекомендуется использовать название, предлагаемое по умолчанию: Xilinx ISE N.Mi (где N.M – номер устанавливаемой версии САПР серии Xilinx ISE). При необходимости его изменения следует использовать клавиатуру. После нажатия кнопки Далее (Next) в нижней части диалоговой панели Select Destination Directory открывается очередная диалоговая панель «мастера», озаглавленная Update Environment.

____Данная панель позволяет определить значения параметров, управляющих установкой переменных окружения и путей доступа к программам пакета САПР серии Xilinx ISE в системных файлах. Значение переменной окружения LMC_HOME должно быть установлено в том случае, если в разрабатываемых проектах планируется использование компонентов процессора PowerPC или высокоскоростных приёмопередатчиков Rocket I/O. Определение значений переменных PATH и XILINX необходимо для нормального функционирования модулей пакета САПР в пакетном режиме и в режиме командной строки. Значения этих параметров используются для определения путей доступа к программам пакета в системных файлах. Управление установкой значений всех переменных окружения осуществляется с помощью индикаторов состояния, которые расположены слева в каждой строке с идентификатором переменной. Значение «включено», отмеченное маркером на поле соответствующего индикатора, разрешает автоматическое определение выбранной переменной окружения. Для изменения состояния индикатора на противоположное следует поместить курсор на поле индикатора и щёлкнуть левой кнопкой мыши. Для всех параметров, управляющих определением значений переменных окружения, рекомендуется использовать состояние «включено», установленное по умолчанию. Чтобы перейти к следующему шагу инсталляции средств проектирования серии Xilinx ISE, нужно воспользоваться кнопкой Далее (Next), расположенной в нижней части диалоговой панели Update Environment.

____Очередная диалоговая панель Begin Installation, отображаемая после нажатия кнопки Далее (Next), содержит список всех указанных ранее параметров процесса установки пакета. В этой панели также перечисляются семейства ПЛИС, которые поддерживаются данной версией САПР. При необходимости изменения каких-либо значений параметров установки следует вернуться к предыдущим шагам, нажав кнопку Назад (Back). Если все параметры установлены корректно, то следует нажать кнопку Установка (Install), которая активизирует собственно процесс инсталляции программ пакета САПР. При этом на экран выводится информационная панель, в верхней части которой отображается индикатор выполнения этого процесса. Процесс установки средств проектирования может занимать заметное время, в зависимости от производительности компьютера и скорости работы жёсткого диска. В течение этого процесса в информационной панели, отображаемой на экране монитора, приводятся сведения о новых возможностях устанавливаемой версии САПР.

____После завершения инсталляции программ пакета САПР серии Xilinx ISE может выводиться запрос о замене драйверов. Для нормальной работы загрузочных кабелей рекомендуется ответить на этот запрос утвердительно (Yes).

____Далее, при отсутствии ошибок, отображается сообщение об успешном окончании процесса инсталляции, которое закрывается кнопкой ОК. После этого следует обязательно установить модули обновления, которые устраняют ошибки, обнаруженные в процессе эксплуатации САПР, а также расширяют список поддерживаемых семейств ПЛИС. Процесс установки модулей обновления Service Pack рассматривается в следующем разделе.

Обновление программных средств пакета САПР серии Xilinx ISE.

____Обновление программных средств пакета САПР серии Xilinx ISE выполняется с помощью модулей Service Pack, которые устанавливаются поверх существующей версии. К моменту написания данной статьи на web-сервере фирмы Xilinx был представлен Service Pack 3. Этот модуль представляет собой самораспаковывающийся архив, после развёртывания которого автоматически запускается «мастер» инсталляции Service Pack.

____В процессе установки модуля обновления Service Pack необходимо указать диск и каталог, в котором расположены программные средства пакета САПР серии Xilinx ISE, используя стартовую диалоговую панель «мастера» Select a Destination Directory. Ввод названия каталога осуществляется с помощью клавиатуры после активизации поля редактирования «Select the directory where you want the software installed» или кнопки Browse, которая открывает стандартную панель выбора каталога. В этой же диалоговой панели содержится параметр Create Backup before installing update, который управляет созданием резервных копий изменяемых файлов. По умолчанию для этого параметра используется значение «включено», позволяющее впоследствии при необходимости отменить изменения, выполненные в процессе обновления пакета средств проектирования.

____Перед началом копирования файлов выводится панель Begin Installation, в которой приведены выбранные значения параметров инсталляции. При необходимости внесения изменений следует вернуться к предыдущим шагам, нажав кнопку Назад (Back). Если все значения параметров установлены верно, то следует нажать кнопку Установка (Install), которая активизирует собственно процесс инсталляции файлов модуля обновления Service Pack.

____Дальнейший ход процесса установки модуля обновления выполняется в автоматическом режиме и сопровождается отображением в диалоговой панели информационных сообщений о последних изменениях в САПР. Завершается этот процесс выводом информационной панели, уведомляющей об успешном окончании установки файлов модуля обновления.

Установка системы HDL-моделирования ModelSim XE III Starter.

____Процесс установки системы HDL-моделирования ModelSim XE III Starter выполняется также с помощью «мастера», который активизируется сразу после автоматической распаковки инсталляционного архива. В начале инсталляции на экран выводится стартовая диалоговая панель с заголовком Select Components, с помощью которой следует выбрать редакцию устанавливаемой системы ModelSim. Дистрибутив пакета позволяет установить как полную, так и ограниченную свободно распространяемую версию системы моделирования. Но для каждой редакции необходима соответствующая лицензия (файл с лицензионным кодом). Фирмой Xilinx бесплатно предоставляется лицензия на использование только свободно распространяемой редакции ModelSim XE III Starter. Для инсталляции этой версии нужно в диалоговой панели Select Components зафиксировать в нажатом состоянии кнопку MXE III Starter – Limited Version MXE III (Free).

____Переход к следующему шагу установки программных средств ModelSim осуществляется нажатием кнопки Далее (Next) в нижней части диалоговой панели. Очередная диалоговая панель «мастера» установки Welcome содержит предупреждение о необходимости закрытия всех других открытых приложений (программ) перед началом процесса инсталляции. Для прекращения установки системы моделирования и последующего завершения работы активных приложений, которые могут повлиять на процесс инсталляции, следует воспользоваться кнопкой Отмена (Cancel), находящейся в нижней части диалоговой панели Welcome.

____Нажатие кнопки Далее (Next) приводит к открытию следующей диалоговой панели «мастера» Software License Agreement. В этой панели отображается текст лицензионного соглашения об использовании устанавливаемой версии системы ModelSim. Чтобы продолжить процесс установки, необходимо принять условия лицензии, нажав кнопку Yes, расположенную в нижней части диалоговой панели Software License Agreement.

____Далее необходимо указать диск и каталог, в который будут установлены программные модули и библиотеки системы моделирования, используя очередную диалоговую панель Choose Destination Location. Полное название каталога отображается в поле Destination Folder. По умолчанию программа установки предлагает разместить средства моделирования ModelSim в каталоге Modeltech_xe_starter, который автоматически создаётся на диске С. Для изменения предлагаемого названия диска и каталога следует воспользоваться стандартной панелью навигации по дискам компьютера, которая открывается после нажатия кнопки Browse, расположенной в поле Destination Folder. Указав место расположения системы моделирования, можно перейти к следующему шагу процесса её инсталляции, воспользовавшись кнопкой Далее (Next), находящейся в нижней части диалоговой панели Choose Destination Location.

____На этом шаге производится выбор устанавливаемых исходных файлов и библиотек. Очередная диалоговая панель «мастера» Select Library Installation Option содержит список возможных вариантов конфигурации библиотек для языков VHDL и Verilog. При разработке проектов с использованием языка описания аппаратуры VHDL следует в этом списке выбрать строку Full VHDL.

____Следующая диалоговая панель Select Program Folder предназначена для определения названия раздела, создаваемого в меню Пуск/Программы (Start/Programs), предоставляющего доступ к программам системы моделирования ModelSim. Имя программной группы указывается в поле редактирования Program Folders. По умолчанию в качестве названия раздела используется строка ModelSim XE III 6.1e. Если данный раздел не используется для других целей, рекомендуется оставить название программной группы, предлагаемое по умолчанию. Выбор названия раздела завершается нажатием кнопки Далее (Next), находящейся в нижней части диалоговой панели Select Program Folder.

____В очередной диалоговой панели «мастера» инсталляции Add ModelSim To Path представлен запрос об установке путей доступа к программам пакета ModelSim в системных файлах компьютера. Указание полного пути доступа к каталогу, содержащему исполняемые программные модули системы моделирования, необходимо для выполнения компиляции в пакетном режиме и осуществления моделирования в окне сеанса DOS. Процедура установки путей доступа выполняется автоматически при нажатии кнопки Yes в панели запроса Add ModelSim To Path.

____Функционирование системы моделирования ModelSim XE III невозможно без файла, содержащего лицензионный код. Процедура его получения может быть выполнена сразу же после завершения установки пакета, если используемый компьютер имеет выход в Интернет. С этой целью на экран выводится диалоговая панель License Request, содержащая запрос о немедленном выполнении процедуры получения файла лицензии. При утвердительном ответе на этот запрос автоматически стартует утилита Submit License Request. Вопросы получения лицензионного кода подробно обсуждаются в следующем разделе.

____Заключительная информационная панель «мастера» ModelSim XE III Setup Complete содержит сведения об успешном выполнении основных операций установки системы моделирования ModelSim XE III Starter. Процесс инсталляции средств моделирования завершается нажатием кнопки Готово (Finish) в нижней части этой информационной панели.

____Для системы моделирования ModelSim XE также периодически выпускаются пакеты обновлений библиотек моделей компонентов и IP-ядер фирмы Xilinx. Получить данные пакеты можно теми же путями, что и САПР серии Xilinx ISE [2]: через Интернет или официального дистрибьютора. Пакеты обновлений для системы ModelSim XE обычно выполнены в виде zip-архивов, содержимое которых нужно скопировать непосредственно в основной каталог, созданный для установки средств моделирования.

Получение лицензионного кода для системы моделирования ModelSim XE III Starter.

____Для получения файла лицензии следует активизировать строку Submit License Request в меню Программы/ModelSim, которое открывается при нажатии кнопки Пуск операционной системы Windows. Эта утилита автоматически собирает всю информацию о технических параметрах используемого компьютера, необходимую для получения лицензионного кода, преобразует её в формат адресной строки Internet и автоматически запускает обозреватель Microsoft Internet Explorer. Если компьютер, на котором установлен пакет, подключен к Интернету, то файл лицензии может быть получен в течение нескольких минут. В процессе получения лицензии необходимо ввести идентификатор пользователя и пароль, полученные ранее при регистрации, и вновь заполнить анкету с указанием адреса электронной почты, по которому будет выслан файл, содержащий лицензионный код.

____В противном случае, при отсутствии выхода в Интернет, следует скопировать содержимое адресной строки Microsoft Internet Explorer в буфер обмена, выделив его и воспользовавшись командой копирования из меню Edit или всплывающего контекстно-зависимого меню. Затем содержимое буфера обмена нужно сохранить в виде текстового файла на дискете или Flash-диске (используя любой текстовый редактор, например, Notepad или WordPad), которые следует перенести на компьютер, подключенный к Интернету. Далее нужно выполнить обратную операцию – скопировать текст из файла на дискете или Flash-диске в буфер обмена, после чего активизировать обозреватель Internet Explorer и вставить содержимое буфера в адресную строку. Полученный файл лицензии необходимо перенести на жёсткий диск компьютера, где установлен пакет ModelSim XE III Starter.

____Перед началом работы с пакетом моделирования необходимо активизировать полученный лицензионный код. Для этого следует запустить программу Licensing Wizard, используя меню Программы/ModelSim, с помощью которой указывается размещение файла лицензии на диске и автоматически устанавливается полный путь доступа к нему, а также необходимые переменные окружения.

Принципиальные схемы загрузочных кабелей, предназначенных для конфигурирования ПЛИС фирмы Xilinx.

____Принципиальные схемы загрузочных кабелей, которые рассматриваются в настоящем разделе, отличаются простотой и доступностью используемых компонентов. Эти схемы представлены в разделе поддержки сайта xilinx.com и в описании инструментальных комплектов, перечисленных в начале статьи. Все загрузочные кабели, выполненные на основе данных схем, предназначены для подключения к параллельному порту (LPT) персонального компьютера.

____На рис. 1 изображена принципиальная схема параллельного загрузочного кабеля Parallel Download Cable III, который серийно производился фирмой Xilinx до выпуска его новой версии – Parallel Download Cable IV. С помощью данного кабеля можно выполнять загрузку конфигурационной последовательности в ПЛИС с архитектурой FPGA (Field Programmable Gate Array), а также программирование кристаллов с архитектурой CPLD и конфигурационной памяти. Поэтому его целесообразно использовать в том случае, когда планируется работа с различными семействами ПЛИС. Загрузка конфигурационных данных в кристалл и обратное считывание информации осуществляется через параллельный порт персонального компьютера, который функционирует в режиме EPP (Enhanced Parallel Port). Питание загрузочного кабеля (рис. 1) осуществляется от стабилизатора напряжения, расположенного на печатной плате проектируемого устройства, в состав которого входит конфигурируемая ПЛИС.

____Схема загрузочного кабеля Xilinx Parallel Download Cable III выполнена на основе двух микросхем SN74HC125N. Все компоненты схемы располагаются на печатной плате. Сопряжение печатной платы модуля загрузочного кабеля с параллельным портом персонального компьютера осуществляется обычно посредством 25-проводного ленточного кабеля, рекомендуемая длина которого не должна превышать 1 м. Для подключения модуля программирования к порту JTAG-интерфейса конфигурируемой ПЛИС можно использовать 10-проводный ленточный кабель, рекомендуемая длина которого не должна превосходить 150 мм. В случае применения ленточных кабелей большей длины велика вероятность возникновения помех в процессе программирования ПЛИС, а также изменения длительности фронтов конфигурационных сигналов. Следствием проявления этих факторов являются сбои в процессе конфигурирования кристалла, которые в конечном итоге приводят к отсутствию работоспособности запрограммированной ПЛИС.

____Для программирования ПЛИС с архитектурой CPLD, в частности, кристаллов семейства CoolRunner-II, можно изготовить загрузочный кабель по упрощённому варианту принципиальной схемы, приведённой на рис. 1. Основу модифицированного варианта схемы образует одна микросхема SN74HC125N. Загрузочный кабель, выполненный по такой схеме, применяется, например, в составе отладочной платы Digilab XC2 из комплекта CoolRunner-II Design Kit, который выпускается фирмой Digilent Incorporated [3, 4 ]. Принципиальная схема упрощённого варианта загрузочного кабеля показана на рис. 2. Сокращение количества компонентов принципиальной схемы позволяет существенно уменьшить размеры печатной платы модуля загрузочного кабеля. Кроме того, разъём, предназначенный для подключения к порту JTAG-интерфейса программируемой ПЛИС, можно также расположить непосредственно на этой печатной плате, исключив тем самым соответствующий ленточный кабель. В этом случае для обеспечения механической совместимости загрузочного кабеля с платой разрабатываемого устройства рекомендуется выбирать ширину печатной платы модуля равной длине разъёма JTAG-интерфейса. Таким образом, исключаются возможные проблемы при подключении разъёма JTAG-интерфейса загрузочного кабеля к соответствующему разъёму на печатной плате разрабатываемой системы, в состав которой входит программируемый кристалл. Электропитание данного загрузочного кабеля при работе с ПЛИС семейства CoolRunner-II осуществляется от источника с выходным напряжением 3,3 В. Для этой цели может использоваться дополнительный внешний источник с указанным значением выходного напряжения или стабилизатор, расположенный на печатной плате (на которой установлена программируемая ПЛИС) и вырабатывающий напряжение 3,3 В.

____Наиболее эффективным вариантом принципиальной схемы загрузочного кабеля, рекомендуемым для самостоятельного изготовления, является схема кабеля JTAG-интерфейса, который выпускается фирмой Digilent Incorporated. Этот загрузочный кабель Digilent JTAG3 Download/Debug Cable входит, в частности, в состав инструментального комплекта Spartan-3 Starter Kit [4, 5]. Важным преимуществом указанного загрузочного кабеля является поддержка достаточно широкого диапазона значений напряжения питания: 2,8...5 В. Основу принципиальной схемы этого кабеля (рис. 3) образуют две микросхемы: NL37WZ17 и NL17SZ125, выпускаемые фирмой ON Semiconductor.

Использование в составе схемы компонентов, выполненных в миниатюрных корпусах, позволяет разместить их на печатной плате вместе с разъёмом JTAG-интерфейса. Для подключения данного загрузочного кабеля к параллельному порту персонального компьютера можно использовать пятипроводный кабель длиной не более 1,5 м. Соединение контактов 8, 11, 12 разъёма параллельного порта осуществляется перемычками, размещаемыми непосредственно на разъёме загрузочного кабеля DB25P.

Продолжение в следующем посте...

.

Последний раз редактировалось: Viktor2312 (Вс Сен 08 2019, 22:54), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

32

.

____________________________________________________________________________________________________

____Вторая часть курса знакомит с последовательностью этапов проектирования цифровых устройств на основе ПЛИС фирмы Xilinx. Приводятся краткие рекомендации по выбору кристаллов для реализации разрабатываемого устройства. Подробно рассматривается процесс создания нового проекта в САПР серии Xilinx ISE.

____________________________________________________________________________________________________

Краткая характеристика этапов проектирования цифровых устройств на основе ПЛИС, выпускаемых фирмой Xilinx.

____В процессе проектирования цифровых устройств на базе ПЛИС фирмы Xilinx можно выделить следующие этапы:

____Типовой маршрут проектирования цифровых устройств, выполняемых на основе ПЛИС фирмы Xilinx, показан на рисунке 4.

____Прежде чем приступить к созданию нового проекта, следует выбрать метод описания разрабатываемого устройства и, соответственно, средств синтеза. Исходная информация, описывающая проектируемое устройство, может быть представлена в виде принципиальных схем, описаний на языках HDL (Hardware Description Language), диаграмм состояний, пакетов и библиотек пользователя. Наиболее привычным и наглядным для разработчиков является схемотехнический метод описания. В то же время в последние годы большое распространение получили языки описания аппаратуры высокого уровня, в первую очередь, VHDL и Verilog. На практике используют смешанный метод: каждый функциональный блок разрабатываемого устройства описывается на одном из языков HDL, а их соединение представляется в виде соответствующей принципиальной схемы. Поэтому в дальнейшем будут рассмотрены процедуры подготовки исходных описаний проектируемых устройств в форме принципиальной схемы и с применением языка VHDL.

____Перед началом формирования нового проекта разрабатываемого устройства в САПР серии Xilinx ISE необходимо выбрать семейство и тип ПЛИС для его реализации. При этом необходимо учесть не только требования технического задания, но и предельные возможности различных серий ПЛИС, а также некоторые дополнительные факторы. Краткие рекомендации по выбору семейства и типа ПЛИС приводятся в следующем разделе. Следует отметить, что предварительно выбранное семейство или тип кристалла при необходимости можно изменить в процессе проектирования. Это достаточно легко сделать, если новый тип ПЛИС содержит те же виды логических и специализированных элементов (например, модули блочной памяти, умножители), которые уже используются в исходных описаниях проектируемого устройства.

____При создании нового проекта в САПР серии Xilinx ISE указывается информация о выбранном семействе и типе ПЛИС, а также об используемых средствах синтеза и моделирования. На этапе подготовки описания проектируемого устройства, кроме формирования принципиальных схем и/или исходных текстов на языке HDL, необходимо установить временные и топологические ограничения, которые должны учитываться при синтезе, размещении и трассировке проекта в кристалле. В процессе синтеза, на основании исходных модулей проекта формируется список соединений (netlist), содержащий набор примитивов или компонентов, который может быть реализован на основе элементов выбранного кристалла ПЛИС. Далее результаты синтеза используются в качестве исходных данных средствами размещения и трассировки.

____Верификация подготовленных исходных описаний разрабатываемого устройства, выполняемая методом функционального моделирования, производится без учёта реальных значений задержек прохождения сигналов и позволяет проконтролировать соответствие выходных сигналов предполагаемому алгоритму работы. На этапе размещения и трассировки проекта в кристалле производится распределение выполняемых функций в конфигурируемые логические блоки CLB (Configurable Logic Block) или макроячейки (Macrocell) в зависимости от используемого семейства ПЛИС и формирование необходимых связей. В процессе выполнения этого этапа также вычисляются реальные значения задержек распространения сигналов, которые необходимы для полного (временного) моделирования разрабатываемого устройства. Основным результатом этапа размещения и трассировки является формирование файла, в котором содержится информация о конфигурации ПЛИС, реализующей проектируемое устройство. Итогом процесса разработки цифрового устройства на основе ПЛИС является загрузка конфигурационных данных в кристалл или программирование конфигурационного ПЗУ/ППЗУ с помощью соответствующих средств САПР серии Xilinx ISE и загрузочного кабеля, варианты которого были представлены в первой части данной статьи.

____Следует обратить внимание на то, что этапы функционального и временного моделирования не являются обязательными. Тем не менее, использование эффективных средств моделирования, включаемых в состав пакетов САПР серии Xilinx ISE [1], позволяет обнаружить большинство возможных ошибок и тем самым значительно сократить общее время разработки устройства. При обнаружении ошибок на любом из этих этапов моделирования, например, логических ошибок на этапе функционального моделирования или при получении неудовлетворительных результатов временного моделирования, следует вернуться на стадию разработки исходных описаний проекта, внести необходимые изменения и повторить соответствующие этапы.

____Выполнение этапов создания нового проекта и подготовки исходных описаний проектируемого устройства не зависит от выбранного типа архитектуры ПЛИС (CPLD или FPGA), используемого для его реализации. Содержание последующих этапов (синтеза, функционального и временного моделирования, размещения, трассировки и загрузки проекта в кристалл) зависит от семейства ПЛИС – CPLD (Complex Programmable Logic Device) или FPGA (Field Programmable Gate Array) [2]. Поэтому в дальнейшем реализация этих этапов проектирования в САПР серии Xilinx ISE рассматривается отдельно для каждого типа архитектуры ПЛИС.

Рекомендации по выбору семейства и типа ПЛИС для реализации разрабатываемого устройства.

____При определении семейства и типа ПЛИС для разрабатываемого устройства необходимо, учитывая уровень его сложности и требования, предъявляемые к быстродействию, уровню потребления, условиям эксплуатации, обратить внимание на следующие технические характеристики кристаллов:

____Прежде всего, необходимо выбрать тип архитектуры ПЛИС: CPLD или FPGA. Преимуществами кристаллов семейств CPLD, выпускаемых фирмой Xilinx, являются:

____Основным недостатком ПЛИС с архитектурой CPLD является ограниченный объём логических ресурсов. Максимальное количество макроячеек (и, соответственно, триггеров) в кристаллах семейств CPLD фирмы Xilinx составляет 512. Поэтому ПЛИС данного типа целесообразно использовать для реализации цифровых устройств, большую часть которых образуют комбинационные схемы (блоки) при ограниченном объёме последовательностных схем (блоков). В настоящее время фирма Xilinx производит две серии ПЛИС с архитектурой CPLD: XC9500 и CoolRunner. В состав серии XC9500 входят три семейства недорогих кристаллов: XC9500, XC9500XL и XC9500XV, которые различаются, в основном, напряжением питания. Если проектируемое устройство должно работать в системе с напряжением питания 5 В и соответствующими уровнями входных и выходных сигналов, для его реализации рекомендуется использовать ПЛИС семейства XC9500. В тех случаях, когда необходимо обеспечить совместимость с уровнями цифровых сигналов 5 В только по входам, можно использовать кристаллы семейства XC9500XL, напряжение питания ядра которых составляет 3,3 В. Для реализации устройств, которые должны обладать совместимостью по входам с уровнями цифровых сигналов 2,5 В и/или 3,3 В, а по выходам – с 1,8 В, 2,5 В и/или 3,3 В, необходимо выбирать ПЛИС семейства XC9500XV.

____Серия CoolRunner включает два семейства кристаллов, отличающихся высоким быстродействием и низкой потребляемой мощностью: CoolRunner XPLA3 и CoolRunner-II. Напряжение питания ядра кристаллов семейства CoolRunner-II составляет 1,8 В, а блоки ввода/вывода способны работать с уровнями цифровых сигналов 1,8 В, 2,5 В и/или 3,3 В. ПЛИС семейства CoolRunner XPLA3 следует применять в тех случаях, когда проектируемое устройство должно обладать совместимостью по входам с уровнями цифровых сигналов 5 В. Более подробную информацию об особенностях и технических характеристиках ПЛИС с архитектурой CPLD, выпускаемых фирмой Xilinx, можно найти в [2, 4, 5].

____К важным преимуществам кристаллов с архитектурой FPGA относятся:

____Из пяти серий ПЛИС с архитектурой FPGA, выпускаемых фирмой Xilinx, для новых разработок рекомендованы только две: Virtex и Spartan. Серия Virtex включает в себя следующие семейства: Virtex, Virtex-E, Virtex-II, Virtex-II PRO, Virtex-4 и Virtex-5. Последние четыре семейства являются наиболее перспективными для создания высокопроизводительных цифровых устройств различного назначения, в том числе модулей и систем цифровой обработки сигналов. Кристаллы, входящие в состав этих семейств, в полной мере обладают перечисленными выше преимуществами и позволяют реализовать цифровые устройства различного уровня сложности, включая мощные многопроцессорные встраиваемые системы на кристалле [3]. Для разработки последних следует использовать семейства Virtex-II PRO, Virtex-4 и Virtex-5 с интегрированными микропроцессорными ядрами. Более подробная информация о технических параметрах ПЛИС указанных семейств представлена в [6–8]. Основным фактором, сдерживающим массовое применение ПЛИС серии Virtex, является их высокая стоимость.

____В серии Spartan в настоящее время доступны семь семейств кристаллов, которые по техническим характеристикам близки к ПЛИС серии Virtex (соответствующих семейств), но отличаются более низкой стоимостью. К наиболее перспективным семействам ПЛИС серии Spartan можно отнести Spartan 3 и Spartan-3E [9–11], рекомендуемые для серийно выпускаемых устройств.

Структура проекта разрабатываемого цифрового устройства в САПР серии Xilinx ISE.

____Прежде чем приступить к изучению этапов процесса проектирования, следует определить само понятие проекта.

____Под проектом цифрового устройства в САПР серии Xilinx ISE понимается совокупность модулей (файлов),которые содержат полную информацию, необходимую для выполнения всех этапов процесса разработки данного устройства на базе ПЛИС, включая программирование кристалла.

____В структуре проекта САПР серии Xilinx ISE можно выделить следующие группы модулей:

____Все модули проекта располагаются в одном каталоге (папке), название которого совпадает с названием проекта. Изначально проект представлен только заголовком и модулем, в котором указаны параметры проекта. Затем к проекту добавляются модули исходного описания разрабатываемого устройства. Далее, после выполнения каждого этапа процесса разработки, в проект включаются результаты, полученные на этом этапе, и соответствующий отчёт. Кроме того, разработчик может дополнить проект необходимой текстовой документацией.

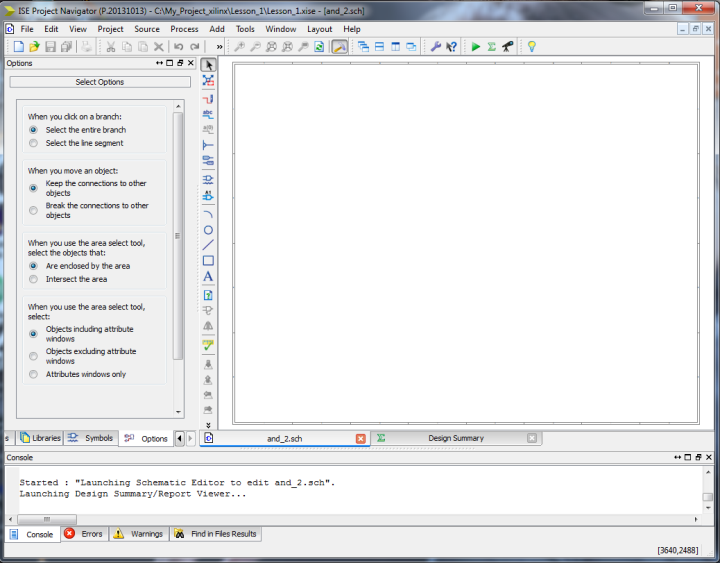

Создание нового проекта разрабатываемого устройства в САПР серии Xilinx ISE.

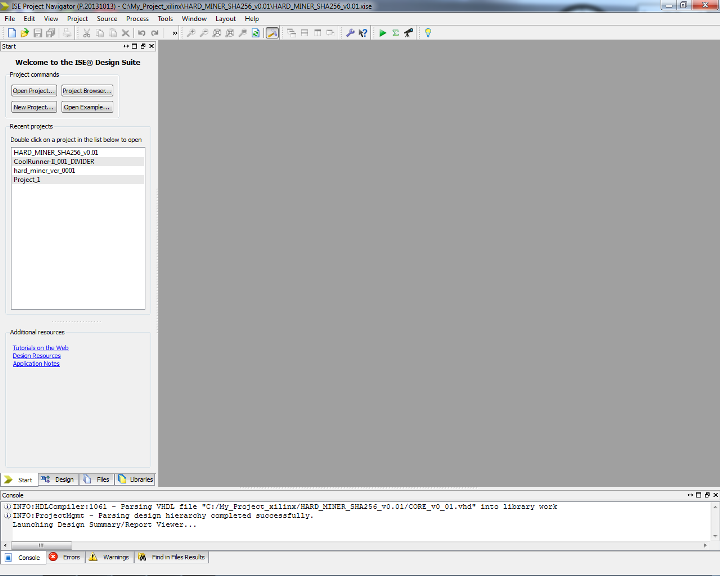

____Работа в САПР серии Xilinx ISE начинается с открытия управляющей оболочки этого пакета – Навигатора проекта (Project Navigator) – двойным щелчком левой кнопки мыши на соответствующей пиктограмме (ISE), расположенной на Рабочем столе компьютера. При отсутствии данной пиктограммы можно воспользоваться кнопкой Пуск (Start) операционной системы Windows XP/2000. В открывшейся панели необходимо выбрать строку Программы (Programs), затем в предложенном списке найти группу программ Xilinx ISE…, где следует выбрать строку Project Navigator.

При успешном выполнении указанных операций на экране монитора отображается основное окно Навигатора проекта, структура которого была подробно рассмотрена [1].

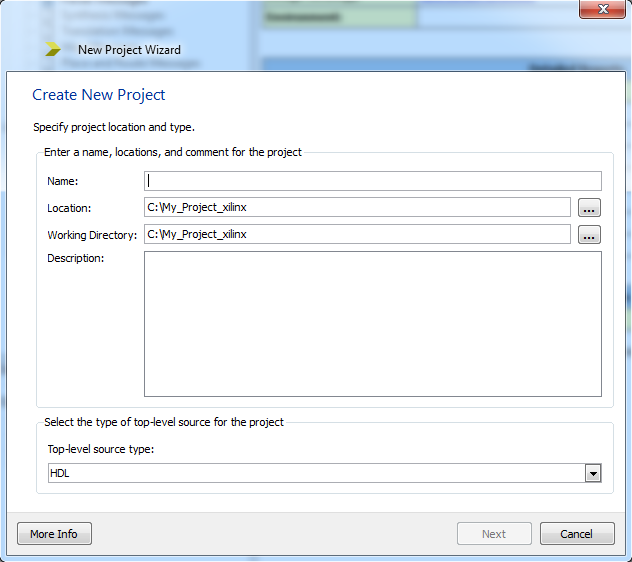

____Для создания нового проекта в САПР серии Xilinx ISE следует выполнить команду File основного меню Навигатора проекта, а затем во всплывающем меню выбрать строку New Project.

В результате запускается «мастер» формирования нового проекта – New Project Wizard. Работа «мастера» начинается с вывода на экран диалоговой панели Create New Project, в которой должны быть определены следующие необходимые исходные данные:

____В первую очередь, рекомендуется определить раздел (папку), в котором будет располагаться рабочий каталог проекта. Целесообразно хранить все проекты в специально созданном для этих целей каталоге, например, C:\Project. Каталог, в котором находятся все проекты пользователя, должен располагаться вне раздела, содержащего средства проектирования серии Xilinx ISE, чтобы при обновлении версии пакета САПР он не был случайно удалён. Местоположение проекта на диске указывается в поле редактирования Project Location. По умолчанию в поле редактирования Project Location предлагаются имена диска и каталога, которые использовались в предыдущем проекте. Изменить местоположение создаваемого проекта можно стандартными средствами ОС Windows.

____Чтобы задать имя создаваемого проекта, необходимо активизировать поле редактирования Project name, после чего ввести соответствующее название. В тексте названия могут использоваться только заглавные и строчные буквы латинского алфавита (A – Z, a – z), цифры (0 – 9) и символ подчеркивания (_). Рекомендуется задавать мнемонические имена проектов, чтобы в дальнейшем легко найти требуемый проект. Введённое название проекта автоматически добавляется в поле Project Location, определяя название рабочего каталога проекта.

____Тип (способ описания) модуля верхнего уровня иерархии проекта определяется с помощью поля выбора Top Level Source Type. Выпадающий список, который открывается при нажатии кнопки, расположенной в правой части этого поля выбора, содержит четыре варианта: HDL, Schematic, EDIF и NGC/NGO.

При использовании языков высокого уровня VHDL и Verilog для описания модуля верхнего уровня проекта в качестве значения параметра Top Level Source Type устанавливается HDL. Если исходный модуль верхнего уровня проекта будет выполнен в схемотехническом редакторе САПР серии Xilinx ISE, следует выбрать вариант Schematic. В тех случаях, когда в качестве модуля верхнего уровня иерархии предполагается использовать описания в формате EDIF или NGC/NGO, должны быть указаны соответствующие значения параметра Top Level Source Type.

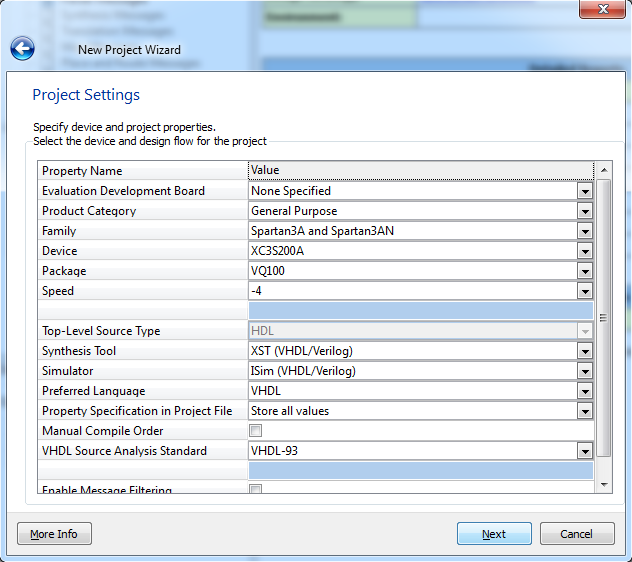

____Установка значений всех исходных параметров создаваемого проекта завершается нажатием клавиши Далее (Next), которая находится в нижней части стартовой диалоговой панели «мастера» New Project Wizard. Следует отметить, что эта клавиша становится доступной только после определения значений всех перечисленных выше параметров. Если значение какого-либо параметра не задано, данная клавиша остаётся в неактивном состоянии (отображается серым цветом). После нажатия клавиши Далее (Next), в панели Create New Project выводится очередная диалоговая панель «мастера» New Project Wizard с заголовком Device Properties, с помощью которой необходимо определить следующие параметры нового проекта:

____Категория, семейство ПЛИС, тип кристалла, корпуса, категория быстродействия, средства синтеза и моделирования указываются в форме таблицы параметров проекта. В первом столбце этой таблицы отображаются названия параметров (Property Name), во втором – значения этих характеристик (Value). Каждая ячейка столбца Value является полем соответствующего параметра. Чтобы установить требуемое значение какого-либо параметра в этой таблице, следует воспользоваться кнопкой управления выпадающим списком соответствующего поля выбора. При нажатии на эту кнопку отображается список всех возможных значений соответствующего параметра. Выбор требуемого значения осуществляется щелчком левой кнопки мыши на строке выпадающего списка, содержащей это значение. После этого указанное в данной строке значение автоматически отображается в поле выбора.

____Фирма Xilinx классифицирует все выпускаемые семейства кристаллов в соответствии с областью их применения по следующим категориям:

____Выбор категории кристаллов позволяет существенно ограничить список возможных вариантов при определении семейства ПЛИС. Чтобы указать категорию ПЛИС, необходимо в выпадающем списке значений параметра Product Category выделить название соответствующей группы. Если при выборе семейства ПЛИС требуется отобразить список всех доступных семейств кристаллов (без деления по категориям), для параметра Product Category следует выбрать значение All.

____Для определения семейства ПЛИС, на базе которого проектируется устройство, следует воспользоваться полем выбора значения параметра Family. При нажатии на кнопку управления выпадающим списком, находящуюся в правой части этого поля, отображается список семейств кристаллов, которые относятся к выбранной ранее категории ПЛИС. Если для параметра Product Category было установлено значение All, в этом списке будут перечислены названия всех семейств ПЛИС, поддерживаемых используемой версией средств проектирования серии Xilinx ISE.

____В поле выбора типа кристалла для реализации проектируемого устройства Device автоматически отображается тип ПЛИС, установленный по умолчанию для выбранного семейства. Чтобы изменить предлагаемый вариант, необходимо в выпадающем списке выбора параметра Device выделить строку, содержащую условное обозначение требуемого типа кристалла. При выборе ПЛИС семейств CPLD предусмотрена возможность автоматического определения типа кристалла, необходимого для реализации проектируемого устройства. Для этого в выпадающем списке кристаллов следует выбрать строку Automatic, и программы размещения и трассировки самостоятельно определят кристалл с минимальным количеством ресурсов, необходимых для реализации разрабатываемого устройства.

____Тип корпуса кристалла, выбранного для реализации проектируемого устройства, указывается в поле выбора Package. Если задано значение Automatic, в этом поле отображается символ «*», соответствующий режиму автоматического выбора типа корпуса. В этом случае можно указать конкретный тип корпуса с неопределённым числом выводов. Для этого следует выбрать значение <тип корпуса> из выпадающего списка поля Package. Если в поле Device указан определённый тип ПЛИС, то выпадающий список значений поля выбора Package содержит условные обозначения только тех типов корпусов, в которых выпускается данный кристалл.

____Для определения категории быстродействия выбранного кристалла предназначено поле выбора параметра Speed. Выпадающий список этого поля отображает градации быстродействия для выбранного типа ПЛИС. Если тип кристалла не конкретизирован (в поле Device указано Automatic), список содержит единственное значение «*», соответствующее режиму автоматического выбора категории быстродействия ПЛИС.

____Состав поддерживаемых средств синтеза зависит от используемой конфигурации системы проектирования серии Xilinx ISE и применяемого семейства ПЛИС. Чтобы просмотреть этот набор и при необходимости изменить средства синтеза, предлагаемые по умолчанию, следует воспользоваться полем выбора Synthesis Tool. Навигатор проекта автоматически скорректирует содержимое выпадающего списка инструментов синтеза в соответствии с конфигурацией САПР и выбранным семейством ПЛИС. По умолчанию предлагаются встроенные средства синтеза САПР серии Xilinx ISE – Xilinx Synthesis Technology (XST), которые можно рекомендовать для использования в большинстве проектов.

____Для указания средств моделирования проектируемого устройства необходимо воспользоваться полем выбора параметра Simulator. Одновременно с выбором средств моделирования указывается язык HDL, используемый для формирования моделей разрабатываемого устройства. Все конфигурации системы проектирования серии Xilinx ISE обладают собственными средствами моделирования ISE Simulator, а также поддерживают систему HDL-моделирования ModelSim [1]. В большинстве случаев рекомендуется использовать один из этих инструментов моделирования, выбрав одноименную строку в выпадающем списке значений параметра Simulator. Для применения других систем моделирования, названия которых не представлены в этом списке, следует выбрать одну из строк Other с названием используемого языка HDL.

____Диалоговая панель Device Properties позволяет также определить значения параметров, управляющих выводом информации в панели Design Summary и в окне консольных сообщений Навигатора проекта. Для этих параметров рекомендуется оставить значения по умолчанию.

____После определения значений всех параметров в диалоговой панели Device Properties, следует нажать клавишу Далее (Next), которая находится в нижней части этой панели. В результате отображается следующая диалоговая панель «мастера» New Project Wizard с заголовком Create New Source, которая предоставляет возможность создания нового модуля исходного описания разрабатываемого устройства и его включения в состав формируемого проекта. Как правило, сначала создаётся основа модуля исходного описания верхнего уровня проекта, для чего следует нажать кнопку New Source. В результате открывается диалоговая панель Select Source Type, в которой необходимо выбрать тип нового модуля, задать его имя и указать местоположение создаваемого файла на диске.