Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Конспект-1__VHDL

Страница 1 из 1 • Поделиться

Конспект-1__VHDL

Конспект-1__VHDL

1

.

____Хотя язык VHDL внешне выглядит так же, как и другие традиционные языки программирования (поскольку имеет литералы, разделители, операторы и т. д.), он обладает некоторыми важными отличительными характеристиками.

Спецификации модулей VHDL-проектов могут использовать или математические алгоритмы, описывающие их работу или описание аппаратной структуры проектируемого модуля. В соответствии с уровнями абстракций проектов описание модуля может иметь поведенческую или структурную форму.

Моделирование алгоритма работы проекта основывается на событийном принципе управления.

VHDL-проект позволяет выполнять моделирование протекания параллельных процессов в электрических схемах, временной анализ сигналов и их параметров.

VHDL поддерживается инструментальными средствами синтеза и системами автоматизированного проектирования (САПР) многих производителей программного обеспечения, которые могут создавать прямо из описания VHDL-проекта его аппаратную реализацию (связанные между собой структуры логических элементов, содержащихся в СБИС).

Используя VHDL, можно проектировать, моделировать и синтезировать практически любое цифровое устройство, начиная от простой комбинационной схемы до законченной микропроцессорной системы на СБИС.

____Перечисленные выше характеристики языка VHDL как специализированного языка описания цифровых устройств реализуются с помощью следующих языковых средств:

____В отличие от процедурных языков программирования, языковые средства которых обеспечивают выполнение вычислений над абстрактными данными и управление ими, VHDL-проект описывает цифровое устройство, учитывая его многогранность, поведение, структуру, функциональные и физические свойства, а также взаимодействие со специальной аппаратурой, физически реализующей проект цифрового устройства в СБИС.

____Остановимся особо на некоторых важных отличиях языка VHDL. VHDL по существу является языком параллельного программирования, т. е. в его конструкции существуют операторы, соответствующие логическим вентилям. Эти операторы обрабатываются (т. е. вычисляются) по параллельному принципу. Суть данного принципа состоит в том, что, как только сигнал, содержащийся в описании проектируемого цифрового устройства, изменяет своё значение (говорят, что "происходит событие на сигнале"), все операторы, принимающие участие в его обслуживании, мгновенно запускаются на выполнение и одновременно выдают конечный результат. Поэтому такие операторы называются операторами параллельной обработки (ОПО) (concurence operator). Программа написанная на VHDL, моделирует физическое поведение системы (как правило, цифровой), сигналы в которой распространяются мгновенно. Такая программа позволяет формировать временную спецификацию (время задержки распространения сигнала на логическом элементе), а также описывать систему как соединение различного рода компонентов, или функциональных блоков.

____В подавляющем большинстве случаев аппаратная реализация проекта цифрового устройства с использованием VHDL протекает в соответствии со следующими этапами:

____Разработка иерархической блок-схемы проекта. Выяснение базового конструктивно-технологического метода и стандартных блоков на уровне структурной схемы. Поскольку большие логические проекты являются, как правило, иерархическими, использование VHDL позволяет легко разить проект на модули (субпроекты) и определить их интерфейсы.

____Программирование. Запись VHDL-кода для модулей и их интерфейсов.

____Компиляция. Анализ программного кода VHDL-проекта для выявления синтаксических ошибок, а также проверка его совместимости с другими модулями. В ходе компиляции также собирается внутренняя информация о структуре проекта, которая необходима для моделирования работы проектируемого цифрового устройства.

____Моделирование. Определение и применение входных воздействий к откомпилированному коду проекта с наблюдением выходных реакций. Моделирование может выполняться как в форме функционального контроля, т. е. проверки логики работы проекта без учёта временных соотношений и задержек распространения сигналов на логических элементах, так и в качестве одного из этапов верификации завершённого проекта.

____Синтез. Преобразование VHDL-описания в набор примитивов или логических элементов, которые могут быть реализованы с учётом конкретной технологии.

____Компоновка, монтаж и разводка. Отображение проекта на карте синтезирующих элементов, содержащихся в СБИС.

____Временной анализ. Получение фактических задержек реализованной в СБИС цифровой схемы проекта с учётом длины соединений, электрических нагрузок и других известных факторов.

Для синхронного проекта наблюдаются следующие свойства:

.

Конспект-1__VHDL.

Краткая характеристика языка VHDL.

____Хотя язык VHDL внешне выглядит так же, как и другие традиционные языки программирования (поскольку имеет литералы, разделители, операторы и т. д.), он обладает некоторыми важными отличительными характеристиками.

- Проекты цифровых устройств, созданные с помощью языка VHDL, имеют, как правило, иерархическую структуру.

- Каждый автономный проектируемый модуль (субблок проектируемого цифрового устройства) имеет:

- строго определённый интерфейс взаимодействия с другими модулями;

- точную спецификацию внутреннего устройства проектируемого модуля, описывающую концепцию и функционирование модуля.

____Перечисленные выше характеристики языка VHDL как специализированного языка описания цифровых устройств реализуются с помощью следующих языковых средств:

- Библиотеки и пакеты.

- Проекты: интерфейс и архитектура проекта.

- Подпрограммы: функции и процедуры.

- Скалярные типы данных: перечислимые, числовые, физические.

- Программные элементы данных: константы, переменные, сигналы, порты, идентификаторы.

- Математические операции: логические, отношений, арифметические.

- Программные операции: установка значений сигналов, присвоение значений переменным, реализация связи портов и сигналов.

- Математические выражения: логические, алгебраические, логико-алгебраические.

- Операторы объявления программных элементов данных.

- Операторы комбинаторной логики: простой установки значения сигнала, условной установки значения сигнала, селективной установки значения сигнала, оператор process, оператор реализации компонента port map.

- Операторы регистровой логики: оператор process, оператор простой установки значения сигнала, оператор условной передачи управления, оператор цикла, оператор выбора.

____В отличие от процедурных языков программирования, языковые средства которых обеспечивают выполнение вычислений над абстрактными данными и управление ими, VHDL-проект описывает цифровое устройство, учитывая его многогранность, поведение, структуру, функциональные и физические свойства, а также взаимодействие со специальной аппаратурой, физически реализующей проект цифрового устройства в СБИС.

____Остановимся особо на некоторых важных отличиях языка VHDL. VHDL по существу является языком параллельного программирования, т. е. в его конструкции существуют операторы, соответствующие логическим вентилям. Эти операторы обрабатываются (т. е. вычисляются) по параллельному принципу. Суть данного принципа состоит в том, что, как только сигнал, содержащийся в описании проектируемого цифрового устройства, изменяет своё значение (говорят, что "происходит событие на сигнале"), все операторы, принимающие участие в его обслуживании, мгновенно запускаются на выполнение и одновременно выдают конечный результат. Поэтому такие операторы называются операторами параллельной обработки (ОПО) (concurence operator). Программа написанная на VHDL, моделирует физическое поведение системы (как правило, цифровой), сигналы в которой распространяются мгновенно. Такая программа позволяет формировать временную спецификацию (время задержки распространения сигнала на логическом элементе), а также описывать систему как соединение различного рода компонентов, или функциональных блоков.

Этапы проектирования с использованием VHDL.

____В подавляющем большинстве случаев аппаратная реализация проекта цифрового устройства с использованием VHDL протекает в соответствии со следующими этапами:

____Разработка иерархической блок-схемы проекта. Выяснение базового конструктивно-технологического метода и стандартных блоков на уровне структурной схемы. Поскольку большие логические проекты являются, как правило, иерархическими, использование VHDL позволяет легко разить проект на модули (субпроекты) и определить их интерфейсы.

____Программирование. Запись VHDL-кода для модулей и их интерфейсов.

____Компиляция. Анализ программного кода VHDL-проекта для выявления синтаксических ошибок, а также проверка его совместимости с другими модулями. В ходе компиляции также собирается внутренняя информация о структуре проекта, которая необходима для моделирования работы проектируемого цифрового устройства.

____Моделирование. Определение и применение входных воздействий к откомпилированному коду проекта с наблюдением выходных реакций. Моделирование может выполняться как в форме функционального контроля, т. е. проверки логики работы проекта без учёта временных соотношений и задержек распространения сигналов на логических элементах, так и в качестве одного из этапов верификации завершённого проекта.

____Синтез. Преобразование VHDL-описания в набор примитивов или логических элементов, которые могут быть реализованы с учётом конкретной технологии.

____Компоновка, монтаж и разводка. Отображение проекта на карте синтезирующих элементов, содержащихся в СБИС.

____Временной анализ. Получение фактических задержек реализованной в СБИС цифровой схемы проекта с учётом длины соединений, электрических нагрузок и других известных факторов.

Для синхронного проекта наблюдаются следующие свойства:

- число тактовых цепей в проекте минимально, в идеальном варианте все модули используют один тактовый сигнал, формируемый аппаратным модулем микросхемы ПЛИС (FPGA), (DCM, CMT, MMCM или иным, специфичным для данного семейства);

- все модули используют синхронный сброс;

- все модули используют только один перепад тактового сигнала (как правило, фронт);

- используются триггеры, а не защёлки;

- при наличии нескольких тактовых сигналов переход данных от одного тактового домена к другому осуществляется через специальные схемы синхронизации;

- выводы ПЛИС являются выходами регистра, входные сигналы записываются в регистры насколько возможно быстро;

- критичные цепи конвейеризованы.

.

Последний раз редактировалось: Viktor2312 (Чт Май 02 2019, 20:17), всего редактировалось 13 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

2

.

____Проект любого цифрового устройства на языке VHDL - это прежде всего программа, которая содержит ключевые и зарезервированные слова. Эти слова не могут использоваться как имена сигналов и как идентификаторы. В языке VHDL ключевые слова, зарезервированные слова и определяемые пользователем идентификаторы нечувствительны к регистру.

____Строки с комментариями в VHDL-программе начинаются с двух смежных дефисов ( -- ) и при компиляции игнорируются компилятором так же, как символы конца строки и пробелы.

____VHDL - это строго типизированный язык. Это означает, что все программные элементы данных (константа, переменная, сигнал) должны явно объявляться с обязательным указанием типа элемента. Тип, указанный в объявлении программного элемента данных, определяет информационные характеристики этого элемента, диапазон допустимых числовых значений, которые может принимать этот программный элемент, а также операции, которые могут над ним выполняться. Кроме того, в языке VHDL, в отличие от других строго типизированных языков, не допускаются операции над разнотипными элементами без предварительного преобразования типов.

____В языке VHDL (как и в классических языках программирования) из ключевых, зарезервированных слов и других лексических элементов строятся образования, которые принято называть операторами. Оператором в языке VHDL считается любая запись начинающаяся с ключевого слова и заканчивающаяся символом точки с запятой ( ; ).

____В языке VHDL операторы с точки зрения их функционального программного назначения (как при поведенческой, так и при структурной методологии описания проектов) принято делить на две основные группы:

____Кроме основных операторов в языке VHDL принято выделять ещё одну группу операторов, которую называют вспомогательными операторами передачи управления.

____С точки зрения конструктивного устройства операторы обеих групп принято подразделять на два класса:

____В структуре языка VHDL имеется два фундаментальных оператора (составные по своему конструктивному устройству), которые поддерживают принцип системного проектирования. Принцип системного проектирования предполагает, что любое проектируемое цифровое устройство рассматривается как автономная подсистема, которая должна иметь:

____Такими фундаментальными операторами в языке VHDL являются операторы:

entity ... end entity ... ;

architecture ... end architecture ... ;

____Проект цифрового устройства, или его компонент, описанный с помощью языка VHDL, хранится в файле, который обычно снабжается расширением VHD.

____Представленный в виде VHD-файла проект цифрового устройства может содержать другие объекты (подсистемы), которые в таком случае являются подчинёнными компонентами системы верхнего уровня.

____Любой компонент, независимо от того, является ли он автономным либо подчинённым компонентом, или же системой верхнего уровня, в свою очередь является совокупностью интерфейса (entity) и архитектуры (architecture).

____В объявлении интерфейса (entity declaration) содержится объявление портов (ports declaration) проектируемого компонента с внешним миром. Объявление портов проектируемого компонента определяет внешние входные и выходные интерфейсные сигналы, в то время как архитектура представляет собой набор таких взаимосвязанных программных элементов, как подчинённые компоненты, операторы process, операторы параллельных вычислений, последовательные операторы, подпрограммы. В типичном проекте содержится несколько таких взаимосвязанных объектов, предназначенных для выполнения преобразований, в ходе которых и обеспечивается собственно требуемая функциональность проекта.

____В соответствии с синтаксисом языка VHDL объявление интерфейса проектируемого компонента начинается с ключевого слова entity и определяет имя компонента, а также содержит объявление входных и выходных портов. Общий синтаксис объявления интерфейса имеет такой вид:

____Как видно из приведённого синтаксиса, объявление интерфейса всегда начинается с ключевого слова entity, за которым указываются имя проектируемого компонента и ключевое слово is. Далее в объявлении интерфейса с помощью ключевого слова port размещается объявление портов. Объявление интерфейса всегда заканчивается ключевым словом end, после которого могут указываться ключевое слово entity, а также имя компонента (два последних элемента в объявлении интерфейса можно опускать).

____Входящие в конструкцию объявления интерфейса проектируемого компонента (т. е. проектируемого цифрового устройства) элементы имеют следующее назначение:

тип - зарезервированное слово, используемое для объявления определённого пользователем типа сигнала, переменной или константы. Примерами встроенных типов являются: bit, bit_vector, Boolean, character, std_logic и std_ulogic.

bit - может принимать значение или 0, или 1;

bit_vector - зарезервированное слово, показывающее, что сигнал, переменная или константа являются вектором, состоящим из значений типа bit, например bit_vector (0 to 7) ;

std_logic, std_ulogic, std_logic_vector, std_ulogic_vector - зарезервированные слова, показывающие, что сигнал, переменная или константа могут принимать одно из девяти значений, отражающих его силу и реальные физические значения. В проектах цифровых устройств предпочтительнее использовать типы std_logic, std_ulogic, чем типы bit, bit_vector;

boolean - зарезервированное слово, означающее, что сигнал, переменная или константа могут принимать одно из двух значений: TRUE или FALSE;

integer - зарезервированное слово, означающее, что сигнал, переменная или константа могут принимать одно целое значение, попадающее в указанный диапазон;

real - зарезервированное слово, означающее, что сигнал, переменная или константа могут принимать одно вещественное значение, попадающее в указанный диапазон;

character - зарезервированное слово, означающее, что сигнал, переменная или константа могут принимать значение печатаемого ASCII-символа;

time - зарезервированное слово, означающее, что сигнал или константа снабжены единицей измерения времени.

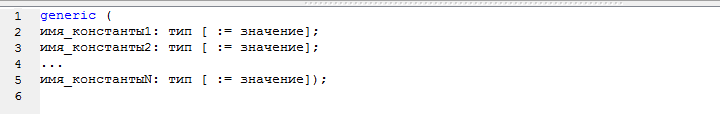

generic (общие объявления) : - объявление generic является факультативным и определяет локальные константы, используемые для задания временных параметров и разрядности (например, разрядности шины) проектируемого цифрового устройства. В объявлении generic могут указываться значения, используемые по умолчанию. Синтаксис для объявления generic следующий:

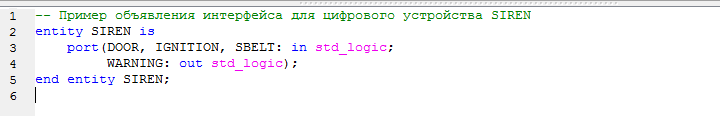

____Для примера цифровое устройство SIREN, структурное представление которого показано на рисунке ниже:

объявление интерфейса имеет следующий вид:

____Как видно из объявления, проектируемый интерфейс имеет идентификатор SIREN, содержит три входных порта (DOOR, IGNITION и SBELT) и один выходной порт (WARNING). Обратите внимание на порядок их размещения и наличие в оформлении точек с запятой! Входные порты обозначены с помощью ключевого слова in, а выходные - с помощью ключевого слова out. Так как язык VHDL является языком со строгим контролем типов, в объявлении каждого порта имеется указание о его информационном типе. Тип определяет набор значений, которые могут присваиваться объекту (в данном случае - сигналу). В этом проекте мы использовали тип std_logig/. Это наиболее предпочтительный тип для цифровых сигналов. В отличии от типа bit, который обеспечивает поддержку только бинарных значений `1` или `0`, типы std_logic и std_ulogic позволяют присваивать соответствующим элементам данных одно из девяти значений.

____Использование типа std_logic и std_ulogic даёт возможность точнее описать значения физической цифровой системы. В общем случае в физической цифровой системе сигнал может принимать бинарные значения `0` или `1`, `X` (неизвестное значение), `U` (неициализированное значение),

`-`(безразличное состояние) и ряд других. Определение типа std_logic находится в пакете std_logic_1164 библиотеки ieee. Тип определяет набор значений, которые объект может иметь.

____Приведём ещё два примера объявлений интерфейсов проектируемых объектов:

____Анализируя синтаксис объявления интерфейса, можно заключить следующее: любой проект цифрового устройства реализуется в языке VHDL с помощью оператора entity... end entity...;. Этот оператор по своей конструкции является составным оператором и содержит другие операторы. Так, в приведённых выше примерах составной оператор имеет в своей конструкции оператор port(...);.

____Архитектура проекта (architecture body) определяет логику работы схемы проектируемого цифрового устройства, т. е. устанавливает алгоритм работы цифрового устройства, и форму её реализации (поведенческая или структурная).

____Синтаксис объявления архитектуры проекта имеет следующий вид:

____Поведенческая форма архитектуры проекта SIREN, представленного на рисунке выше, имеет следующий вид:

____В строке заголовка архитектуры проекта присутствует идентификатор архитектуры (в данном примере behav), который играет роль имени архитектуры и связывает эту архитектуру с объявлением интерфейса SIREN. В качестве имени архитектуры может использоваться любой идентификатор, выбираемый пользователем, при условии соответствия его синтаксиса требованиям языка VHDL. В рассматриваемом примере компонент SIREN не имеет явно оформленного раздела объявлений в следствии его ненадобности. Основная часть архитектуры проекта (раздел выполняемых операторов параллельной обработки) начинается ключевым словом begin. Он обычно содержит описание внутреннего устройства (т. е. функциональности) проекта в форме булевых функций, оформленных в виде операторов параллельной обработки языка VHDL.

____Как говорилось выше, поведенческая форма проекта может быть описана несколькими способами. В частности, в этом примере основная часть архитектуры проекта содержит один простой оператор установки значения сигнала. В данном операторе имеется символ `<=`, который означает, что сигналу, стоящему слева от символа `<=`, устанавливается результат вычисления выражения, стоящего справа от символа `<=`. Основная часть архитектуры проекта заканчивается ключевым словом and, которое может дополняться ключевым словом architecture и именем архитектуры.

____Рассмотрим ещё два примера оформления архитектуры проекта.

____Операторы установки значения сигнала (`<=`) в этих примерах содержат логические операции and, or и not. Кроме указанных, в таких операциях могут использоваться операции nand, nor, xor и xnor.

____Проект SIREN, показанный на рисунке выше, можно также создать, используя структурную форму архитектуры, которая сводится к описанию проекта через набор логических элементов, или компонентов, и связей между их входами и выходами. Вариант такого структурного описания имеет следующий вид:

____Если архитектура проекта имеет структурную форму, после заголовка архитектуры располагаются объявления компонентов, которые предполагается использовать в проекте. В приведённом выше примере проекта SIREN использованы два двухвходовых логических элемента AND, один двухвходовой логический элемент OR и инвертор. Эти компоненты должны быть определены, т. е. их VHDL-проекты должны уже существовать (объявления интерфейсов этих элементов приведены в предыдущих примерах). Все VHDL-проекты компонентов цифровых устройств также могут быть сохранены в виде одного пакета (package), доступ к которому можно получить включая объявления библиотек и пакетов в заголовок проекта. Объявления компонентов содержат описания входных (например in1, in2) и выходных (например, out1) портов.

____Затем необходимо определить внутренние связи путём объявления именованных сигналов. В нашем примере эти внутренние сигналы имеют имена DOOR_NOT, SBELT_NOT, B1, B2. Обратите внимание на то, что в объявлении сигнала всегда требуется указывать его тип.

____При структурной форме в разделе выполняемых операторов архитектуры проекта (т. е. после ключевого слова begin) должны располагаться операторы реализации компонентов, а также операторы, описывающие взаимосвязь компонентов между собой. Каждый оператор реализации создаёт новый уровень иерархии начинается с имени реализуемого экземпляра компонента (например, U0), сопровождаемого двоеточием, идентификатором самого компонента и ключевым словом port map. Говорят, что оператор port map реализует междукомпонентные связи объявляемого в нём конкретного экземпляра компонента.

____В частности, в рассматриваемом примере междукомпонентные связи экземпляра U0 компонента NOT1 определены посредством позиционной (неявной) реализации: внешний сигнал DOOR соответствует входу in1 логического компонента NOT1, а внутренний сигнал DOOR_NOT - выходу компонента NOT1. Точно так же для экземпляра U2: AND2 первые два сигнала (IGNITION и DOOR_NOT) соответствуют входам in1 и in2 компонента AND2 соответственно, а сигнал B1 - выходу out1 этого компонента.

____Альтернативный метод определения межкомпонентных связей состоит в использовании именованной (явной) реализации связей между портами. В этом случае синтаксис оператора реализации имеет следующий вид:

экземпляр: компонент port map (порт1 => сигнал1, порт2 => сигнал2, ..., портN => сигналN);

____Обратите внимание на то, что порядок, в котором эти операторы приведены в разделе выполняемых операторов архитектуры проекта, не имеет никакого значения и не сказывается на конечном результате, так как эти операторы выполняются параллельно. Это объясняется тем, что схемное решение, которое описано этими операторами (проект SIREN), не зависит от порядка расположения операторов, поскольку оно фактически определяется списком выбранных компонентов и жёстко установленными соединениями между ними.

____Теперь вернёмся к тому обстоятельству, что структурная форма архитектуры, как уже отмечалось выше, позволяет создать иерархический VHDL-проект, в котором заранее определённые компоненты можно использовать многократно. Тоже самое относится и к самому высокоуровневому проекту, который в свою очередь может являться компонентом для проекта ещё более высокого уровня иерархии, и т. д. Это свойство VHDL-проектов позволяет значительно упростить графические изображения больших интегральных цифровых устройств. Таким образом, несложно придти к заключению о том, что иерархическое проектирование всегда предпочтительнее, чем одноуровневое.

____Давайте рассмотрим использование иерархической технологии проектирования на примере проекта 4-битного сумматора, показанного на рисунке ниже:

Как известно, любой полный однобитный сумматор может быть описан следующими булевыми выражениями, используемыми для получения суммы (sum) и сигнала переноса (carry) см. верхнюю часть рисунка.

____В VHDL-проекте FOURBITADD мы определим субпроект (т. е. VHDL-проект более низкого уровня иерархии) полного однобитного сумматора FULLADDER, а затем используем его в качестве компонента основного проекта. Обратите внимание на то, что архитектура fulladder_behav проекта FULLADDER имеет компонентную форму, поскольку в ней не нужно использовать несколько экземпляров одного и того же компонента. Архитектурой fouradder_structure проекта FOURBITADD, имеющей структурную форму, реализуется четыре экземпляра полного однобитного сумматора. Обратите внимание также на ключевое слово use, задействованное в проекте FOURBITADD, с помощью которого к проекту подключаются внешние библиотеки и пакеты.

____Обратите внимание на то, что в проекте 4-битного сумматора использованы те же самые имена для входных портов, что и для портов полного однобитного сумматора (они названы a и b). Это не вызывает проблем в языке VHDL, так как эти названия относятся к разным уровням иерархического проекта. Однако для обеспечения восприятия текстов VHDL-проектов на практике желательно назначать более осмысленные и уникальные имена.

____Библиотека (library) в VHDL - это нечто вроде каталога, в котором компилятор получает недостающую информацию, используемую в разрабатываемом проекте, но отсутствующую в явном виде в самом проекте. В качестве пакета (package) компиляторы VHDL используют библиотечные файлы или модули, которые содержат объявления наиболее задействованных объектов: типов данных, компонентов, сигналов, процедур и функций и т. п. Применение пакетов позволяет подобные объекты многократно использовать в разных VHDL-проектах.

____Например, как отмечалось выше, тип данных std_logic определён в пакете ieee.std_logic_1164, который входит в библиотеку ieee. Поэтому, чтобы в VHDL-проекте использовать тип std_logic, требуется подключить к проекту соответствующие библиотеку и проект. Эти операции выполняются в начале VHDL-проекта с помощью ключевых слов library и use соответственно, например, таким образом:

____Расширение .all означает, что в проекте можно использовать описания всех объектов, содержащихся в пакете ieee.std_logic_1164.

____Большинство САПР VHDL поддерживают работу с библиотекой ieee, в состав которой входят следующие пакеты:

____Чтобы задействовать любой из этих пакетов, нужно включить в состав проекта операторы объявления требуемых библиотек и пакетов, вида:

____Очень популярной библиотекой также является библиотека SYNOPSYS, которая содержит пакет SYNOPSYS.attributes.all с описаниями атрибутов:

library SYNOPSYS;

use SYNOPSYS.attributes.all;

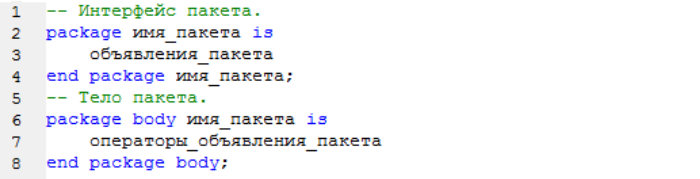

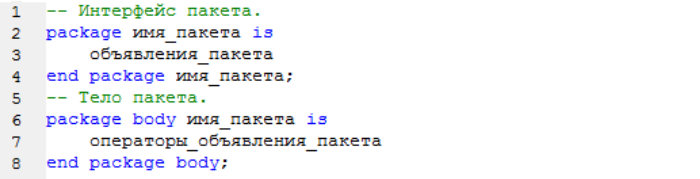

____Разработчик цифрового устройства может создать и затем подключить к проекту собственный пакет. Объявление пакета должно удовлетворять следующему синтаксису:

Например, базовые логические функции and2, or2, nand2, nor2, xor2 и т. д. необходимо предварительно определить как компоненты, прежде чем их можно будет использовать в этом качестве в разрабатываемом проекте. Определить базовые логические функции в качестве компонентов можно, например, в пакете с именем basic_func таким образом:

____Здесь следует обратить внимание на то, что в интерфейсе пакета в подразделе component указано время задержки 5нс (delay: time := 5 ns). Следует заметить, что явное указание времени задержки игнорируется многими инструментальными средствами синтеза. В конструкции разрабатываемого пакета использован встроенный тип std_logic, который объявлен в пакете std_logic_1164. Для достижения видимости описания типа std_logic из разрабатываемого пакета в него включены операторы

library ieee;

и

use ieee.std_logic_1164.all;

____Созданный пакет должен быть откомпилирован и помещён в пользовательскую библиотеку. Такую библиотеку можно именовать как my_func, в создаваемом проекте требуется подключить эту библиотеку my_func и пакет basic_func с помощью операторов следующего вида:

.

Базовая структура VHDL-файла.

Общие сведения.

____Проект любого цифрового устройства на языке VHDL - это прежде всего программа, которая содержит ключевые и зарезервированные слова. Эти слова не могут использоваться как имена сигналов и как идентификаторы. В языке VHDL ключевые слова, зарезервированные слова и определяемые пользователем идентификаторы нечувствительны к регистру.

____Строки с комментариями в VHDL-программе начинаются с двух смежных дефисов ( -- ) и при компиляции игнорируются компилятором так же, как символы конца строки и пробелы.

____VHDL - это строго типизированный язык. Это означает, что все программные элементы данных (константа, переменная, сигнал) должны явно объявляться с обязательным указанием типа элемента. Тип, указанный в объявлении программного элемента данных, определяет информационные характеристики этого элемента, диапазон допустимых числовых значений, которые может принимать этот программный элемент, а также операции, которые могут над ним выполняться. Кроме того, в языке VHDL, в отличие от других строго типизированных языков, не допускаются операции над разнотипными элементами без предварительного преобразования типов.

____В языке VHDL (как и в классических языках программирования) из ключевых, зарезервированных слов и других лексических элементов строятся образования, которые принято называть операторами. Оператором в языке VHDL считается любая запись начинающаяся с ключевого слова и заканчивающаяся символом точки с запятой ( ; ).

____В языке VHDL операторы с точки зрения их функционального программного назначения (как при поведенческой, так и при структурной методологии описания проектов) принято делить на две основные группы:

- Операторы объявления программных элементов данных и их типов, компонентов проектируемого цифрового устройства, их интерфейсов и архитектур, пользовательских типов, а также функций и процедур.

- Выполняемые операторы.

____Кроме основных операторов в языке VHDL принято выделять ещё одну группу операторов, которую называют вспомогательными операторами передачи управления.

____С точки зрения конструктивного устройства операторы обеих групп принято подразделять на два класса:

- Простые (однострочные) операторы. Простой оператор представляет собой текстовую запись, располагающуюся, как правило, на одной строке, которая не содержит других операторов.

- Составные (многострочные) операторы. Составной оператор представляет собой текстовую запись, занимающую, как правило, много строк, которые содержат другие операторы.

____В структуре языка VHDL имеется два фундаментальных оператора (составные по своему конструктивному устройству), которые поддерживают принцип системного проектирования. Принцип системного проектирования предполагает, что любое проектируемое цифровое устройство рассматривается как автономная подсистема, которая должна иметь:

- идентификатор (т. е. должна быть объявлена);

- способность взаимодействовать с другими проектируемыми подсистемами посредством своего интерфейса (входных/выходных портов);

- описание внутренней структуры или алгоритма функционирования.

____Такими фундаментальными операторами в языке VHDL являются операторы:

entity ... end entity ... ;

architecture ... end architecture ... ;

____Проект цифрового устройства, или его компонент, описанный с помощью языка VHDL, хранится в файле, который обычно снабжается расширением VHD.

____Представленный в виде VHD-файла проект цифрового устройства может содержать другие объекты (подсистемы), которые в таком случае являются подчинёнными компонентами системы верхнего уровня.

____Любой компонент, независимо от того, является ли он автономным либо подчинённым компонентом, или же системой верхнего уровня, в свою очередь является совокупностью интерфейса (entity) и архитектуры (architecture).

____В объявлении интерфейса (entity declaration) содержится объявление портов (ports declaration) проектируемого компонента с внешним миром. Объявление портов проектируемого компонента определяет внешние входные и выходные интерфейсные сигналы, в то время как архитектура представляет собой набор таких взаимосвязанных программных элементов, как подчинённые компоненты, операторы process, операторы параллельных вычислений, последовательные операторы, подпрограммы. В типичном проекте содержится несколько таких взаимосвязанных объектов, предназначенных для выполнения преобразований, в ходе которых и обеспечивается собственно требуемая функциональность проекта.

Объявление интерфейса.

____В соответствии с синтаксисом языка VHDL объявление интерфейса проектируемого компонента начинается с ключевого слова entity и определяет имя компонента, а также содержит объявление входных и выходных портов. Общий синтаксис объявления интерфейса имеет такой вид:

____Как видно из приведённого синтаксиса, объявление интерфейса всегда начинается с ключевого слова entity, за которым указываются имя проектируемого компонента и ключевое слово is. Далее в объявлении интерфейса с помощью ключевого слова port размещается объявление портов. Объявление интерфейса всегда заканчивается ключевым словом end, после которого могут указываться ключевое слово entity, а также имя компонента (два последних элемента в объявлении интерфейса можно опускать).

____Входящие в конструкцию объявления интерфейса проектируемого компонента (т. е. проектируемого цифрового устройства) элементы имеют следующее назначение:

- Имя_компонента - определённый пользователем идентификатор проекта.

- сигнал - список разделяемых запятыми идентификаторов, представляющих внешние интерфейсные сигналы (порты проекта).

- режим - ключевое слово, показывающее направление действия сигнала (порта):

- in - ключевое слово, используемое для объявления входных сигналов;

- out - ключевое слово, используемое для объявления выходных сигналов. Значения выходных сигналов могут считываться другими проектами;

- buffer - ключевое слово, используемое для объявления внутренних сигналов. Значения сигнала с этого порта могут читаться только внутри архитектуры проекта;

- inout - ключевое слово, используемое для объявления сигналов, которые могут быть как входными, так и выходными.

____Для примера цифровое устройство SIREN, структурное представление которого показано на рисунке ниже:

объявление интерфейса имеет следующий вид:

____Как видно из объявления, проектируемый интерфейс имеет идентификатор SIREN, содержит три входных порта (DOOR, IGNITION и SBELT) и один выходной порт (WARNING). Обратите внимание на порядок их размещения и наличие в оформлении точек с запятой! Входные порты обозначены с помощью ключевого слова in, а выходные - с помощью ключевого слова out. Так как язык VHDL является языком со строгим контролем типов, в объявлении каждого порта имеется указание о его информационном типе. Тип определяет набор значений, которые могут присваиваться объекту (в данном случае - сигналу). В этом проекте мы использовали тип std_logig/. Это наиболее предпочтительный тип для цифровых сигналов. В отличии от типа bit, который обеспечивает поддержку только бинарных значений `1` или `0`, типы std_logic и std_ulogic позволяют присваивать соответствующим элементам данных одно из девяти значений.

____Использование типа std_logic и std_ulogic даёт возможность точнее описать значения физической цифровой системы. В общем случае в физической цифровой системе сигнал может принимать бинарные значения `0` или `1`, `X` (неизвестное значение), `U` (неициализированное значение),

`-`(безразличное состояние) и ряд других. Определение типа std_logic находится в пакете std_logic_1164 библиотеки ieee. Тип определяет набор значений, которые объект может иметь.

____Приведём ещё два примера объявлений интерфейсов проектируемых объектов:

Примечание. В языке VHDL любой конструктивный элемент, начинающийся некоторым ключевым словом и заканчивающийся ключевым словом end и символом " ; " (точка с запятой), принято называть составным оператором. Однако операторы могут быть не только составными, т. е. содержащие в себе другие операторы (часто говорят, что составные операторы "содержат тело"), но и простыми. Простые операторы размещаются обычно в одной строке, не имеют ключевого слова end и всегда заканчиваются символом " ; " (точка с запятой).

____Анализируя синтаксис объявления интерфейса, можно заключить следующее: любой проект цифрового устройства реализуется в языке VHDL с помощью оператора entity... end entity...;. Этот оператор по своей конструкции является составным оператором и содержит другие операторы. Так, в приведённых выше примерах составной оператор имеет в своей конструкции оператор port(...);.

Архитектура проекта.

____Архитектура проекта (architecture body) определяет логику работы схемы проектируемого цифрового устройства, т. е. устанавливает алгоритм работы цифрового устройства, и форму её реализации (поведенческая или структурная).

Примечание. Как говорилось выше, VHDL-проект цифрового устройства может иметь разные формы представления: поведенческую, структурную или их комбинацию.

____Синтаксис объявления архитектуры проекта имеет следующий вид:

Архитектура проекта в поведенческой форме.

____Поведенческая форма архитектуры проекта SIREN, представленного на рисунке выше, имеет следующий вид:

____В строке заголовка архитектуры проекта присутствует идентификатор архитектуры (в данном примере behav), который играет роль имени архитектуры и связывает эту архитектуру с объявлением интерфейса SIREN. В качестве имени архитектуры может использоваться любой идентификатор, выбираемый пользователем, при условии соответствия его синтаксиса требованиям языка VHDL. В рассматриваемом примере компонент SIREN не имеет явно оформленного раздела объявлений в следствии его ненадобности. Основная часть архитектуры проекта (раздел выполняемых операторов параллельной обработки) начинается ключевым словом begin. Он обычно содержит описание внутреннего устройства (т. е. функциональности) проекта в форме булевых функций, оформленных в виде операторов параллельной обработки языка VHDL.

____Как говорилось выше, поведенческая форма проекта может быть описана несколькими способами. В частности, в этом примере основная часть архитектуры проекта содержит один простой оператор установки значения сигнала. В данном операторе имеется символ `<=`, который означает, что сигналу, стоящему слева от символа `<=`, устанавливается результат вычисления выражения, стоящего справа от символа `<=`. Основная часть архитектуры проекта заканчивается ключевым словом and, которое может дополняться ключевым словом architecture и именем архитектуры.

____Рассмотрим ещё два примера оформления архитектуры проекта.

____Операторы установки значения сигнала (`<=`) в этих примерах содержат логические операции and, or и not. Кроме указанных, в таких операциях могут использоваться операции nand, nor, xor и xnor.

Примечание. Следует особо заметить, что операторы установки значения сигнала (signal assignment statement) в вышеупомянутых примерах являются операторами параллельной обработки (concurrent processing). Такие операторы выполняются параллельно, когда один или больше сигналов, входящих в состав выражений, которые расположены в правой части оператора, изменяют своё значение (т. е. когда хотя бы на одном из сигналов происходит событие). Например, когда сигнал порта А изменит своё значение, одновременно изменят своё значение внутренние сигналы X и Y, которые в свою очередь одновременно (во всяком случае в идеале) заставят последний оператор модифицировать значение сигнала на выходном порту Z. (В реальных цифровых системах при распространении сигналов может существовать задержка, связанная с этими изменениями).

Физические цифровые устройства управляются данными, а также событиями, возникающими при изменении данных. То есть событие, которое происходит на одном из сигналов, приводит к появлению события на другом сигнале, и т. д. Выполнение операторов детерминировано потоком изменения значений сигналов, т. е. определено последовательностью возникновения событий на сигналах. В результате такого принципа функционирования порядок, в котором операторы параллельной обработки располагаются в основной части архитектуры проекта, может быть любым. Иными словами, если разместить оператор Z перед операторами X и Y, конечный результат от этого не изменится. В этом состоит главное отличие языка VHDL от языков программирования, в которых операторы выполняются последовательно или путём вызова процедур.

Архитектура проекта в структурной форме.

____Проект SIREN, показанный на рисунке выше, можно также создать, используя структурную форму архитектуры, которая сводится к описанию проекта через набор логических элементов, или компонентов, и связей между их входами и выходами. Вариант такого структурного описания имеет следующий вид:

____Если архитектура проекта имеет структурную форму, после заголовка архитектуры располагаются объявления компонентов, которые предполагается использовать в проекте. В приведённом выше примере проекта SIREN использованы два двухвходовых логических элемента AND, один двухвходовой логический элемент OR и инвертор. Эти компоненты должны быть определены, т. е. их VHDL-проекты должны уже существовать (объявления интерфейсов этих элементов приведены в предыдущих примерах). Все VHDL-проекты компонентов цифровых устройств также могут быть сохранены в виде одного пакета (package), доступ к которому можно получить включая объявления библиотек и пакетов в заголовок проекта. Объявления компонентов содержат описания входных (например in1, in2) и выходных (например, out1) портов.

____Затем необходимо определить внутренние связи путём объявления именованных сигналов. В нашем примере эти внутренние сигналы имеют имена DOOR_NOT, SBELT_NOT, B1, B2. Обратите внимание на то, что в объявлении сигнала всегда требуется указывать его тип.

____При структурной форме в разделе выполняемых операторов архитектуры проекта (т. е. после ключевого слова begin) должны располагаться операторы реализации компонентов, а также операторы, описывающие взаимосвязь компонентов между собой. Каждый оператор реализации создаёт новый уровень иерархии начинается с имени реализуемого экземпляра компонента (например, U0), сопровождаемого двоеточием, идентификатором самого компонента и ключевым словом port map. Говорят, что оператор port map реализует междукомпонентные связи объявляемого в нём конкретного экземпляра компонента.

____В частности, в рассматриваемом примере междукомпонентные связи экземпляра U0 компонента NOT1 определены посредством позиционной (неявной) реализации: внешний сигнал DOOR соответствует входу in1 логического компонента NOT1, а внутренний сигнал DOOR_NOT - выходу компонента NOT1. Точно так же для экземпляра U2: AND2 первые два сигнала (IGNITION и DOOR_NOT) соответствуют входам in1 и in2 компонента AND2 соответственно, а сигнал B1 - выходу out1 этого компонента.

____Альтернативный метод определения межкомпонентных связей состоит в использовании именованной (явной) реализации связей между портами. В этом случае синтаксис оператора реализации имеет следующий вид:

экземпляр: компонент port map (порт1 => сигнал1, порт2 => сигнал2, ..., портN => сигналN);

____Обратите внимание на то, что порядок, в котором эти операторы приведены в разделе выполняемых операторов архитектуры проекта, не имеет никакого значения и не сказывается на конечном результате, так как эти операторы выполняются параллельно. Это объясняется тем, что схемное решение, которое описано этими операторами (проект SIREN), не зависит от порядка расположения операторов, поскольку оно фактически определяется списком выбранных компонентов и жёстко установленными соединениями между ними.

____Теперь вернёмся к тому обстоятельству, что структурная форма архитектуры, как уже отмечалось выше, позволяет создать иерархический VHDL-проект, в котором заранее определённые компоненты можно использовать многократно. Тоже самое относится и к самому высокоуровневому проекту, который в свою очередь может являться компонентом для проекта ещё более высокого уровня иерархии, и т. д. Это свойство VHDL-проектов позволяет значительно упростить графические изображения больших интегральных цифровых устройств. Таким образом, несложно придти к заключению о том, что иерархическое проектирование всегда предпочтительнее, чем одноуровневое.

____Давайте рассмотрим использование иерархической технологии проектирования на примере проекта 4-битного сумматора, показанного на рисунке ниже:

Как известно, любой полный однобитный сумматор может быть описан следующими булевыми выражениями, используемыми для получения суммы (sum) и сигнала переноса (carry) см. верхнюю часть рисунка.

____В VHDL-проекте FOURBITADD мы определим субпроект (т. е. VHDL-проект более низкого уровня иерархии) полного однобитного сумматора FULLADDER, а затем используем его в качестве компонента основного проекта. Обратите внимание на то, что архитектура fulladder_behav проекта FULLADDER имеет компонентную форму, поскольку в ней не нужно использовать несколько экземпляров одного и того же компонента. Архитектурой fouradder_structure проекта FOURBITADD, имеющей структурную форму, реализуется четыре экземпляра полного однобитного сумматора. Обратите внимание также на ключевое слово use, задействованное в проекте FOURBITADD, с помощью которого к проекту подключаются внешние библиотеки и пакеты.

____Обратите внимание на то, что в проекте 4-битного сумматора использованы те же самые имена для входных портов, что и для портов полного однобитного сумматора (они названы a и b). Это не вызывает проблем в языке VHDL, так как эти названия относятся к разным уровням иерархического проекта. Однако для обеспечения восприятия текстов VHDL-проектов на практике желательно назначать более осмысленные и уникальные имена.

Библиотеки и пакеты.

____Библиотека (library) в VHDL - это нечто вроде каталога, в котором компилятор получает недостающую информацию, используемую в разрабатываемом проекте, но отсутствующую в явном виде в самом проекте. В качестве пакета (package) компиляторы VHDL используют библиотечные файлы или модули, которые содержат объявления наиболее задействованных объектов: типов данных, компонентов, сигналов, процедур и функций и т. п. Применение пакетов позволяет подобные объекты многократно использовать в разных VHDL-проектах.

____Например, как отмечалось выше, тип данных std_logic определён в пакете ieee.std_logic_1164, который входит в библиотеку ieee. Поэтому, чтобы в VHDL-проекте использовать тип std_logic, требуется подключить к проекту соответствующие библиотеку и проект. Эти операции выполняются в начале VHDL-проекта с помощью ключевых слов library и use соответственно, например, таким образом:

____Расширение .all означает, что в проекте можно использовать описания всех объектов, содержащихся в пакете ieee.std_logic_1164.

____Большинство САПР VHDL поддерживают работу с библиотекой ieee, в состав которой входят следующие пакеты:

- ieee.std_logic_1164. Содержит определения основных типов данных.

- std_logic_arith. Содержит арифметические функции, функции преобразования и сравнения, работающие с такими типами данных как, signed, unsigned, integer, std_ulogic, std_logic, std_logic_unsigned и std_logic_vector.

- std_logic_misc. Содержит определения вспомогательных типов данных, а также подтипов, констант и функций, используемых пакетом ieee.std_logic_1164.

____Чтобы задействовать любой из этих пакетов, нужно включить в состав проекта операторы объявления требуемых библиотек и пакетов, вида:

____Очень популярной библиотекой также является библиотека SYNOPSYS, которая содержит пакет SYNOPSYS.attributes.all с описаниями атрибутов:

library SYNOPSYS;

use SYNOPSYS.attributes.all;

____Разработчик цифрового устройства может создать и затем подключить к проекту собственный пакет. Объявление пакета должно удовлетворять следующему синтаксису:

Например, базовые логические функции and2, or2, nand2, nor2, xor2 и т. д. необходимо предварительно определить как компоненты, прежде чем их можно будет использовать в этом качестве в разрабатываемом проекте. Определить базовые логические функции в качестве компонентов можно, например, в пакете с именем basic_func таким образом:

____Здесь следует обратить внимание на то, что в интерфейсе пакета в подразделе component указано время задержки 5нс (delay: time := 5 ns). Следует заметить, что явное указание времени задержки игнорируется многими инструментальными средствами синтеза. В конструкции разрабатываемого пакета использован встроенный тип std_logic, который объявлен в пакете std_logic_1164. Для достижения видимости описания типа std_logic из разрабатываемого пакета в него включены операторы

library ieee;

и

use ieee.std_logic_1164.all;

____Созданный пакет должен быть откомпилирован и помещён в пользовательскую библиотеку. Такую библиотеку можно именовать как my_func, в создаваемом проекте требуется подключить эту библиотеку my_func и пакет basic_func с помощью операторов следующего вида:

Внимание! Язык VHDL допускает перечисление имён библиотек и пакетов после ключевых слов library и use соответственно, разделяя их запятыми. Естественно, что можно объявлять в создаваемом проекте библиотеки и пакеты с помощью отдельных операторов, как показано на следующем листинге.

.

Последний раз редактировалось: Viktor2312 (Сб Май 04 2019, 17:46), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Re: Конспект-1__VHDL

Re: Конспект-1__VHDL

3

.

____Идентификаторы (identifiers) - это определяемые пользователем слова, используемые для обозначения программных объектов (проектов, интерфейсов, архитектур, пакетов, сигналов, переменных, констант, компонентов и др.) в VHDL-проектах. Выше уже приводились примеры идентификаторов для входных и выходных сигналов, а также для объявлений интерфейсов и архитектур проектов. При выборе идентификаторов следует соблюдать следующие правила:

____Примеры корректных идентификаторов: X10, x_10, My_gate1.

____Примеры некорректных идентификаторов: _X10, my_gate@input, gate-input.

____Идентификаторы, создаваемые по приведённым выше правила, называют базовыми идентификаторами (baze identifier). Однако эти правила часто слишком ограничивают разработчиков, не позволяя создавать имена сигналов с особыми свойствами. Например, если в VHDL-проекте требуется обозначить сигнал RESET с активным низким уровнем, проще всего использовать идентификатор \RESET. Ограничения, наложенные на базовые идентификаторы, сняты в группе так называемых расширенных идентификаторов (extended identifier). К расширенным идентификаторам применяются все те же правила, что и для базовых, но с учётом следующих особенностей:

____Расширенные идентификаторы поддерживаются только в версии языка VHDL-93. В версии VHDL-87 они отсутствуют.

____Примеры корректного оформления расширенных идентификаторов: Input, \Input\, \input#1\, \Rst\\as\.

____Некоторые идентификаторы используются системой проектирования как ключевые слова (keyword) для организации особых, специфических конструкций языка (операторов языка). Эти ключевые слова не могут применяться как идентификаторы для сигналов или объектов, которые мы определяем в создаваемом проекте. Некоторые из этих ключевых слов приводились ранее: in, out, or, and, port, map, end и т. д. Ключевые слова часто выделяются САПР VHDL полужирным шрифтом или цветом. Полный список ключевых слов языка VHDL:

abs

access

after

alias

all

and

architecture

array

assert

attribute

begin

block

body

buffer

bus

case

component

cofiguration

constant

disconnect

downto

else

elsif

end

entity

exit

file

for

function

generate

generic

group

guarded

if

impure

in

inertial

inout

is

label

library

linkage

literal

loop

map

mod

mand

new

next

nor

not

null

of

on

open

or

others

out

package

port

postponed

procedure

process

pure

range

record

register

reject

rem

report

return

rol

ror

select

severity

signal

shared

sla

sll

sra

srl

subtype

then

to

transport

type

unaffected

units

until

use

variable

wait

when

while

with

xnor

xor

____Некоторые идентификаторы являются в конкретных САПР VHDL зарезервированными. Зарезервированные идентификаторы используются для указания информационных характеристик (типов) программных объектов в операторах их объявлений. В частности, зарезервированными идентификаторами являются такие идентификаторы, как bit, bit_vector, std_logic_vector и т. д. Зарезервированные идентификаторы запрещено применять в качестве базовых идентификаторов.

____Стандарт VHDL-87 поддерживает следующие зарезервированные слова: bit, bit_vector, integer, float, string, character.

____Стандарт VHDL-93 дополняет этот перечень следующими зарезервированными идентификаторами: std_logic, std_logic_vector, std_logic_signed, std_logic_unsigned.

____По умолчанию числа, или числовые литералы, в языке VHDL представляются в десятичной системе счисления. Язык VHDL поддерживает работу с целочисленными (integer) и действительными (real) литералами. Целочисленный литерал состоит из целого числа без десятичной точки, действительный литерал всегда содержит десятичную точку. Экспоненциальное представление как целый, так и действительных чисел поддерживается путём использования символов "Е" или "е". Для целочисленных литералов экспонента должна быть положительным числом.

____Примеры целочисленных литералов: 13, 11, 512Е3, 13е+6.

____Примеры вещественных литералов: 2.4, 512.23, 3.14е-2.

____Число -12 является комбинацией операции минус и целочисленного литерала.

____Язык VHDL также поддерживает работу с числами других систем счисления. Такие числа принято называть базированными литералами. Синтаксис представления базированных литералов имеет вид:

база#число#.

____

Лексические элементы языка VHDL.

Идентификаторы.

____Идентификаторы (identifiers) - это определяемые пользователем слова, используемые для обозначения программных объектов (проектов, интерфейсов, архитектур, пакетов, сигналов, переменных, констант, компонентов и др.) в VHDL-проектах. Выше уже приводились примеры идентификаторов для входных и выходных сигналов, а также для объявлений интерфейсов и архитектур проектов. При выборе идентификаторов следует соблюдать следующие правила:

- Идентификатор может содержать прописные и (или) строчные символы латинского алфавита и цифры (A...Z, a...z, 0...9)разделяемые одним символом подчёркивания.

- Первым символом в идентификаторе должен быть символ латинского алфавита. Символ подчёркивания не может быть первым или последним символом идентификатора.

- Использовать подряд два символа подчёркивания в идентификаторе запрещается.

- Строчные и прописные символы латинского алфавита в идентификаторе считаются одинаковыми, т. е. идентификаторы And2, AND2 или and2 равнозначны. Другими словами, идентификаторы не чувствительны к регистру символов.

- Идентификатор может иметь любую длину.

____Примеры корректных идентификаторов: X10, x_10, My_gate1.

____Примеры некорректных идентификаторов: _X10, my_gate@input, gate-input.

____Идентификаторы, создаваемые по приведённым выше правила, называют базовыми идентификаторами (baze identifier). Однако эти правила часто слишком ограничивают разработчиков, не позволяя создавать имена сигналов с особыми свойствами. Например, если в VHDL-проекте требуется обозначить сигнал RESET с активным низким уровнем, проще всего использовать идентификатор \RESET. Ограничения, наложенные на базовые идентификаторы, сняты в группе так называемых расширенных идентификаторов (extended identifier). К расширенным идентификаторам применяются все те же правила, что и для базовых, но с учётом следующих особенностей:

- Расширенные идентификаторы могут начинаться и заканчиваться символом обратной косой черты "\".

- Расширенные идентификаторы должны отличаться от зарезервированных слов, ключевых слов и любых других базовых идентификаторов. Например, можно использовать расширенный идентификатор \if, который не будет восприниматься компилятором в качестве ключевого слова if.

- Внутри расширенного идентификатора также может содержаться символ косой обратной черты. В такой ситуации он должен предваряться дополнительным символом обратной косой черты, т. е. данных символа внутри расширенного идентификатора должно быть два.

____Расширенные идентификаторы поддерживаются только в версии языка VHDL-93. В версии VHDL-87 они отсутствуют.

____Примеры корректного оформления расширенных идентификаторов: Input, \Input\, \input#1\, \Rst\\as\.

Ключевые слова.

____Некоторые идентификаторы используются системой проектирования как ключевые слова (keyword) для организации особых, специфических конструкций языка (операторов языка). Эти ключевые слова не могут применяться как идентификаторы для сигналов или объектов, которые мы определяем в создаваемом проекте. Некоторые из этих ключевых слов приводились ранее: in, out, or, and, port, map, end и т. д. Ключевые слова часто выделяются САПР VHDL полужирным шрифтом или цветом. Полный список ключевых слов языка VHDL:

abs

access

after

alias

all

and

architecture

array

assert

attribute

begin

block

body

buffer

bus

case

component

cofiguration

constant

disconnect

downto

else

elsif

end

entity

exit

file

for

function

generate

generic

group

guarded

if

impure

in

inertial

inout

is

label

library

linkage

literal

loop

map

mod

mand

new

next

nor

not

null

of

on

open

or

others

out

package

port

postponed

procedure

process

pure

range

record

register

reject

rem

report

return

rol

ror

select

severity

signal

shared

sla

sll

sra

srl

subtype

then

to

transport

type

unaffected

units

until

use

variable

wait

when

while

with

xnor

xor

Зарезервированные слова.

____Некоторые идентификаторы являются в конкретных САПР VHDL зарезервированными. Зарезервированные идентификаторы используются для указания информационных характеристик (типов) программных объектов в операторах их объявлений. В частности, зарезервированными идентификаторами являются такие идентификаторы, как bit, bit_vector, std_logic_vector и т. д. Зарезервированные идентификаторы запрещено применять в качестве базовых идентификаторов.

____Стандарт VHDL-87 поддерживает следующие зарезервированные слова: bit, bit_vector, integer, float, string, character.

____Стандарт VHDL-93 дополняет этот перечень следующими зарезервированными идентификаторами: std_logic, std_logic_vector, std_logic_signed, std_logic_unsigned.

Числа.

____По умолчанию числа, или числовые литералы, в языке VHDL представляются в десятичной системе счисления. Язык VHDL поддерживает работу с целочисленными (integer) и действительными (real) литералами. Целочисленный литерал состоит из целого числа без десятичной точки, действительный литерал всегда содержит десятичную точку. Экспоненциальное представление как целый, так и действительных чисел поддерживается путём использования символов "Е" или "е". Для целочисленных литералов экспонента должна быть положительным числом.

____Примеры целочисленных литералов: 13, 11, 512Е3, 13е+6.

____Примеры вещественных литералов: 2.4, 512.23, 3.14е-2.

____Число -12 является комбинацией операции минус и целочисленного литерала.

____Язык VHDL также поддерживает работу с числами других систем счисления. Такие числа принято называть базированными литералами. Синтаксис представления базированных литералов имеет вид:

база#число#.

____

Последний раз редактировалось: Viktor2312 (Сб Май 04 2019, 17:26), всего редактировалось 12 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Страница 1 из 1

Права доступа к этому форуму:

Вы не можете отвечать на сообщения|

|

|