Последние темы

» Вити больше нет!автор bug19 Пн Фев 20 2023, 19:54

» Собираем оригинальный Орион 128

автор bug19 Пн Фев 20 2023, 19:47

» Проблема плющеного экрана ОРИОНА

автор kanzler Пн Ноя 28 2022, 12:05

» Орион 128 и его клоны возрождение 2019-2022 год

автор kanzler Пн Ноя 28 2022, 12:03

» Электроника КР-04. Информация, документы, фото.

автор kanzler Пн Ноя 28 2022, 12:02

» Новости форума

автор kanzler Пн Ноя 28 2022, 11:52

» Орион-128 НГМД запуск 2021 года

автор matrixplus Сб Сен 10 2022, 17:36

» ПЗУ F800 для РК86

автор ведущий_специалист Сб Сен 10 2022, 10:37

» Микропроцессорная лаборатория "Микролаб К580ИК80", УМК-80, УМПК-80 и др.

автор Электротехник Вт Июл 26 2022, 19:33

» Орион-128 SD карта в Орионе

автор matrixplus Чт Июн 02 2022, 09:00

» 7 Мая. День Радио!

автор Viktor2312 Чт Май 12 2022, 10:58

» Серия: Массовая радио библиотека. МРБ

автор Viktor2312 Ср Май 11 2022, 12:17

» Полезные книги

автор Viktor2312 Пн Май 09 2022, 15:07

» Орион 128 Стандарты портов и системной шины Х2

автор matrixplus Вс Май 08 2022, 23:08

» Орион-128 и Орион ПРО еще раз про блоки питания

автор matrixplus Вс Май 08 2022, 19:09

» Орион-128 Программаторы

автор matrixplus Вс Май 08 2022, 19:02

» Орион ПРО история сборки 2021 до 2022

автор matrixplus Вс Май 08 2022, 18:47

» Анонсы монет (New coin).

автор Viktor2312 Сб Май 07 2022, 23:11

» Хочу свой усилок для квартиры собрать не спеша

автор Viktor2312 Сб Май 07 2022, 19:33

» Амфитон 25у-002С

автор Viktor2312 Сб Май 07 2022, 09:38

» Майнер: T-Rex

автор Viktor2312 Вс Май 01 2022, 09:12

» GoWin. Изучение документации. SUG100-2.6E_Gowin Software User Guide. Среда разработки EDA.

автор Viktor2312 Пн Апр 25 2022, 01:01

» GoWin. Изучение документации. UG286-1.9.1E Gowin Clock User Guide.

автор Viktor2312 Сб Апр 23 2022, 18:22

» GoWin. Documentation Database. Device. GW2A.

автор Viktor2312 Ср Апр 20 2022, 14:08

» GOWIN AEC IP

автор Viktor2312 Ср Апр 20 2022, 12:08

Самые активные пользователи за месяц

| Нет пользователей |

Поиск

Микросхемы ПЛИС семейства Spartan-3A

Страница 1 из 1 • Поделиться

Микросхемы ПЛИС семейства Spartan-3A

Микросхемы ПЛИС семейства Spartan-3A

1

Spartan-3A

Чувствую впереди будет, что-то такое:

- Спойлер:

- 1. https://cloud.mail.ru/public/ewdA/8YZqhQW5u

2.

...

Последний раз редактировалось: Viktor2312 (Пн Дек 06 2021, 04:50), всего редактировалось 2 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

2

Документация.

Решил, что нужно сохранить, пока оно есть и доступно, а то знаем, проходили уже, как производители убирают документацию и другую информацию на семейства, которые они считают устаревшими. К тому же похоже, что скоро это всё сильно мне потребуется...

Data Sheets (Спецификация)

DS529 - Spartan-3A FPGA Family Data Sheet (v2.1)

Dec 18, 2018

Document Type: Data Sheets

Includes the overview, specifications, and pinouts for the Spartan-3A FPGA family.

(Включает обзор, спецификации и распиновку для семейства Spartan-3A FPGA.)

Скачать

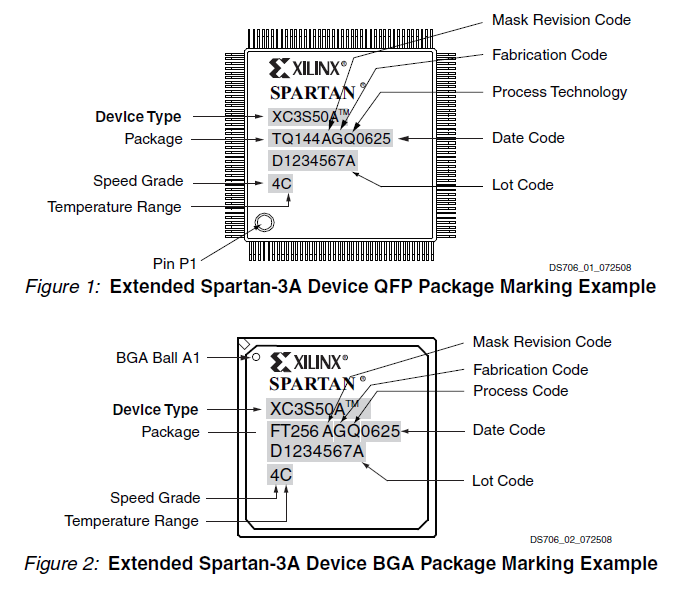

DS706 - Extended Spartan-3A Family Overview (v1.1)

Feb 03, 2011

Document Type: Data Sheets

This document introduces the Extended Spartan-3A family of FPGAs. It provides features, a device summary, functional overview, packaging options, and ordering information for the device family.

(Этот документ знакомит с семейством ПЛИС Extended Spartan-3A. В нем представлены функции, краткое описание устройства, функциональный обзор, варианты упаковки и информация для заказа для данного семейства устройств.)

Скачать

Spartan-3A/3AN Starter Kit Schematics (v1.0.2)

Aug 21, 2007

Document Type: Data Sheets,Board Files

Spartan-3A/3AN FPGA Starter Kit board schematics.

(Схема платы стартового комплекта Spartan-3A/3AN FPGA.)

Скачать

DS610 - Spartan-3A DSP FPGA Family: Complete Data Sheet (v3.0)

Oct 04, 2010

Document Type: Data Sheets

The Spartan-3A DSP family of Field-Programmable Gate Arrays (FPGAs) solves the design challenges in most high-volume, cost-sensitive, high-performance DSP applications.

(Семейство программируемых вентильных матриц (ПЛИС) Spartan-3A DSP решает проблемы проектирования в большинстве высокопроизводительных, дорогостоящих и высокопроизводительных DSP-приложений большого объема.)

Скачать

DS681 - XA Spartan-3A Automotive FPGA Family Data Sheet (v2.1)

Feb 05, 2021

Document Type: Data Sheets

The Xilinx Automotive (XA) Spartan-3A family of FPGAs solves the design challenges in most high-volume, cost-sensitive, I/O-intensive automotive electronics applications.

(Семейство ПЛИС Xilinx Automotive (XA) Spartan-3A решает проблемы проектирования в большинстве крупных, дорогостоящих и требовательных к вводу-выводу приложений автомобильной электроники.)

Скачать

DS705 - XA Spartan-3A DSP Automotive FPGA Family Data Sheet (v2.0)

Apr 18, 2011

Document Type: Data Sheets

The Xilinx Automotive (XA) Spartan-3A DSP family of FPGAs solves the design challenges in most high-volume, cost-sensitive, high-performance DSP automotive applications. The XA Spartan-3A DSP family includes hardened DSP MACs with pre-adders, providing significant increases in the throughput and performance of this low-cost family.

(Семейство ПЛИС Xilinx Automotive (XA) Spartan-3A DSP решает проблемы проектирования в большинстве крупных, дорогостоящих и высокопроизводительных автомобильных приложений DSP. Семейство DSP XA Spartan-3A включает усиленные MAC-адреса DSP с предварительными сумматорами, обеспечивающие значительное увеличение пропускной способности и производительности этого недорогого семейства.)

Скачать

UG334 - Spartan-3A/3AN FPGA Starter Kit Board User Guide (v1.1)

Jun 19, 2008

Document Type: Data Sheets

This user guide describes the components and operation of the Spartan-3A/3AN FPGA Starter Kit Board, for Revision D. The Starter Kit provides a low-cost, easy-to-use development and evaluation platform for Spartan-3A/3AN FPGA designs.

(В этом руководстве пользователя описываются компоненты и работа платы стартового комплекта Spartan-3A/3AN FPGA для версии D. Стартовый комплект представляет собой недорогую, простую в использовании платформу разработки и оценки для Spartan-3A/3AN FPGA. конструкции.)

Скачать

UG330 - Spartan-3A Starter Kit Board User Guide for Revision C Board (v1.3)

Jun 21, 2007

Document Type: Data Sheets

Describes the original Revision C Spartan-3A FPGA Starter Kit Board. See UG334 for the Revision D board.

(Описывает исходную плату стартового набора Spartan-3A FPGA Revision C. См. UG334 для платы Revision D)

Скачать

Extended Spartan-3A Family CLKFX Jitter Calculator (v1.0.6)

Sep 16, 2010

Document Type: Data Sheets

Excel file to calculate DFS output jitter based on input and output clock frequencies. Applies to Spartan-3A, Spartan-3AN, and Spartan-3A DSP platforms.

(Файл Excel для расчета выходного джиттера DFS на основе входных и выходных тактовых частот. Применимо к платформам DSP Spartan-3A, Spartan-3AN и Spartan-3A.)

Скачать

Extended Spartan-3A Family ASCII Pinouts and Excel Footprints (v1.3)

Jan 09, 2009

Document Type: Data Sheets

Comma-delimited ASCII text files and Excel footprints for each package type in the Extended Spartan-3A Family (Spartan-3A, Spartan-3AN, and Spartan-3A DSP platforms).

(Текстовые файлы ASCII с разделителями-запятыми и посадочные места Excel для каждого типа пакета в расширенном семействе Spartan-3A (платформы Spartan-3A, Spartan-3AN и Spartan-3A DSP).)

Скачать

Spartan-3A DSP FPGA Pinouts and Excel Footprints (v1.2)

Jun 02, 2008

Document Type: Data Sheets

Comma-delimited ASCII text files and Excel footprints for each package type.

(Текстовые файлы ASCII с разделителями-запятыми и посадочные места Excel для каждого типа пакета.)

Скачать

DS557 - Spartan-3AN FPGA Family Data Sheet (v4.3)

Jan 10, 2019

Document Type: Data Sheets

Includes the overview, specifications, and pinouts for the Spartan-3AN FPGA family.

(Включает обзор, спецификации и распиновку для семейства Spartan-3AN FPGA.)

Скачать

DS698 - XPS InSystem Flash (v1.01b) (v1.3)

Sep 16, 2009

Document Type: Data Sheets

The InSystem Flash (ISF) is a type of serial flash memory and it is present only on Spartan-3AN devices. The Spartan-3AN FPGA family is the sub-family of Spartan-3A FPGA devices.

(InSystem Flash (ISF) - это тип последовательной флэш-памяти, которая присутствует только на устройствах Spartan-3AN. Семейство ПЛИС Spartan-3AN - это подсемейство устройств ПЛИС Spartan-3A.)

Скачать

DS569 - XPS General Purpose Input/Output (GPIO) (v2.00a) Data Sheet (v2.0)

Dec 02, 2009

Document Type: Data Sheets

This document describes the specifications for the General Purpose Input/Output (GPIO) core for the Processor Local Bus (PLB). The XPS GPIO is a 32-bit peripheral that attaches to the PLBv4.6.

(В этом документе описываются спецификации ядра ввода/вывода общего назначения (GPIO) для локальной шины процессора (PLB). XPS GPIO - это 32-разрядное периферийное устройство, которое подключается к PLBv4.6.)

Скачать

DS588 - XPS Delta-Sigma Digital to Analog Converter (v1.01a) Data Sheet (v1.9)

Dec 02, 2009

Document Type: Data Sheets

The digital to analog converter (DAC) converts a binary number into a voltage directly proportional to the value of the binary number. A variety of applications use DAC including waveform generators and programmable voltage sources.

(Цифро-аналоговый преобразователь (ЦАП) преобразует двоичное число в напряжение, прямо пропорциональное значению двоичного числа. В различных приложениях используется ЦАП, включая генераторы сигналов и программируемые источники напряжения.)

Скачать

DS583 - XPS SYSACE (System ACE) Interface Controller (v1.01a) Data Sheet (v2.0)

Dec 02, 2009

Document Type: Data Sheets

The XPS System ACE Interface Controller (or, interchangeably, the XPS SYSACE) is the interface between the Processor Local Bus (PLB) and the Microprocessor Interface (MPU) of the System ACE Compact Flash solution peripheral. This module attaches to the PLB.

(Контроллер интерфейса XPS System ACE (или, взаимозаменяемо, XPS SYSACE) - это интерфейс между локальной шиной процессора (PLB) и интерфейсом микропроцессора (MPU) периферийного устройства решения System ACE Compact Flash. Этот модуль подключается к PLB.)

Скачать

DS313 - Spartan-3L Low Power FPGA Family (v1.2)

Apr 18, 2008

Document Type: Data Sheets

Low-power Spartan-3L data sheet. Explains how the Spartan-3L family is different from the Spartan-3 family. Note that this family is being discontinued. For specifications and other information common to both families, see the standard Spartan-3 data sheet.

(Паспорт мало потребляющего Spartan-3L. Объясняет, чем семейство Spartan-3L отличается от семейства Spartan-3. Обратите внимание, что это семейство больше не выпускается. Технические характеристики и другую информацию, общую для обоих семейств, см. В стандартном техническом описании Spartan-3.)

Скачать

DS573 - LogiCORE IP XPS Timer/Counter (v1.02a) Data Sheet (v2.0)

Apr 19, 2010

Document Type: Data Sheets

This document describes the specifications for a XPS Timer/Counter core for the Processor Local Bus.

(В этом документе описываются спецификации ядра таймера/счетчика XPS для локальной шины процессора.)

Скачать

DS571 - XPS UART Lite (v1.02a) Data Sheet (v1.8 )

Jun 22, 2011

Document Type: Data Sheets

The XPS Universal Asynchronous Receiver Transmitter (UART) Lite Interface connects to the PLB (Processor Local Bus) and provides the controller interface for asynchronous serial data transfer. This soft IP core is designed to interface with the PLBV46.

(Облегченный интерфейс универсального асинхронного приемного передатчика (UART) XPS подключается к PLB (локальной шине процессора) и обеспечивает интерфейс контроллера для асинхронной последовательной передачи данных. Это программное ядро IP предназначено для взаимодействия с PLBV46.)

Скачать

DS587 - XPS Delta-Sigma Analog to Digital Converter (ADC) (v1.01a) (v2.2)

Dec 02, 2009

Document Type: Data Sheets

When digital systems are used in real-world applications, it is often necessary to convert an analog voltage level to a binary number. The value of this number is directly or inversely proportional to the voltage. The analog to digital conversion is realized in the XPS Delta-Sigma ADC (XPS ADC) using Delta-Sigma conversion technique. This soft IP core isdesigned to interface with the PLB (Processor Local Bus).

(Когда цифровые системы используются в реальных приложениях, часто необходимо преобразовать аналоговый уровень напряжения в двоичное число. Значение этого числа прямо или обратно пропорционально напряжению. Аналого-цифровое преобразование реализовано в дельта-сигма-АЦП XPS (XPS ADC) с использованием техники дельта-сигма-преобразования. Это программное ядро IP предназначено для взаимодействия с PLB (локальной шиной процессора). )

Скачать

DS582 - LogiCORE IP XPS Timebase Watchdog Timer (v1.02a) Data Sheet (v1.3)

Jul 23, 2010

Document Type: Data Sheets

The XPS Timebase Watchdog Timer Interface is a 32-bit peripheral that provides a 32-bit free-running timebase and watchdog timer.

(Интерфейс сторожевого таймера XPS Timebase - это 32-битное периферийное устройство, которое обеспечивает 32-битную автономную временную развертку и сторожевой таймер.)

Скачать

DS581 - XPS External Peripheral Controller (EPC) v1.02a (v2.0)

Sep 16, 2009

Document Type: Data Sheets

This is the data sheet for the XPS External Peripheral Controller (EPC) v1.02a core.

(Это лист данных для ядра внешнего периферийного контроллера XPS (EPC) v1.02a.)

Скачать

DS570 - LogiCORE IP XPS Serial Peripheral Interface (SPI) (v2.02a) Data Sheet (v2.7)

Jun 22, 2011

Document Type: Data Sheets

The XPS Serial Peripheral Interface (SPI) connects to the PLB V4.6 (Processor Local Bus with Xilinx simplifications) and provides a serial interface to SPI devices such as SPI EEPROMs and SPI serial flash devices.

(Последовательный периферийный интерфейс XPS (SPI) подключается к PLB V4.6 (локальная шина процессора с упрощениями Xilinx) и обеспечивает последовательный интерфейс для устройств SPI, таких как SPI EEPROM и последовательные флэш-устройства SPI.)

Скачать

DS579 - LogiCORE IP XPS Central DMA Controller (v2.03a) Data Sheet (v3.4)

Dec 14, 2010

Document Type: Data Sheets

The XPS Central DMA Controller provides simple Direct Memory Access (DMA) services to peripherals and memory devices on the PLB. The controller transfers a programmable quantity of data from a source address to a destination address without processor intervention.

(Центральный контроллер DMA XPS обеспечивает простой прямой доступ к памяти (DMA), (ПДП) для периферийных устройств и устройств памяти на PLB. Контроллер передает программируемое количество данных с адреса источника на адрес назначения без вмешательства процессора.)

Скачать

DS572 - LogiCORE IP XPS Interrupt Controller (v2.01a) Data Sheet (v2.6)

Apr 19, 2010

Document Type: Data Sheets

The XPS Interrupt Controller (XPS INTC) concentrates multiple interrupt inputs from peripheral devices to a single interrupt output to the system processor. The registers for checking, enabling and acknowledging interrupts are accessed through a slave interface for the Processor Local Bus (PLB V4.6). The number of interrupts and other aspects can be tailored to the target system.

(Контроллер прерываний XPS (XPS INTC) концентрирует несколько входных прерываний от периферийных устройств к одному выходу прерывания для системного процессора. Доступ к регистрам для проверки, разрешения и подтверждения прерываний осуществляется через подчиненный интерфейс локальной шины процессора (PLB V4.6). Количество прерываний и другие аспекты могут быть адаптированы к целевой системе.)

Скачать

DS707 - LogiCORE IP XPS PS2 Controller (v1.01b) (v1.6)

Apr 19, 2010

Document Type: Data Sheets

The LogiCORE IP XPS PS2 Controller is a PLB (Processor Local Bus) slave that is designed to control PS2 devices such as keyboard and mouse. The PS2 protocol is a simple bidirectional serial protocol.

(Контроллер LogiCORE IP XPS PS2 - это подчиненное устройство PLB (локальная шина процессора), предназначенное для управления устройствами PS2, такими как клавиатура и мышь. Протокол PS2 - это простой двунаправленный последовательный протокол.)

Скачать

DS575 - LogiCORE IP XPS Multi-CHannel External Memory Controller (XPS MCH EMC) (v3.01a) Data Sheet (v1.8 )

Jun 22, 2011

Document Type: Data Sheets

The Xilinx LogiCORE Multichannel External Memory Controller (XPS MCH EMC) provides the control interface for external synchronous, asynchronous SRAM and Flash memory devices through the MCH or PLB interfaces. It is assumed that the reader is familiar with the PLB and MCH protocol.

(Многоканальный контроллер внешней памяти Xilinx LogiCORE (XPS MCH EMC) обеспечивает интерфейс управления для внешних синхронных, асинхронных устройств SRAM и флэш-памяти через интерфейсы MCH или PLB. Предполагается, что читатель знаком с протоколами PLB и MCH.)

Скачать

DS577 - XPS 16550 UART (v3.00a) Data Sheet (v2.0)

Sep 16, 2009

Document Type: Data Sheets

This is the data sheet for the XPS 16550 UART (v3.00a) core.

(Это лист данных для ядра XPS 16550 UART (v3.00a). )

Скачать

DS206 - LogiCORE IP 32-Bit Initiator/Target v3 & v4 for PCI Data Sheet (v14.1)

Oct 16, 2012

Document Type: Data Sheets

The Initiator/Target core for PCI is a pre-implemented and fully tested module for Xilinx FPGAs. The pinout for each device and the relative placement of the internal logic are pre-defined.

(Инициатор/целевое ядро для PCI - это предварительно реализованный и полностью протестированный модуль для ПЛИС Xilinx. Распиновка для каждого устройства и относительное размещение внутренней логики предварительно определены.)

Скачать

DS205 - LogiCORE IP 64-Bit Initiator/Target v3 & v4 for PCI Data Sheet (v15.1)

Oct 16, 2012

Document Type: Data Sheets

The 64-Bit Initiator/Target Core v3 and v4 for PCI is a pre-implemented and fully tested module for Xilinx FPGAs. The pinout for each device and the relative placement of the internal logic are predefined.

(64-битный инициатор/целевое ядро v3 и v4 для PCI - это предварительно реализованный и полностью протестированный модуль для ПЛИС Xilinx. Распиновка для каждого устройства и относительное размещение внутренней логики предопределены.)

Скачать

DS299 - LogiCORE IP ChipScope Pro Integrated Logic Analyzer (ILA) (1.04a) Data Sheet (v3.2)

Jun 22, 2011

Document Type: Data Sheets

The ChipScope Pro Integrated Logic Analyzer (ILA) core is a customizable logic analyzer core that can be used to monitor any internal signal of your design. The ILA core includes many advanced features of modern logic analyzers, including boolean trigger equations, trigger sequences, and storage qualification.

(Ядро интегрированного логического анализатора (ILA) ChipScope Pro - это настраиваемое ядро логического анализатора, которое можно использовать для мониторинга любого внутреннего сигнала вашей конструкции. Ядро ILA включает в себя множество расширенных функций современных логических анализаторов, включая логические уравнения запуска, последовательности запуска и квалификацию хранилища.)

Скачать

DS646 - LogiCORE IP ChipScope Pro Integrated Controller ( ICON) (v1.05a) Data Sheet (v2.2)

Jun 22, 2011

Document Type: Data Sheets

The LogiCORE IP ChipScope Pro Integrated CONtroller core (ICON) provides an interface between the JTAG Boundary Scan (BSCAN) interface of the FPGA device and the ChipScope Pro cores.

(Ядро интегрированного контроллера LogiCORE IP ChipScope Pro (ICON) обеспечивает интерфейс между интерфейсом JTAG Boundary Scan (BSCAN) устройства FPGA и ядрами ChipScope Pro.)

Скачать

DS444 - IP Processor Block RAM (BRAM) Block (v1.00a) Data Sheet (v2.3)

Mar 01, 2011

Document Type: Data Sheets

The BRAM Block is a configurable memory module that attaches to a variety of BRAM Interface Controllers.

(Блок BRAM - это настраиваемый модуль памяти, который подключается к различным контроллерам интерфейса BRAM.)

Скачать

DS618 - LogiCORE IP PLBv46 to PLBv46 Bridge (v1.04a) Data Sheet (v1.7)

Mar 01, 2011

Document Type: Data Sheets

The PLBv46 (Processor Local Bus Version 4.6 with Xilinx simplification) to PLBv46 Bridge allows the designer to connect two PLB buses. The PLBv46 to PLBv46 Bridge can be used to isolate the slow PLB peripherals from the primary PLB and improve the system performance.

(PLBv46 (локальная шина процессора версии 4.6 с упрощением Xilinx) к мосту PLBv46 позволяет проектировщику подключать две шины PLB. Мост PLBv46 - PLBv46 можно использовать для изоляции медленных периферийных устройств PLB от основного PLB и повышения производительности системы.)

Скачать

DS537 - XPS LL TEMAC (v2.03a) Data Sheet (v2.6)

Dec 14, 2010

Document Type: Data Sheets

This document provides the design specification for the XPS_LL_TEMAC soft Ethernet core.

(Этот документ предоставляет проектную спецификацию для ядра Soft Ethernet XPS_LL_TEMAC.)

Скачать

DS483 - Utility Flip-Flop (v1.10a) Data Sheet (v1.8 )

Dec 02, 2009

Document Type: Data Sheets

The Utility Flip-Flop is a pipelining glue-logic core intended for use in a Xilinx Platform Studio (XPS) project.

(Utility Flip-Flop - это конвейерное ядро связующей логики, предназначенное для использования в проекте Xilinx Platform Studio (XPS). )

Скачать

DS631 - XPS Mutex (v1.00.c) Data Sheet (v1.5)

Jun 24, 2009

Document Type: Data Sheets

This is the data sheet for the XPS Mutex (v1.00.c) core.

(Это лист данных для ядра XPS Mutex (v1.00.c). )

Скачать

DS632 - XPS Mailbox (v2.00a) Data Sheet (v1.2)

Jun 24, 2009

Document Type: Data Sheets

This is the data sheet for the XPS Mailbox (v2.00a) core.

(Это лист данных для ядра XPS Mailbox (v2.00a). )

Скачать

DS639 - LogiCORE IP XPS Universal Bus 2.0 Device (v7.01a) Data Sheet (v3.4)

Oct 16, 2012

Document Type: Data Sheets

The Xilinx Universal Serial Bus 2.0 High Speed Device with Processor Local Bus (PLBv4.6) enables USB connectivity to the user’s design with a minimal amount of resources. This interface is suitable for USB-centric, high-performance designs, bridges, and legacy port replacement operations.

(Высокоскоростное устройство Xilinx Universal Serial Bus 2.0 с процессорной локальной шиной (PLBv4.6) обеспечивает возможность USB-подключения к пользовательскому дизайну с минимальным объемом ресурсов. Этот интерфейс подходит для высокопроизводительных проектов, связанных с USB, мостов и операций по замене устаревших портов.)

Скачать

DS482 - Utility Reduced Logic (v1.00a) Data Sheet (v1.6)

Dec 02, 2009

Document Type: Data Sheets

The Utility Reduced Logic core applies a logic reduction function over an input vector to generate a single bit result. The core is intended as glue logic between peripherals.

(Ядро Utility Reduced Logic применяет функцию сокращения логики к входному вектору для генерации однобитового результата. Ядро предназначено как связующее звено между периферийными устройствами.)

Скачать

DS694 - Utility IO Multiplexer (v1.00a) Data Sheet (v1.2)

Dec 02, 2009

Document Type: Data Sheets

The Utility IO Multiplexer module provides a multiplexing function between two IO vectors to one IO vector.

(Модуль Utility IO Multiplexer обеспечивает функцию мультиплексирования между двумя векторами ввода-вывода в один вектор ввода-вывода.)

Скачать

DS565 - PLBV46 Master Burst (v1.01a) Data Sheet (v2.0)

Dec 14, 2010

Document Type: Data Sheets

The PLBV46 Master Burst is a continuation of the Xilinx family of IBM CoreConnect compatible LogiCORE products. It provides a bi-directional interface between a User IP core and the PLB v4.6 bus standard. This version of the PLBV46 Master Burst has been designed for PLBV46 Master operations consisting of single data beat read or write transfers and Fixed Length Burst Transfers of 2 to 16 data beats.

(PLBV46 Master Burst является продолжением семейства Xilinx продуктов LogiCORE, совместимых с IBM CoreConnect. Он обеспечивает двунаправленный интерфейс между ядром User IP и стандартом шины PLB v4.6. Эта версия PLBV46 Master Burst была разработана для основных операций PLBV46, состоящих из однократных операций чтения или записи данных и пакетных передач фиксированной длины от 2 до 16 битов данных.)

Скачать

DS606 - LogiCORE IP XPS IIC Bus Interface (v2.03a) Data Sheet (v1.11)

Jun 22, 2011

Document Type: Data Sheets

This product specification defines the architecture, hardware (signal) interface, software (register) interface and parameterization options for the XPS IIC module. It provides a low speed, two wire, serial bus interface to a large number of popular devices.

(Эта спецификация продукта определяет архитектуру, аппаратный (сигнальный) интерфейс, программный (регистрационный) интерфейс и варианты параметризации для модуля XPS IIC. Он обеспечивает низкоскоростной двухпроводной интерфейс последовательной шины для большого количества популярных устройств.)

Скачать

DS580 - LogiCORE IP XPS Ethernet Lite Media Access Controller Data Sheet (v2.2)

Sep 21, 2010

Document Type: Data Sheets

This is the data sheet for the XPS Ethernet Lite Media Access Controller (v4.00a) core.

(Это лист данных для ядра XPS Ethernet Lite Media Access Controller (v4.00a). )

Скачать

DS643 - LogiCORE IP Multi-Port Memory Controller (v6.06.a) Data Sheet (v3.2)

Feb 22, 2013

Document Type: Data Sheets

The LogiCORE IP Multi-Port Memory Controller is a fully parameterizable memory controller that supports SDRAM/DDR/DDR2/DDR3/LPDDR memory.

(Многопортовый контроллер памяти LogiCORE IP - это полностью параметризуемый контроллер памяти, который поддерживает память SDRAM/DDR/DDR2/DDR3/LPDDR.)

Скачать

DS484 - Utility Bus Split (v1.00a) Data Sheet (v1.6)

Dec 02, 2009

Document Type: Data Sheets

The Utility Bus Split core splits a bus into smaller buses using the Xilinx Platform Studio (XPS). The core splits one input bus into two output buses which serve as glue logic between peripherals.

(Ядро с разделением служебной шины разделяет шину на меньшие шины с помощью Xilinx Platform Studio (XPS). Ядро разделяет одну входную шину на две выходные шины, которые служат связующим звеном между периферийными устройствами.)

Скачать

DS481 - Utility Vector Logic (v1.00a) Data Sheet (v1.6)

Dec 02, 2009

Document Type: Data Sheets

The Utility Vector Logic core takes two vector operands and bit wise applies a logic function to generate a single vector result. This core is intended as glue logic between peripherals.

(Ядро Utility Vector Logic принимает два векторных операнда и побитово применяет логическую функцию для генерации одного векторного результата. Это ядро задумано как связующее звено между периферийными устройствами.)

Скачать

DS323 - LogiCORE IP Ethernet Statistics v3.5 Data Sheet (v2.6)

Mar 01, 2011

Document Type: Data Sheets

The LogiCORE IP Ethernet Statistics core provides a user-configurable collection of statistical counters that can be used to gather network traffic statistics for Xilinx Ethernet Media Access Controller (MAC) products.

(Ядро LogiCORE IP Ethernet Statistics предоставляет настраиваемый пользователем набор статистических счетчиков, которые можно использовать для сбора статистики сетевого трафика для продуктов Xilinx Ethernet Media Access Controller (MAC). )

Скачать

DS695 - XPS Thin Film Transistor (TFT) Controller (v2.00a) (v1.3)

Sep 16, 2009

Document Type: Data Sheets

The XPS Thin Film Transistor (TFT) controller is a hardware display controller IP core capable of displaying 256k colors. The XPS TFT controller connects as a master on the PLB V4.6 (Processor Local Bus with Xilinx simplification) and reads the video pixel data from PLB attached video memory.

(Контроллер XPS на тонкопленочных транзисторах (TFT) представляет собой IP-ядро аппаратного контроллера дисплея, способное отображать 256 тыс. Цветов. Контроллер XPS TFT подключается в качестве ведущего к PLB V4.6 (локальная шина процессора с упрощением Xilinx) и считывает данные пикселей видео из подключенной видеопамяти PLB.)

Скачать

DS282 - ChipScope OPB IBA (Bus Analyzer) Data Sheet (v6.1)

Jun 24, 2009

Document Type: Data Sheets

The ChipScope OPB IBA core is a specialized Bus Analyzer core designed to debug embedded systems containing the IBM CoreConnect On-Chip Peripheral Bus (OPB).

(Ядро ChipScope OPB IBA - это специализированное ядро анализатора шины, предназначенное для отладки встроенных систем, содержащих периферийную шину IBM CoreConnect On-Chip Peripheral Bus (OPB). )

Скачать

DS604 - 3GPP2 Turbo Encoder v2.0 Data Sheet (v2.5)

Apr 02, 2007

Document Type: Data Sheets

This is the data sheet for 3GPP2 Turbo Encoder v2.0

(Это лист данных для 3GPP2 Turbo Encoder v2.0. )

Скачать

DS449 - LogiCORE IP Fast Simplex Link (FSL) Bus (v2.11f) Data Sheet (v2.5)

Dec 18, 2012

Document Type: Data Sheets

The LogiCORE IP FSL V20 Fast Simplex Link (FSL) Bus is a uni-directional point-to-point communication channel bus used to perform fast communication between any two design elements on the FPGA when implementing an interface to the FSL bus. The FSL interface is available on the Xilinx MicroBlaze processor.

(Шина Fast Simplex Link (FSL) LogiCORE IP FSL V20 - это однонаправленная шина канала связи точка-точка, используемая для быстрой связи между любыми двумя элементами конструкции на ПЛИС при реализации интерфейса с шиной FSL. Интерфейс FSL доступен на процессоре Xilinx MicroBlaze.)

Скачать

DS619 - ChipScope PLBv46 IBA (Bus Analyzer) Data Sheet (v3.0)

Apr 07, 2009

Document Type: Data Sheets

The ChipScope PLB Integrated Bus Analyzer (IBA) core is a specialized bus analyzer core designed to debug embedded systems that contain the IBM CoreConnect Processor Local Bus (PLB) version 4.6.

(Ядро интегрированного анализатора шины (IBA) ChipScope PLB - это специализированное ядро анализатора шины, предназначенное для отладки встроенных систем, содержащих локальную шину процессора IBM CoreConnect (PLB) версии 4.6.)

Скачать

DS525 - 802.16e CTC Encoder v3.0 Data Sheet (v3.0)

Apr 24, 2009

Document Type: Data Sheets

This is the data sheet for the 802.16e CTC Encoder v3.0 core.

(Это лист данных для ядра 802.16e CTC Encoder v3.0. )

Скачать

DS562 - LogiCORE PLBv46 Slave Burst (v1.01a) Data Sheet (v1.2)

Jun 22, 2010

Document Type: Data Sheets

The PLBv46 Slave Burst core is a part of the Xilinx family of PLB v4.6 compatible products. It provides a bi-directional interface between a User IP core and the PLB v4.6 bus standard.

(Ядро PLBv46 Slave Burst является частью семейства Xilinx продуктов, совместимых с PLB v4.6. Он обеспечивает двунаправленный интерфейс между ядром User IP и стандартом шины PLB v4.6.)

Скачать

DS403 - PLBV46 to OPB Bridge (v1.00a) (v1.2)

Dec 13, 2007

Document Type: Data Sheets

This is the data sheet for the PLBV46 to OPB Bridge (v1.00a) core.

(Это лист данных для ядра PLBV46 - OPB Bridge (v1.00a). )

Скачать

DS726 - OPB to PLBV46 Bridge (v1.01a) (v1.4)

Apr 24, 2009

Document Type: Data Sheets

The On-Chip Peripheral Bus (OPB) to Processor Local Bus (PLB v4.6) Bridge module translates OPB transactions into PLBV46 transactions. It functions as a slave on the OPB side and a master on the PLBV46 side.

(Модуль моста между периферийной шиной (OPB) и локальной шиной процессора (PLB v4.6) преобразует транзакции OPB в транзакции PLBV46. Он функционирует как ведомое устройство на стороне OPB и ведущее устройство на стороне PLBV46.)

Скачать

DS321 - LogiCORE IP Endpoint PIPE v1.8 for PCI Express Data Sheet (v2.0)

Jul 23, 2010

Document Type: Data Sheets

The LogiCORE IP Endpoint PIPE (PHY Interface) for PCI Express 1-lane core is a high-bandwidth scalable and reliable serial interconnect intellectual property building block for use with the Spartan-3, Spartan-3E, and Spartan-3A FPGAs in conjunction with an external PHY device.

(LogiCORE IP Endpoint PIPE (PHY-интерфейс) для однополосного ядра PCI Express - это масштабируемый и надежный блок интеллектуальной собственности для последовательного межсоединения с высокой пропускной способностью для использования с ПЛИС Spartan-3, Spartan-3E и Spartan-3A в сочетании с внешнее устройство PHY.)

Скачать

DS561 - PLBv46 Slave Single (v1.01a) Data Sheet (v1.3)

Jun 22, 2010

Document Type: Data Sheets

The PLBv46 Slave Single device is part of the Xilinx family of PLB v4.6 compatible products which provides a singles only bi-directional interface between a User IP core and the PLB v4.6 bus standard. This version of the core has been optimized for slave operation on the version 4.6 PLB Bus.

(Одиночное ведомое устройство PLBv46 является частью семейства Xilinx продуктов, совместимых с PLB v4.6, которое обеспечивает только одиночный двунаправленный интерфейс между ядром IP пользователя и стандартом шины PLB v4.6. Эта версия ядра была оптимизирована для работы ведомого устройства на шине PLB версии 4.6.)

Скачать

DS471 - Channel FIFO (CFIFO) (v1.00a) (v1.8 )

Apr 24, 2009

Document Type: Data Sheets

This is the data sheet for the Channel FIFO core.

(Это лист данных для ядра Channel FIFO.)

Скачать

DS649 - LogiCORE IP XPS Controller Area Network (CAN) (v3.01a) Data Sheet (v4.2)

Jul 23, 2010

Document Type: Data Sheets

The LogiCORE IP Controller Area Network (CAN) product specification defines the architecture and features of the Xilinx CAN controller core. This document also defines the addressing and functionality of the various registers in the design, in addition to describing the user interface.

(Спецификация продукта LogiCORE IP Controller Area Network (CAN) определяет архитектуру и функции ядра контроллера Xilinx CAN. Этот документ также определяет адресацию и функциональность различных регистров в проекте в дополнение к описанию пользовательского интерфейса.)

Скачать

DS633 - PLB to FSL Bridge v1.00a (v1.0)

Jul 04, 2007

Document Type: Data Sheets

The PLB to FSL Bridge can be used to provide FSL interface connection to any PLB v4.6 master. Both FSL master and slave interfaces are available for bi-directional transfer of data.

(Мост PLB-FSL может использоваться для обеспечения подключения интерфейса FSL к любому ведущему устройству PLB v4.6. Для двунаправленной передачи данных доступны как главный, так и подчиненный интерфейсы FSL.)

Скачать

DS563 - PLBV46 Master Single (v1.00a) (v1.2)

Apr 24, 2009

Document Type: Data Sheets

This is the data sheet for the PLBV46 Master Single (v1.00a) core.

(Это лист данных для ядра PLBV46 Master Single (v1.00a). )

Скачать

DS531 - Processor Local Bus (PLB) v4.6 (v1.05a) Data Sheet (v1.3)

Sep 21, 2010

Document Type: Data Sheets

The Xilinx 128-bit Processor Local Bus (PLB) v4.6 provides bus infrastructure for connecting an optional number of PLB masters and slaves into an overall PLB system. It consists of a bus control unit, a watchdog timer, and separate address, write, and read data path units, as well as an optional DCR (Device Control Register) slave interface to provide access to its bus error status registers.

(128-битная локальная шина процессора (PLB) Xilinx v4.6 обеспечивает шинную инфраструктуру для подключения дополнительного количества ведущих и ведомых устройств PLB в общую систему PLB. Он состоит из блока управления шиной, сторожевого таймера и отдельных блоков тракта адреса, записи и чтения данных, а также дополнительного подчиненного интерфейса DCR (регистр управления устройством) для обеспечения доступа к его регистрам состояния ошибки шины.)

Скачать

DS568 - LogiCORE XPS LL FIFO (v1.02a) Data Sheet (v1.9)

Mar 01, 2011

Document Type: Data Sheets

The XPS LL FIFO is a soft IP core designed for Xilinx FPGAs. This core allows memory mapped access to a LocalLink interface. The core can be used to interface to the XPS LL TEMAC without the need to use DMA. Other uses include interfacing to the LocalLink interfaces on PLBv46 PCIe and PLBv46 PCI.

(XPS LL FIFO - это программное IP-ядро, разработанное для ПЛИС Xilinx. Это ядро обеспечивает доступ с отображением памяти к интерфейсу LocalLink. Ядро может использоваться для взаимодействия с XPS LL TEMAC без необходимости использования DMA. Другие применения включают взаимодействие с интерфейсами LocalLink на PLBv46 PCIe и PLBv46 PCI.)

Скачать

DS634 - IEEE 802.16e CTC Decoder v4.0 Data Sheet (v1.3)

Dec 02, 2009

Document Type: Data Sheets

The IEEE 802.16e CTC decoder core performs iterative decoding of channel data that has been encoded as described in Section 8.4.9.2.3 of the IEEE Std 802.16e-2005 specification and corrigendum IEEE P802.16Rev2/D0b (June 2007).

(Ядро декодера CTC IEEE 802.16e выполняет итеративное декодирование данных канала, которые были закодированы, как описано в разделе 8.4.9.2.3 спецификации IEEE Std 802.16e-2005 и исправлении IEEE P802.16Rev2 / D0b (июнь 2007 г.). )

Скачать

DS591 - OPB Universal Serial Bus 2.0 Device (v1.00a) Data Sheet (v1.0)

May 10, 2007

Document Type: Data Sheets

This is the data sheet for the OPB Universal Serial Bus 2.0 Device (v1.00a) core.

(Это лист данных для ядра OPB Universal Serial Bus 2.0 Device (v1.00a). )

Скачать

DS650 - Agilent Trace Core 2 (ATC2) (v1.04a) Data Sheet (v2.2)

Jun 22, 2011

Document Type: Data Sheets

The Agilent Trace Core 2 (ATC2) is a customizable debug capture core that is specially designed to work with the latest generation logic analyzers from Agilent Technologies. The ATC2 core provides external Agilent logic analyzers access to internal FPGA design nets.

(Agilent Trace Core 2 (ATC2) - это настраиваемое ядро отладки, которое специально разработано для работы с логическими анализаторами последнего поколения от Agilent Technologies. Ядро ATC2 предоставляет внешним логическим анализаторам Agilent доступ к внутренним схемам проектирования FPGA.)

Скачать

DS593 - Platform Cable USB II Data Sheet (v1.5.1)

Aug 07, 2018

Document Type: Data Sheets

Platform Cable USB II provides integrated firmware, hardware, and software to deliver high-performance, reliable and easy-to-perform configuration of Xilinx devices.

(Platform Cable USB II предоставляет встроенное микропрограммное обеспечение, оборудование и программное обеспечение для обеспечения высокопроизводительной, надежной и простой в использовании конфигурации устройств Xilinx. )

Скачать

DS284 - LogiCORE IP ChipScope Pro Virtual Input/Output (VIO) (v1.04a) Data Sheet (v3.2)

Jun 22, 2011

Document Type: Data Sheets

The Virtual Input/Output (VIO) core is a customizable core that can both monitor and drive internal FPGA signals in real time.

(Ядро виртуального ввода/вывода (VIO) - это настраиваемое ядро, которое может как отслеживать, так и управлять внутренними сигналами ПЛИС в реальном времени.)

Скачать

DS616 - PLBV46 PCI Full Bridge (v1.04a) Data Sheet (v1.4)

Jun 22, 2011

Document Type: Data Sheets

The PLBV46 PCI Full Bridge design provides full bridge functionality between the Xilinx PLB and a 32-bit Revision 2.2 compliant Peripheral Component Interconnect (PCI) bus.

(Конструкция полного моста PCI PLBV46 обеспечивает полную функциональность моста между Xilinx PLB и 32-разрядной шиной Peripheral Component Interconnect (PCI), совместимой с версией 2.2.)

Скачать

DS440 - Channelized Direct Memory Access and Scatter Gather Data Sheet (v1.5.1)

Feb 25, 2010

Document Type: Data Sheets

This is the data sheet for the Channelized Direct Memory Access and Scatter Gather core.

(Это лист данных для ядра Channelized Direct Memory Access и Scatter Gather.)

Скачать

DS275 - 3GPP2 Turbo Decoder v2.1 Data Sheet (v2.1)

Feb 15, 2007

Document Type: Data Sheets

This is the data sheet for 3GPP2 Turbo Decoder v2.1.

(Это лист данных для 3GPP2 Turbo Decoder v2.1. )

Скачать

DS402 - Device Control Register Bus (DCR) v2.9 Data Sheet (v2.1)

Apr 19, 2010

Document Type: Data Sheets

This is the data sheet for the Device Control Register Bus (DCR) v2.9 core.

(Это лист данных для ядра шины регистров управления устройством (DCR) v2.9)

Скачать

DS318 - 3GPP Turbo Decoder v4.0 Data Sheet (v4.0)

Jun 24, 2009

Document Type: Data Sheets

The Turbo Convolution Code (TCC) Decoder core is used in conjunction with a TCC Encoder to provide an extremely effective way of transmitting data reliably over noisy data channels, and is designed to meet the 3GPP Mobile Communication System specification.

(Ядро декодера Turbo Convolution Code (TCC) используется вместе с TCC Encoder, чтобы обеспечить чрезвычайно эффективный способ надежной передачи данных по каналам данных с шумом, и разработано в соответствии со спецификацией системы мобильной связи 3GPP.)

Скачать

DS586 - LogiCORE IP XPS HWICAP (v5.01a) Data Sheet (v1.7.1)

Jun 22, 2011

Document Type: Data Sheets

This product specification describes the functionality of the HWICAP core for the Processor Local Bus (PLB). The XPS HWICAP (Hardware ICAP) IP enables an embedded microprocessor, such as the MicroBlaze or PowerPC to read and write the FPGA configuration memory through the Internal Configuration Access Port (ICAP) at run time, which enables a user to write software programs for an embedded processor that modifies the circuit structure and functionality during the circuit’s operation.

(Эта спецификация продукта описывает функциональные возможности ядра HWICAP для локальной шины процессора (PLB). XPS HWICAP (Hardware ICAP) IP позволяет встроенному микропроцессору, например MicroBlaze или PowerPC, читать и записывать конфигурационную память FPGA через внутренний порт доступа к конфигурации (ICAP) во время выполнения, что позволяет пользователю писать программы для встроенного процессора, который изменяет структуру и функциональность схемы, во время работы схемы.)

Скачать

DS300 - Platform Cable USB Data Sheet (v3.3)

Jun 25, 2014

Document Type: Data Sheets

Platform Cable USB is a high-performance download cable that attaches to user hardware for the purpose of programming or configuring Xilinx devices such as ISP Configuration PROMs, CPLDs, and FPGAs.

(Platform Cable USB - это высокопроизводительный загрузочный кабель, который подключается к пользовательскому оборудованию с целью программирования или настройки устройств Xilinx, таких как PROM конфигурации ISP, CPLD и FPGA.)

Скачать

DS123 - Platform Flash In-System Programmable Configuration PROMs Data Sheet (v2.19)

Jun 07, 2016

Document Type: Data Sheets

Complete data sheet for Platform Flash In-System Programmable Configuration PROMs. Available in 1 to 32 Megabit densities (XCF01S, XCF02S, XCF04S, XCF08P, XCF16P, and XCF32P), these PROMs provide an easy-to-use, cost-effective, and reprogrammable method for storing large Xilinx FPGA configuration bitstreams.

(Полный лист данных для ППЗУ с программируемой внутрисистемной флэш-памятью платформы. Доступные с плотностью от 1 до 32 Мегабит (XCF01S, XCF02S, XCF04S, XCF08P, XCF16P и XCF32P), эти PROM обеспечивают простой в использовании, экономичный и перепрограммируемый метод хранения больших потоков битов конфигурации Xilinx FPGA.)

Скачать

DS402 - On-Chip Peripheral Bus V2.0 w/OPB Arbiter Data Sheet (v1.4)

Apr 19, 2010

Document Type: Data Sheets

This is the data sheet for the On-Chip Peripheral Bus V2.0 with OPB Arbiter (v1.10d) core.

(Это лист данных для On-Chip Peripheral Bus V2.0 с ядром OPB Arbiter (v1.10d). )

Скачать

DS986 - Kria KV260 Vision AI Starter Kit Data Sheet (v1.0)

Apr 20, 2021

Document Type: Data Sheets

Contains the specifications for the Kria KV260 Vision AI starter kit.

(Содержит спецификации для стартового набора Kria KV260 Vision AI.)

Скачать

DS416 - Direct Memory Access and Scatter Gather (v2.01a) (v1.5)

Apr 24, 2009

Document Type: Data Sheets

The DMA SG service is a continuation of the Xilinx family of IBM CoreConnect compatible LogiCORE products. It provides direct memory access (DMA) allowing for a bounded number of sequential data transfers to take place between regions in the address space, typically between memory and an I/O device, without processor management of individual transfers. This service also provides Scatter Gather (SG) functionality allowing a sequence of DMA operations to be prespecified by software and performed automatically without further processor intervention.

(Служба DMA SG является продолжением семейства Xilinx продуктов LogiCORE, совместимых с IBM CoreConnect. Он обеспечивает прямой доступ к памяти (DMA), позволяющий осуществлять ограниченное количество последовательных передач данных между областями в адресном пространстве, обычно между памятью и устройством ввода-вывода, без управления процессором отдельных передач. Эта служба также обеспечивает функциональность Scatter Gather (SG), позволяющую программно задавать последовательность операций прямого доступа к памяти и выполнять их автоматически без дальнейшего вмешательства процессора.)

Скачать

UG065 - PHY Daughter Card User Guide (v1.0)

May 05, 2004

Document Type: Data Sheets

This guide documents the PHY daughter card for use with Xilinx ML32x Development Platforms.

(В этом руководстве описана дочерняя карта PHY для использования с платформами разработки Xilinx ML32x.)

Скачать

...

Последний раз редактировалось: Viktor2312 (Сб Дек 04 2021, 17:30), всего редактировалось 4 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

3

Разное.

1.

- Спойлер:

Data Sheets

DS706 - Extended Spartan-3A Family Overview / Расширенный обзор семейства Spartan-3A ( ver1.1, 187 KB )

Скачать

This document introduces the Extended Spartan-3A family of FPGAs. It provides features, a device summary, functional overview, packaging options, and ordering information for the device family.

DS529 - Spartan-3A FPGA Family Data Sheet ( ver2.0, 5937 KB )

Скачать

Spartan-3A FPGA Family Data Sheet, including Overview, Specifications, and Pinouts. See the Spartan-3 Generation User Guides for additional information.

Extended Spartan-3A Family CLKFX Jitter Calculator ( ver1.0.6, 8 KB ) [ZIP]

Скачать

Excel file to calculate DFS output jitter based on input and output clock frequencies. Applies to Spartan-3A, Spartan-3AN, and Spartan-3A DSP platforms.

Extended Spartan-3A Family ASCII Pinouts and Excel Footprints ( ver1.3, 417 KB ) [ZIP]

Скачать

Comma-delimited ASCII text files and Excel footprints for each package type in the Extended Spartan-3A Family (Spartan-3A, Spartan-3AN, and Spartan-3A DSP platforms).

XC3S200A-4VQG100C

...

Последний раз редактировалось: Viktor2312 (Сб Дек 04 2021, 13:18), всего редактировалось 3 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

4

Документация.

Tutorials (Учебники)

ISE 11 In-Depth Tutorial (v11.2)

Jun 24, 2009

Document Type: Tutorials

ISE 11 Software Design Suite.

(Интегрированное программное средство разработки, версии 11)

Скачать

...

Последний раз редактировалось: Viktor2312 (Сб Дек 04 2021, 17:32), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

5

Документация.

Release Notes (Примечания к выпуску)

Release Notes (Примечания к выпуску)

UG631 - Xilinx ISE Design Suite 14: Release Notes, Installation, and Licensing (v14.7)

Jul 10, 2020

Document Type: Release Notes

Release information, What's New, installation, and licensing for ISE design tools.

(Информация о выпуске, что нового, установка и лицензирование средств проектирования ISE.)

Скачать

...

Последний раз редактировалось: Viktor2312 (Сб Дек 04 2021, 17:33), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

6

Документация.

Errata (Опечатки)

Errata (Опечатки)

EN036 - XC3S1400A Errata for Engineering Samples (v1.1)

Apr 16, 2007

Document Type: Errata

Spartan-3A XC3S1400A Errata for Engineering Samples.

(Spartan-3A XC3S1400A Исправления для инженерных образцов.)

Скачать

EN035 - XC3S700A Errata for Engineering Samples (v1.1)

Apr 16, 2007

Document Type: Errata

Spartan-3A XC3S700A Errata for Engineering Samples.

(Spartan-3A XC3S700A Исправления для инженерных образцов.)

Скачать

EN033 - XC3S700AN Errata for Engineering Samples (v1.3)

Sep 12, 2007

Document Type: Errata

Spartan-3AN XC3S700AN Errata.

(Spartan-3AN XC3S700AN Опечатки.)

Скачать

EN028 - XC3S200AN Errata for Engineering Samples (v1.2)

Aug 16, 2007

Document Type: Errata

Spartan-3AN XC3S200AN Errata

(Spartan-3AN XC3S200AN Опечатки.)

Скачать

EN032 - XC3S400AN Errata for Engineering Samples (v1.2)

Sep 24, 2007

Document Type: Errata

Spartan-3AN XC3S400AN Errata

(Spartan-3AN XC3S400AN Опечатки.)

Скачать

EN034 - XC3S1400AN Errata for Engineering Samples (v1.3)

Aug 31, 2007

Document Type: Errata

Spartan-3AN XC3S1400AN Errata

(Spartan-3AN XC3S1400AN Опечатки.)

Скачать

EN027 - XC3S50AN Errata for Engineering Samples (v1.2)

Dec 12, 2007

Document Type: Errata

Spartan-3AN XC3S50AN Errata

(Spartan-3AN XC3S50AN Опечатки.)

Скачать

...

Последний раз редактировалось: Viktor2312 (Сб Дек 04 2021, 17:28), всего редактировалось 1 раз(а)

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

7

Документация.

Board Files

Board Files

Spartan-3A/3AN Starter Kit Schematics (v1.0.2)

Aug 21, 2007

Document Type: Data Sheets,Board Files

Spartan-3A/3AN FPGA Starter Kit board schematics.

(Схема платы стартового комплекта Spartan-3A/3AN FPGA.)

Скачать

Associated File(s): Скачать

Spartan-3A/3AN FPGA Starter Kit Board Gerber Plots (v1.0)

Aug 02, 2007

Document Type: Board Files

Gerber board layout plots in PDF format for the Spartan-3A and Spartan-3AN FPGA Starter Kit boards.

(Графики компоновки платы Gerber в формате PDF для плат Spartan-3A и Spartan-3AN FPGA Starter Kit.)

Скачать

RDF0087 - Spartan-3A Kit MIG Reference Design Files

RDF0087 - Spartan-3A Kit MIG Reference Design FilesDocument Type: Board Files

(Файлы эталонного дизайна для MIG комплекта Spartan-3A)

Скачать

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

8

Документация.

Product Briefs (Краткое описание продукта)

Product Briefs (Краткое описание продукта)

XMP004 - IEEE 802.16e CTC Decoder v4.0 Product Brief (v2.1)

Dec 02, 2009

Document Type: Product Briefs

This is the product brief for the IEEE 802.16e CTC Decoder v4.0 core.

(Это краткое описание продукта для ядра IEEE 802.16e CTC Decoder v4.0.)

Скачать

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

9

Документация.

Backgrounder (Справочная информация)

Backgrounder (Справочная информация)

2016 North American Automotive PLDs For ADAS Product Leadership Award

(2016 Североамериканские автомобильные PLD получили награду ADAS Product Leadership Award)

Document Type: Backgrounder

Frost & Sullivan 2016 Best Practices Awards

(Награды Frost & Sullivan Best Practices Awards 2016)

https://cloud.mail.ru/public/JCWW/NVVkQjPxH

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

10

Документация.

Libraries Guides (Руководства по "библиотекам")

Libraries Guides (Руководства по "библиотекам")

UG613 - Spartan-3A and Spartan-3A DSP Libraries Guide for HDL Designs (v14.7)

Oct 02, 2013

Document Type: Libraries Guides

Describes circuit design elements associated with the Spartan-3A and Spartan-3A DSP architectures. Details for each element include VHDL and Verilog instantiation code, schematic symbols, truth tables, and other information specific to the design element.

(Описывает элементы схемотехники, связанные с архитектурами Spartan-3A и Spartan-3A DSP. Подробная информация для каждого элемента включает в себя код создания экземпляра VHDL и Verilog, схематические символы, таблицы истинности и другую информацию, относящуюся к элементу дизайна.)

Скачать

Associated File(s):

Spartan3a_Library_Guide_14.7_HDL_Templates.zip : Скачать

Spartan3a_Library_Guide_14.7_HDL_Templates.zip : Скачать Spartan3adsp_Library_Guide_14.7_HDL_Templates.zip : Скачать

Spartan3adsp_Library_Guide_14.7_HDL_Templates.zip : СкачатьUG614 - Spartan-3A and Spartan-3A DSP Libraries Guide for Schematic Designs (v14.7)

Oct 02, 2013

Document Type: Libraries Guides

Describes circuit design elements associated with the Spartan-3A and Spartan-3A DSP architectures. Details for each element include schematic symbols, truth tables, and other information specific to the design element.

(Описывает элементы схемотехники, связанные с архитектурами Spartan-3A и Spartan-3A DSP. Подробности для каждого элемента включают схематические символы, таблицы истинности и другую информацию, относящуюся к элементу дизайна.)

Скачать

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

11

Документация.

Customer Notices (Уведомления клиентов)

Customer Notices (Уведомления клиентов)

XCN11019 - Data Sheet Revisions for Xilinx Automotive (XA) Spartan-3A/-3A DSP FPGA Devices (v1.0)

Apr 18, 2011

Document Type: Customer Notices

To communicate some revisions to the Xilinx Automotive (XA) Spartan-3A and Spartan-3A DSP data sheets describing parasitic leakage current that may occur when an input is below -0.2V.

(Чтобы сообщить о некоторых изменениях в таблицах данных Xilinx Automotive (XA) Spartan-3A и Spartan-3A DSP, описывающих паразитный ток утечки, который может возникнуть, когда входное напряжение ниже -0,2 В.)

Скачать

XCN08014 - Package Substrate Change for Spartan-3A and Spartan-3AN Devices (v1.0)

Oct 20, 2008

Document Type: Customer Notices

This notice is to announce the standardization of remaining Spartan-3A devices to the current 2-layer substrate for the FT256 and FTG256 packages.

(В этом уведомлении объявляется о стандартизации оставшихся устройств Spartan-3A на текущую двухслойную подложку для корпусов FT256 и FTG256.)

Скачать

Associated File(s):

rpt112.pdf : Скачать

rpt112.pdf : Скачатьxtp036.pdf : Скачать

XCN07024 - Spartan-3A/-3AN/-3A DSP Chip-Select Controlled SelectMAP and ICAP Data Loading (v1.0)

Nov 26, 2007

Document Type: Customer Notices

The purpose of this Quality Alert is to communicate that the Non-continuous Slave Parallel (SelectMAP) or ICAP_SPARTAN3A data loading via de-asserting CSI_B does not function as expected, and is not a supported feature of these devices.

(Целью этого предупреждения о качестве является сообщение о том, что непостоянная параллельная загрузка данных ведомого устройства (SelectMAP) или ICAP_SPARTAN3A посредством отмены утверждения CSI_B не работает должным образом и не является поддерживаемой функцией этих устройств.)

Скачать

XCN10001 - Additional Test Site for Xilinx Automotive (XA) Spartan-3/-3E/-3A/-3A DSP devices (v1.0)

Mar 01, 2010

Document Type: Customer Notices

To add Amkor Technology Philippines "ATP", as an additional test site for Xilinx Automotive (XA) Spartan-3/-3E/-3A/-3A DSP devices. There is no change to the form, fit, or function.

(Добавить Amkor Technology Philippines «ATP» в качестве дополнительной испытательной площадки для устройств Xilinx Automotive (XA) Spartan-3/-3E/-3A/-3A DSP. Нет никаких изменений в форме, посадке или функциях.)

Скачать

Associated File(s):

rpt111.pdf : Скачать

rpt111.pdf : СкачатьXCN13003 - Product Discontinuation Notice: Selected Automotive Spartan-3/-3A DSP FPGA Products (v1.0)

Jan 21, 2013

Document Type: Customer Notices

This notification is to communicate that Xilinx is discontinuing certain Automotive (XA) Spartan-3/-3A DSP FPGA products.

(Это уведомление означает, что Xilinx прекращает выпуск некоторых продуктов Automotive (XA) Spartan-3/-3A DSP FPGA.)

Скачать

XCN14001 - Package Bill of Material Gold (Au) To Copper (Cu) Wire Change for Spartan-3A DSP FPGA Products (v1.0)

Dec 09, 2013

Document Type: Customer Notices

To announce the transitioning of all wire bond package types for Spartan-3A DSP FPGA Products from gold (Au) to copper (Cu) wire.

(Чтобы объявить о переходе всех типов корпусов проводов для продуктов Spartan-3A DSP FPGA с золотых (Au) на медные (Cu) провода.)

Скачать

XCN20010 - Product Discontinuation Notice For Selective Spartan-3A, Virtex-5, Virtex-7 and SSIT FPGA Packages (v1.1)

Oct 05, 2020

Document Type: Customer Notices

The purpose of this notification is to communicate that Xilinx is discontinuing selective packages for Spartan-3A, Virtex-5, Virtex-7 and SSIT FPGA products. This product discontinuation notice (PDN) applies to all speed and temperature-grade variations in the stated package pins.

(Цель этого уведомления - сообщить, что Xilinx прекращает выпуск выборочных пакетов для продуктов Spartan-3A, Virtex-5, Virtex-7 и SSIT FPGA. Это уведомление о прекращении производства продукта (PDN) распространяется на все отклонения по скорости и температуре в указанных выводах на упаковке.)

Скачать

XCN15005 - Package Bill of Material Gold (Au) To Copper (Cu) Wire Change For Automotive (XA) Spartan-6 And (XA) Spartan-3/-3E/-3A/-3A DSP FPGA Products (v1.0)

Jul 06, 2015

Document Type: Customer Notices

To announce the transitioning of all wire bond package types for Automotive “XA” Spartan-3/-3E/-3A/-3A DSP and Spartan-6 FPGA products from gold (Au) to copper (Cu) wire.

(Объявить о переводе проводов всех типов корпусов для автомобильных «XA» Spartan-3/-3E/-3A/-3A DSP и Spartan-6 FPGA с золотых (Au) на медные (Cu) провода.)

Скачать

XCN11002 - Package Bill of Material Gold (Au) To Copper (Cu) Wire Change for Spartan-3, Spartan-3E and Spartan-3A FPGA Products (v1.0)

Aug 15, 2011

Document Type: Customer Notices

To announce the transitioning of all wire bond package types for Spartan-3, Spartan-3E and Spartan-3A FPGA products from gold (Au) to copper (Cu) wire.

(Объявить о переходе всех типов корпусов проводов для продуктов ПЛИС Spartan-3, Spartan-3E и Spartan-3A с золотых (Au) на медные (Cu) провода.)

Скачать

XCN14009 - Addition of Final Test Site for All Automotive (XA) Spartan FPGA Product Family (v1.0)

Feb 10, 2014

Document Type: Customer Notices

To inform customers that Xilinx is adding a final test site in Taiwan for all our Automotive (XA) Spartan-3/-3E/-3A/-3ADSP and Spartan-6 FPGA product families.

(Чтобы проинформировать клиентов о том, что Xilinx добавляет последний испытательный полигон на Тайване для всех наших автомобильных семейств Spartan-3/-3E/-3A/-3ADSP и Spartan-6 FPGA.)

Скачать

XCN11018 - Spartan, Virtex and CoolRunner Series Wire Bond BGA Packaging Material Source Addition (v2.0)

Jul 25, 2011

Document Type: Customer Notices

To communicate the addition of new supply sources for wire bond BGA package core and prepreg material for Spartan/-XL/-II/-IIE/-3/-3E/-3A/-3AN/-3ADSP/-6, XC95XXX, XC95XXXXL, Virtex, Virtex-E, Virtex-II/-ll Pro, and CoolRunner and CoolRunner-II product.

(Чтобы сообщить о добавлении новых источников поставки для сердечника корпуса BGA и материала препрега для Spartan/-XL/-II/-IIE/-3/-3E /-3A/-3AN/-3ADSP/-6, XC95XXX, XC95XXXXL , Virtex, Virtex-E, Virtex-II/-ll Pro, а также CoolRunner и CoolRunner-II.)

Скачать

XTP343 - FAQ: Flash Wafer Fabrication Change and Gold (Au) To Copper (Cu) Transition For Spartan-3AN FPGA Devices (v1.7)

Oct 03, 2016

Document Type: Customer Notices

Frequently Asked Questions: Implications of XCN14003.

(Часто задаваемые вопросы: значение XCN14003.)

Скачать

XCN15029 - Product Discontinuation Notice for Development Systems Products (v1.0)

Jun 22, 2015

Document Type: Customer Notices

To communicate that Xilinx is discontinuing some Development Systems Spartan Kits.

(Чтобы сообщить, что Xilinx прекращает выпуск некоторых комплектов Spartan Kits для систем разработки.)

Скачать

XCN12013 - Product Discontinuation Notice for Development Systems Products (v1.0)

Jun 25, 2012

Document Type: Customer Notices

To communicate that Xilinx is discontinuing certain Development Systems products – LogiCORE, 3GPP RACH Preamble Detector, LogiCORE, 3GPP Searcher, LogiCORE, AEHF Turbo Convolutional Encoder, LogiCORE, AEHF Turbo Convolutional Decoder, and LogiCORE, MOST NIC.

(Чтобы сообщить, что Xilinx прекращает выпуск определенных продуктов системы разработки - LogiCORE, 3GPP RACH Preamble Detector, LogiCORE, 3GPP Searcher, LogiCORE, AEHF Turbo Convolutional Encoder, LogiCORE, AEHF Turbo Convolutional Decoder и LogiCORE, MOST NIC.)

Скачать

XCN09033 - Humidity Indicator Card (HIC) Change (v1.0)

Dec 07, 2009

Document Type: Customer Notices

To inform customers of a change to the Humidity Indicator Card (HIC). There is no change to the form, fit, or function.

(Чтобы проинформировать клиентов об изменении карты индикатора влажности (HIC). Нет никаких изменений в форме, посадке или функциях.)

Скачать

XCN11016 - Product Discontinuation Notice for Development Systems Product (v1.0.1)

Apr 26, 2011

Document Type: Customer Notices

To communicate that Xilinx is discontinuing certain Development Systems products.

(Сообщать, что Xilinx прекращает выпуск определенных продуктов Development Systems.)

Скачать

XCN14003 - Flash Wafer Fabrication Change and Gold (Au) To Copper (Cu) Transition For Spartan-3AN FPGA Devices (v1.3)

Oct 27, 2014

Document Type: Customer Notices

To communicate a change in wafer fabrication facility location and process technology shrink change in-system flash memory used in the Spartan-3AN FPGA devices. In addition, Xilinx is transitioning the wire bond packages from gold (Au) to copper (Cu) wires.

(Чтобы сообщить об изменении местоположения завода по изготовлению полупроводниковых пластин и технологического процесса, изменения в системной флэш-памяти, используемой в устройствах Spartan-3AN FPGA. Кроме того, Xilinx переводит пакеты проводов с золотых (Au) на медные (Cu). )

Скачать

...

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

12

Документация.

Constraints Guide (Руководство по ограничениям).

Constraints Guide (Руководство по ограничениям).

UG625 (v 11.4) December 2, 2009

Скачать

Содержание руководства.

Это руководство состоит из следующих глав:

- Об этом Руководстве, обсуждает, что нового в этом Руководстве для ISE Design Suite, и предоставляет другую вводную информацию.

- Типы ограничений, обсуждает различные типы ограничений, задокументированные в этом Руководстве, включая установщик CPLD, ограничения группировки, логические ограничения, физические ограничения, директивы сопоставления, ограничения размещения, директивы маршрутизации, ограничения синтеза, временные ограничения.

- Стратегии входа для ограничений Xilinx, обсуждает стратегии входа для ограничений Xilinx, в том числе, какую функцию программного обеспечения ISE использовать для ввода заданного типа ограничения.

- Стратегии ограничения времени, содержат общие рекомендации, объясняющие, как ограничить время в проектах при использовании инструментов реализации для устройств FPGA.

- Ограничения Xilinx описывают отдельные ограничения, которые могут использоваться с устройствами Xilinx FPGA и CPLD, включая для каждого ограничения поддержку архитектуры, применимые элементы, описание, правила распространения, примеры синтаксиса и, при необходимости, дополнительную информацию для конкретных ограничений.

.

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

13

Документация.

White Papers (Белая книга).

White Papers (Белая книга).

WP267 - Advanced Security Schemes for Spartan-3A/3AN/3A DSP FPGAs (v1.0)

Aug 15, 2007

Document Type: White Papers

This white paper identifies the top design security threats, explores the advanced security options, and describes how new, low-cost Spartan-3A, Spartan-3AN, and Spartan-3A DSP FPGAs from Xilinx can help protect your products and profits.

(В этом техническом документе определяются основные угрозы безопасности, исследуются расширенные возможности безопасности и описывается, как новые недорогие ПЛИС Spartan-3A, Spartan-3AN и Spartan-3A DSP от Xilinx могут помочь защитить ваши продукты и прибыль.)

Скачать

WP277 - Expanding Dedicated Multipliers (v1.0)

May 22, 2008

Document Type: White Papers

This white paper describes methods for expanding the natural bit-width capability of dedicated multipliers in a way that will make best use of the complete FPGA resources.

(В этом техническом документе описаны методы расширения возможностей выделенных умножителей естественной разрядности таким образом, чтобы максимально использовать все ресурсы FPGA.)

Скачать

WP324 - New High Speed Broadcast Video Connectivity Solution (3G) with Low-cost FPGAs (v1.0)

Nov 28, 2007

Document Type: White Papers

Using Xilinx Spartan-3E and Spartan-3A FPGAs, a National Semiconductor PHY, and a Xilinx video processing stack provides a very cost-effective and flexible approach to the challenges of multi-rate broadcast.

(Использование ПЛИС Xilinx Spartan-3E и Spartan-3A, PHY National Semiconductor и стека обработки видео Xilinx обеспечивает очень экономичный и гибкий подход к проблемам многоскоростного вещания.)

Скачать

WP260 - Memory Interfaces Made Easy with Xilinx FPGAs and the Memory Interface Generator (v1.0)

Feb 16, 2007

Document Type: White Papers

This white paper discusses the various memory interface controller design challenges and Xilinx solutions, including how to use the Xilinx software tools and hardware-verified reference designs to build a complete memory interface solution for your own application, from low-cost DDR SDRAM applications to higher-performance interfaces like the 667Mb/s DDR2 SDRAMs.

(В этом техническом документе обсуждаются различные проблемы проектирования контроллеров интерфейса памяти и решения Xilinx, в том числе способы использования программных средств Xilinx и проверенных аппаратным обеспечением эталонных проектов для создания полного решения интерфейса памяти для вашего собственного приложения, от недорогих приложений DDR SDRAM до более сложных. Производительные интерфейсы, такие как DDR2 SDRAM со скоростью 667 Мбит/с.)

Скачать

WP330 - Infinite Impulse Response Filter Structures in Xilinx FPGAs (v1.2)

Aug 10, 2009

Document Type: White Papers

This white paper covers the different kinds of IIR filters and structures, and, with the use of The MathWorks tools, shows how these structures can be mapped to the Xilinx FPGA architecture.

(В этом техническом документе рассматриваются различные типы фильтров и структур БИХ, а также с использованием инструментов MathWorks показано, как эти структуры могут быть сопоставлены с архитектурой Xilinx FPGA.)

Скачать

WP230 - Physical Synthesis and Optimization with ISE 9.1i (v1.1)

May 16, 2007

Document Type: White Papers

The Physical Synthesis and Optimization tools in the Xilinx ISE software have been created to reexamine the structure of your FPGA design during the packing and placement phases of implementation.

(Инструменты физического синтеза и оптимизации в программном обеспечении Xilinx ISE были созданы для повторного изучения структуры вашего проекта FPGA на этапах упаковки и размещения.)

Скачать

WP273 - Performance + Time = Memory (Cost Saving with 3-D Design) (v1.0)

Feb 01, 2008

Document Type: White Papers

Operating logic at a higher rate than the processing rate allows operations to be achieved sequentially. As with a processor, logic is timeshared over multiple clock cycles. Memory holds values not being used on a given clock cycle. The FPGA can be considered to be a three-dimensional volume to be filled. "Performance + Time = Memory" is a strange formula, but when understood, it can often result in significantly lower cost implementations with Xilinx devices.

(Операционная логика с более высокой скоростью, чем скорость обработки, позволяет выполнять операции последовательно. Как и в случае с процессором, логика распределяется по времени в течение нескольких тактовых циклов. В памяти хранятся значения, не используемые в данном тактовом цикле. FPGA можно рассматривать как трехмерный объем, который необходимо заполнить. «Производительность + время = память» - странная формула, но если ее понять, она часто может привести к значительно более дешевым реализациям с устройствами Xilinx.)

Скачать

WP335 - Creative Uses of Block RAM (v1.0)

Jun 04, 2008

Document Type: White Papers

This white paper examines alternate uses of available block RAM in Virtex and Spartan FPGAs.

(В этом техническом документе рассматриваются альтернативные варианты использования доступной блочной ОЗУ в ПЛИС Virtex и Spartan.)

Скачать

WP320 - It's Not the Same Old PCB Anymore (v1.0)

Mar 27, 2008

Document Type: White Papers

This white paper discusses signal analysis requirements and methods for printed circuit board design for Xilinx FPGAs.

(В этом техническом документе обсуждаются требования и методы анализа сигналов для проектирования печатных плат для ПЛИС Xilinx.)

Скачать

WP321 - IBIS Model Usage (v1.0)

Mar 27, 2008

Document Type: White Papers

This white paper defines IBIS models and describes how to use them to model I/O characteristics for Xilinx FPGAs.

(В этом техническом документе определяются модели IBIS и описывается, как их использовать для моделирования характеристик ввода-вывода для ПЛИС Xilinx.)

Скачать

WP322 - Bit Error Ratio: What Is It? What Does It Mean? (v1.0)

(Коэффициент битовых ошибок: что это такое? Что это значит?)

Mar 27, 2008

Document Type: White Papers

This white paper defines the use and limitations of bit error ratio measurements when analyzing the performance of communications links.

(В этом техническом документе определяются использование и ограничения измерения коэффициента ошибок по битам при анализе производительности каналов связи.)

Скачать

WP315 - I/O Design Flexibility with the FPGA Mezzanine Card (FMC) (v1.0)

Aug 19, 2009

Document Type: White Papers

The FPGA Mezzanine Card (FMC) standard, developed by a consortium of companies ranging from FPGA vendors to end users, specifically targets FPGAs, increasing I/O flexibility and lowering costs in a broad range of applications.

(Стандарт FPGA Mezzanine Card (FMC), разработанный консорциумом компаний, от поставщиков FPGA до конечных пользователей, специально нацелен на FPGA, увеличивая гибкость ввода-вывода и снижая затраты в широком спектре приложений.)

Скачать

WP276 - Programmable Development and Test (v1.0.1)

Mar 07, 2008

Document Type: White Papers

FPGAs can be configured with test applications during the development and production test stage. This white paper explores efficient options to help in product development and accelerate testing on the production line.

(ПЛИС можно настроить с тестовыми приложениями на этапе разработки и тестирования в производстве. В этом техническом документе рассматриваются эффективные варианты помощи в разработке продукта и ускорения тестирования на производственной линии.)

Скачать

WP319 - Jitter: Variations in the Significant Instants of a Clock or Data Signal (v1.0)

Mar 24, 2008

Document Type: White Papers

This white paper examines the causes of jitter, jitter measurement techniques, and methods of managing jitter in digital systems.

(В этом техническом документе рассматриваются причины джиттера, методы измерения джиттера и методы управления джиттером в цифровых системах.)

Скачать

WP271 - Saving Costs with the SRL16E (v1.0)

May 08, 2008

Document Type: White Papers

This white paper provides examples to help your understanding of the capabilities and use of the SRL16E to improve the performance and lower the cost of your designs by as much as an order of magnitude.

(В этом техническом документе представлены примеры, которые помогут вам понять возможности и использование SRL16E для повышения производительности и снижения стоимости ваших проектов на порядок.)

Скачать

WP353 - Seven Steps to an Accurate Worst-Case Power Analysis Using Xilinx Power Estimator (v1.0)

Sep 30, 2008

Document Type: White Papers

This white paper describes the steps necessary to analyze your design's power requirements using the Xilinx Power Estimator.

(В этом техническом документе описаны шаги, необходимые для анализа требований к электропитанию вашей конструкции с помощью средства оценки мощности Xilinx.)

Скачать

WP365 - Solving Today's Design Security Concerns (v1.2)

Jul 30, 2012

Document Type: White Papers

This white paper describes the various threats to design security and the solutions offered by modern FPGAs.

(В этом техническом документе описаны различные угрозы безопасности проектирования и решения, предлагаемые современными ПЛИС.)

Скачать

WP323 - Signal Integrity: Tips and Tricks (v1.0)

Mar 28, 2008

Document Type: White Papers

This white paper describes design techniques that improve signal integrity in Xilinx FPGAs.

(This white paper describes design techniques that improve signal integrity in Xilinx FPGAs.)

Скачать

WP258 - Considerations for Heatsink Selection - Xilinx Thermal Data Application (v1.0)

Feb 08, 2007

Document Type: White Papers

This white paper reviews the potential inaccuracies associated with the traditional one-resistor approach to selecting heatsinks, and suggests a more accurate two-resistor (2-R) approach based on both theta-jc and theta-jb from the device datasheet.

(В этом техническом документе рассматриваются возможные неточности, связанные с традиционным подходом с одним резистором к выбору радиаторов, и предлагается более точный подход с двумя резисторами (2-R), основанный как на theta-jc, так и на theta-jb из таблицы данных устройства.)

Скачать

WP240 - AccelDSP Synthesis Tool Supported MATLAB Constructs and Functions (v1.1)

Dec 08, 2006

Document Type: White Papers

This document provides a concise overview of the subset of the MATLAB language, including operators, as well as built-in and toolbox functions supported by AccelDSP Synthesis Tool for algorithmic synthesis targeting Xilinx FPGAs.

(В этом документе представлен краткий обзор подмножества языка MATLAB, включая операторы, а также встроенные функции и функции набора инструментов, поддерживаемые AccelDSP Synthesis Tool для алгоритмического синтеза, ориентированного на ПЛИС Xilinx.)

Скачать

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

Viktor2312- RIP

- Сообщения : 15492

Дата регистрации : 2012-08-10

Возраст : 45

Откуда : Пятигорск

.

.

15

Изучение. VHDL.

Введение.

Введение.

Современные языки проектирования цифровых устройств.